- •1) Архитектура фон Неймана

- •2) Понятие информационных систем, систем обработки данных, вычислительных систем.

- •3) Функционирование эвм. Процесс и поток.

- •Функционирование эвм. Процесс и поток.

- •Процессы и потоки

- •4) Классификация элементов памяти. Физические принципы построения.

- •5) Матричная организация элементов памяти.

- •6) Кэширование памяти

- •7)Архитектура кэш-памяти

- •8) Исполнение программного кода. Переключение задач и виртуальные машины. Защищенный режим и виртуальная память

- •9) Архитектура и микроархитектура процессоров. Конвейеризация.

- •10) Режимы работы процессоров

- •11) Архитектурные регистры и типы данных

- •12) Набор инструкций. События - прерывания и исключения.

- •13) Эффективный адрес и преобразование адресов.

- •14) Страничная трансляция адресов и виртуальная память

- •15) Мультипроцессорные и избыточные системы

- •16) Информационная магистраль первого поколения - шина isa

- •17) Информационная магистраль второго поколения - шина pci

- •18) Информационная магистраль третьего поколения - шина pci-Express

- •19) Принципы магнитной записи и физическое устройство жесткого диска

- •20) Системная организация hdd. Интерфейсы устройств хранения

- •21) Raid-массивы

- •22) Логическая структура дисков. Файловая система

- •24) Видеосистема

- •25) Представление различных видов информации в компьютере

- •28) Способы организации многомашинных вычислительных систем

- •29) Модель системы передачи данных. (точка-точка и многоточечные соединения)

- •30) Способы передачи данных в сетях. Синхронизация передачи данных.

- •31) Средства организации удаленного взаимодействия. Структура сетей со средствами коммутации. Коммуникационный порт.

- •32) Общее описание процесса обмена данными в сети

- •33) Физическая и логическая топология сети

- •34) Архитектуры сетей

- •35) Локальные и глобальные сети

- •36)Семиуровневая модель взаимодействия открытых систем osi

- •Структура модели osi. Функции уровней.

- •37) Функции канального уровня. Контроль ошибок и взаимодействие канальных уровней

- •38) Протоколы ieee канального уровня

- •39) Основные функции сетевого уровня. Протокол х.25

- •40) Протокол ip

- •41) Общая характеристика транспортных протоколов. Протокол tcp

- •42) Протокол udp. Стандартные стеки коммуникационных протоколов.

6) Кэширование памяти

Кэш (англ. cache, от фр. cacher — «прятать»; произносится [kæʃ] — «кэш») — промежуточный буфер с быстрым доступом, содержащий информацию, которая может быть запрошена с наибольшей вероятностью. Доступ к данным в кэше идёт быстрее, чем выборка исходных данных из оперативной (ОЗУ) и быстрее внешней (жёсткий диск или твердотельный накопитель) памяти, за счёт чего уменьшается среднее время доступа и увеличивается общая производительность компьютерной системы.

Кэш-память представляет собой статическое ОЗУ, обладающее значительно более высоким быстродействием, нежели динамическое. Фактически, кэш-память предназначена для согласования (компенсации) скорости работы сравнительно медленных устройств с относительно быстрым центральным процессором, т.е. она играет роль быстродействующего буфера между процессором и относительно медленной динамической памятью.При попытке доступа к данным процессор сначала обращается к внутренней кэш-памяти, если их там нет, то ко внешней, лишь затем к основной динамической памяти.Когда процессор первый раз обращается к ячейке памяти, ее содержимое параллельно копируется в кэш, и в случае повторного обращения может быть с гораздо большей скоростью выбрано из кэша.

7)Архитектура кэш-памяти

Кэш центрального процессора разделён на несколько уровней. В универсальном процессоре в настоящее время число уровней может достигать 3. Кэш-память уровня N+1 как правило больше по размеру и медленнее по скорости доступа и передаче данных, чем кэш-память уровня N.

Самой быстрой памятью является кэш первого уровня — L1-cache. По сути, она является неотъемлемой частью процессора, поскольку расположена на одном с ним кристалле и входит в состав функциональных блоков. В современных процессорах обычно кэш L1 разделен на два кэша, кэш команд (инструкций) и кэш данных.

Вторым по быстродействию является L2-cache — кэш второго уровня, обычно он расположен на кристалле, как и L1. В старых процессорах — набор микросхем на системной плате. Объём L2 кэша от 128 Кбайт до 1−12 Мбайт. В современных многоядерных процессорах кэш второго уровня, находясь на том же кристалле, является памятью раздельного пользования — при общем объёме кэша в nM Мбайт на каждое ядро приходится по nM/nC Мбайта, где nC количество ядер процессора. Обычно латентность L2 кэша, расположенного на кристалле ядра, составляет от 8 до 20 тактов ядра.

Кэш третьего уровня наименее быстродействующий, но он может быть очень внушительного размера — более 24 Мбайт. L3 кэш медленнее предыдущих кэшей, но всё равно значительно быстрее, чем оперативная память. В многопроцессорных системах находится в общем пользовании и предназначен для синхронизации данных различных L2.

8) Исполнение программного кода. Переключение задач и виртуальные машины. Защищенный режим и виртуальная память

Программный код — это последовательность команд, или инструкций, каждая из которых определенным образом закодирована и расположена в целом числе смежных байтов памяти. Каждая инструкция обязательно имеет операционную часть, несущую процессору информацию о требуемых действиях. Операндная часть, указывающая процессору, где находится его «предмет труда» — операнды, — может присутствовать в явном или неявном виде и даже отсутствовать. Операндная часть может описывать от нуля до двух операндов, участвующих в выполнении данной инструкции (есть инструкции, в которых, помимо двух операндов, задается еще и параметр инструкции). Здесь могут быть сами значения операндов (непосредственные операнды); явные или неявные указания на регистры процессора, в которых находятся операнды; адрес (или его составная часть) ячейки памяти или порта ввода-вывода; регистры процессора, участвующие в формировании адреса, и разные комбинации этих компонентов. Инструкции могут предшествовать префиксы (к счастью, всегда однобайтные, но их может быть несколько), указывающие на изменение способа адресации, размера операнда или/и необходимость многократного (по счетчику и условию) повторения для данной инструкции. Адрес (логический) текущей исполняемой инструкции хранится в специальном регистре — указателе инструкций (Instruction Pointer, IP), который соответствует счетчику команд фон-неймановской машины. После исполнения так называемой линейной инструкции этот указатель увеличивает свое значение на ее длину, то есть указывает на начало следующей инструкции. Линейная инструкция не нарушает порядок выполнения инструкций, определяемый последовательностью их расположения в памяти (по нарастанию адреса). Помимо линейных инструкций существуют инструкции передачи управления, среди которых различают инструкции переходов и вызовов процедур. Эти инструкции в явном или неявном виде содержат информацию об адресе следующей выполняемой инструкции, который может указывать на относительно произвольную ячейку памяти. Инструкции переходов и вызовов могут быть безусловными (ни от чего не зависящими) и условными. Произойдет ли условный переход (вызов) или нет, зависит от состояния флагов (признаков) на момент исполнения данной инструкции. Если переход (вызов) не состоится, то исполняется инструкция, расположенная в памяти вслед за текущей. Вызов процедуры характерен тем, что перед ним процессор сохраняет в стеке (стек — это область ОЗУ) адрес следующей инструкции, и на этот адрес передается управление после завершения исполнения процедуры (этот адрес извлекается из стека при выполнении инструкции возврата). Переход выполняется безвозвратно.

Последовательность исполнения инструкций, предписанная программным кодом, может быть нарушена под воздействием внутренних или внешних (относительно процессора) причин. К внутренним причинам относятся исключения (exceptions) — особые ситуации, возникающие при выполнении инструкций. Наглядным примером исключения является попытка деления на ноль. При возникновении условия исключения процессор автоматически выполняет вызов процедуры обработки исключения, после которой он может вернуться к повторному исполнению инструкции, породившей исключение, или следующей за ней. Вариант поведения зависит от типа произошедшего исключения. Исключения широко используются современными операционными системами. На основе обработки исключений строится система виртуальной памяти и реализуются многие функции многозадачных операционных систем. Внешними причинами изменения нормальной последовательности инструкций являются аппаратные прерывания — вызовы процедур под воздействием электрических сигналов на специальные выводы процессора или по получении сообщения по специальному интерфейсу контроллера прерываний. Эти сигналы могут подаваться совершенно неожиданно для исполняемой программы; правда, у программиста есть возможность заставить процессор (компьютер) игнорировать все прерывания или их часть. Злоупотреблять этой возможностью нельзя (да и не всегда она есть), поскольку на аппаратных прерываниях строится, например, отсчет времени и другие системные и прикладные функции компьютера. Источниками аппаратных прерываний являются контроллеры и адаптеры периферийных устройств, генераторы меток времени, системы управления питанием и другие подсистемы. Есть еще так называемые программные прерывания, но они отнюдь не нарушают последовательность инструкций, предписанную программистом. Поэтому прерываниями они по сути не являются — это всего лишь особый способ вызова системных сервисов BIOS и операционной системы. И наконец, последовательность инструкций может изменяться по сигналу аппаратного сброса или инициализации процессора. С этого, собственно, и начинается функционирование компьютера: процессор переводится в исходное состояние и «запускается». При этом указатель инструкций совместно с другими регистрами, участвующими в формировании адреса инструкции, генерирует адрес, на 15 байт меньший максимального физического адреса. По этому адресу должна располагаться инструкция, с которой начинается инициализация компьютера.

Прерывания используют и для переключения задач в многозадачных системах. Пусть, например, имеются два потока инструкций (например, две прикладные программы), которые должны выполняться как бы одновременно (по-настоя- щему одновременно один фон-неймановский процессор их выполнить не может). Можно запустить один поток, а через некоторое время его работы при аппаратном прерывани (от таймера) сохранить в памяти образ его текущего состояния (все регистры, программно-доступные этому процессу) и запустить другой поток. Через некоторое время при следующем прерывании выполнить обратное переключение: сохранить состояние второго потока (в другом месте памяти), загрузить в регистры процессора образ состояния первого потока и продолжить его выполнение. Эти переключения задач следует выполнять в течение исполнения обоих программ с частотой, создающей у пользователя иллюзию непрерывности и одновременности. Понятно, что ресурсы процессора (производительность) в этом случае делятся между задачами пропорционально выделяемым им квантам времени. Чтобы пользователя такая производительность процессов удовлетворяла (а еще учтем накладные расходы на сохранение и восстановление образов при переключениях), у процессора должна быть достаточная мощность. Процессоры семейства х86, начиная со второго и особенно с третьего (386) поколения, имеют встроенные средства поддержки многозадачности (число задач почти не ограничено), работающие в защищенном режиме. Переключение задач производится по сигналу прерывания от таймера совершенно «прозрачно» для процессов, работающих псевдопараллельно. Благодаря этой прозрачности программисту, разрабатывающему прикладную программу, в большинстве случаев не надо заботиться об обеспечении многозадачности. В распоряжение его программы предоставляется виртуальная машина (тоже фон-неймановская), в которой управление передается последовательно этой программой, как будто она — единственная. Конечно, поддержка виртуальных машин требует определенных усилий со стороны многозадачной операционной системы, которой приходится распределять не только процессорное время, но и память, устройства хранения, ввода-вывода и коммуникационные устройства — то есть все ресурсы реального компьютера. В этом ей помогают специальные средства, введенные в процессоры х86 2-3-го поколений и постоянно развиваемые в следующих поколениях.

Широко известно, что первым микропроцессором, на базе которого была создана IBM PC, был Intel 8088. Этот микропроцессор отличался от первого 16-разрядного микропроцессора фирмы Intel -- 8086 -- прежде всего тем, что у него была 8-битовая шина данных, а не 16-битовая (как у 8086). Оба эти микропроцессора предназначались для создания вычислительных устройств, которые бы работали в однозадачном режиме, то есть специальных аппаратных средств для поддержки надежных и эффективных мультипрограммных ОС в них не было.

Однако к тому времени, когда разработчики осознали необходимость включения в микропроцессор специальной аппаратной поддержки для мультипрограммных вычислений, уже было создано очень много программных продуктов. Поэтому для совместимости с первыми компьютерами в последующих версиях микропроцессоров была реализована возможность использовать их в двух режимах -- реальном (real mode -- так назвали режим работы первых 16-битовых микропроцессоров) и защищенном (protected mode -- означает, что параллельные вычисления могут быть защищены аппаратно-программными механизмами).

Подробно рассматривать архитектуру первых 16-битовых микропроцессоров i8086/i8088 мы не будем, поскольку этот материал должен изучаться в предыдущих дисциплинах учебного плана. Для тех же, кто с ним не знаком, можно рекомендовать такие книги, как [52, 73], и многие другие. Однако напомним, что в этих микропроцессорах (а значит, и в остальных микропроцессорах семейства i80x86 при работе их в реальном режиме) обращение к памяти с возможным адресным пространством в 1 Мбайт осуществляется посредством механизма сегментной адресации (рис. 3.1). Этот механизм был использован для увеличения количества разрядов, участвующих в указании адреса ячейки памяти, с которой в данный момент осуществляется работа, с 16 до 20 и тем самым увеличения объема памяти.

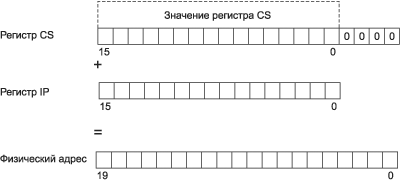

Конкретизируем задачу и ограничимся рассмотрением определения адреса команды. Для адресации операндов используется аналогичный механизм, только участвуют в этом случае другие сегментные регистры. Напомним, что для определения физического адреса команды содержимое сегментного регистра CS (code segment) умножается на 16 за счет добавления справа (к младшим битам) четырех нулей, после чего к полученному значению прибавляется содержимое указателя команд (регистр IP, instruction pointer). Получается двадцатибитовое значение, которое и позволяет указать любой байт из 220.

В защищенном режиме работы определение физического адреса осуществляется совершенно иначе. Прежде всего используется сегментный механизм для организации виртуальной памяти. При этом адреса задаются 32-битовыми значениями. Кроме этого, возможна страничная трансляция адресов, также с 32-битовыми значениями. Наконец, при работе в защищенном режиме, который по умолчанию предполагает 32-битовый код, возможно исполнение двоичных программ, созданных для работы микропроцессора в 16-битовом режиме. Для этого введен режим виртуальной 16-битовой машины и 20-битовые адреса реального режима транслируются с помощью страничного механизма в 32-битовые значения защищенного режима. Наконец, есть еще один режим -- 16-битовый защищенный, позволяющий 32-битовым микропроцессорам выполнять защищенный 16-битовый код, который был характерен для микропроцессора 80286. Правда, следует отметить, что это последний режим практически не используется, поскольку программ, созданных для него, не так уж и много.

Для изучения этих возможностей рассмотрим сначала новые архитектурные возможности микропроцессоров i80x86.