- •Дисциплина: «микропроцессоры и микропроцессорные системы»

- •Отличительные особенности поколений процессоров. Микропроцессоры: определение, назначение, классификация и параметры. Поколения процессоров.

- •2. Системы эвм.

- •3.Обобщенная структурная схема микропроцессора.

- •4. Типичный машинный цикл. Пути обработки командного слова.

- •5. Типичный машинный цикл. Пути обработки информационного слова.

- •6. Запоминающие устройства: назначение, классификация, параметры.

- •7.Элементы и модули статических и динамических зу: режимы работы.

- •8. Постоянные и перепрограммируемые зу. Элементы перепрограммирования.

- •10. Организация подсистемы прерываний микропроцессорной системы. Классы прерываний. Структура контроллера прерываний. Процедура обслуживания прерывания.

- •11. Организация режима прямого доступа в память. Контроллер пдп.

- •12. Организация службы времени. Программируемый таймер.

- •13. Контроллер видеотерминала. Структурная схема.

- •14. Схема включения контроллера видеотерминала в мпс.

- •15. Особенности архитектуры микропроцессоров Intel 80486 и Pentium. Структурная схема.

- •16. Эволюция архитектуры микропроцессоров. Конвейерная обработка команд.

- •17. Семейства микро-эвм. Ключевые микросхемы пк ibm pc и совместимых с ними.

- •18. Многомашинные вычислительные системы. Структурная схема.

- •19. Многопроцессорные вычислительные системы. Структурная схема.

- •20. Микроконтроллеры avr: система команд.

- •21. Интегрированная среда разработки программного обеспечения (ис рпо) для семейства мк avr. Компиляция, компоновка, отладка.

- •22. Программирование микроконтроллера на языке Assembler (asm): процедуры, подпрограммы, директивы.

- •23. Взаимодействие мк с объектами управления.

- •24. Программируемые логические матрицы. Программируемая матричная логика. Стратегия и этапы проектирования.

- •Дисциплина: «конструирование, производство и эксплуатация средств вычислительной техники»

- •25. Жизненный цикл технической системы. Структура жизненного цикла. Компьютерное сопровождение процессов жизненного цикла изделий – кспи.

- •26. Комплекс работ по созданию новой техники. Этапы проектирования.

- •27. Модульный принцип конструирования. Уровни конструктивных модулей свт. Электрические соединения в конструкциях эвм. Конструкторская, технологическая и нормативно-техническая документация.

- •28. Единая система конструкторской документации – ескд. Виды конструкторской документации.

- •29. Единая система технологической документации – естд. Виды технологической документации.

- •30. Конструирование печатных плат. Гост'ы на печатные платы. Типы печатных плат: опп, дпп, мпп, гпп.

- •31. Классы точности печатных плат (отечественные и зарубежные). Размеры печатных плат. Маркировка печатных плат.

- •32. Обеспечение помехоустойчивости в конструкциях свт. Причины возникновения помех.

- •34. Принципы конструирования печатных плат: моносхемный, схемно-узловой, каскадно-узловой, функционально-узловой.

- •35. Системы автоматизированного проектирования (сапр). Структура сапр. Виды обеспечения (подсистемы) сапр.

- •36. Комплексы технических средств сапр. Основные требования к информационным системам; базы данных (бд), субд.

- •37. Классификация по сапр. Системы проектирования электрических схем.

- •38. Системы проектирования печатных плат.

- •39. Компьютерные чертёжно-графические системы для разработки конструкторской документации аппаратно-программных систем.

- •40. Производственный процесс: типы; основные характеристики; составные части; производственного процесса. Изделия: виды изделий.

- •41. Стадии производственных процессов. Технологическое оборудование, приспособления и оснастка. Типы производства: единичное, серийное, массовое.

- •42. Виды технологических процессов. Исходные данные для разработки тп. Основные принципы организации тп

- •43. Материалы, переменяемые для изготовления печатных плат. Фольгированные и нефольгированные диэлектрики; стеклотекстолит. Изготовление оригиналов и фотошаблонов.

- •44. Технологические процессы изготовления пп: субтрактивные, аддитивные.

- •46. Типовая структура тп изготовления тэз'ов. Сборочные процессы в производстве свт: установка корпусных навесных элементов на платы. Компоновка тэз'ов.

- •47. Выходной контроль собранной системы. Регулировка. Испытания.

- •48. Надёжность. Критерии надёжности. Культура производства. Субъективные и объективные эксплуатационные факторы. Способы повышения надёжности.

- •49. Автоматизация производства свт: сапр, астпп, гпс. Промышленные работы.

- •50. Техническое обслуживание; контроль и диагностика свт. Виды неисправностей свт и способы их устранения.

- •Дисциплина: «операционные системы и среды»

- •51. Понятие процесс. Состояние процессов. Контекст и дескриптор процесса.

- •52. Алгоритмы планирования процессов. Алгоритмы основанные на квантовании. Алгоритмы основанные на приоритетах.

- •53. Абсолютные и относительные приоритеты. Вытесняющие и невытесняющие алгоритмы планирования.

- •54. Задача по управлению файлами и устройствами. Организация параллельной работы устройств ввода-вывода и процессора. Согласование скоростей обмена и кэширование данных.

- •55. Управление реальной памятью. Функции ос по управлению реальной памятью. Типы адресов.

- •56. Файловая система. Цели и задачи файловой системы. Каталоги.

- •57. Иерархическая структура файловой системы. Атрибуты файлов

- •58. Типы файлов. Имена файлов.

- •59. Виды интерфейсов пользователя ос unix.Графический, командный и программный интерфейс.

- •60. Типы файлов ос unix. Генерация имен файлов. Структура каталогов ос unix.

- •61. Основные каталоги в корне системы. Их название и назначение.

- •62. Управление правами доступа к файлам и каталогам в ос unix. Категории пользователей в системе. Изменение прав доступа файла/каталога.

- •63. Создание и редактирование текстовых файлов. Выход из текстового редактора. Команды режима ввода текста. Команды удаления текста.

- •64. Создание и редактирование текстовых файлов. Выход из текстового редактора. Команды отмены. Команды копирования.

- •65. Команды поиска файлов в ос linux. Основные команды поиска, различия между ними. Основные флаги команд поиска.

- •Дисциплина: «компьютерные сети и телекоммуникации»

- •65.Определение локальной сети. Сетевой сервис. Классификация сетей. Типы серверов.

- •Базовые сетевые топологии: полносвязные, неполносвязные (шинная, звездообразная, кольцевая, иерархическая).

- •Стандарты кабелей. Виды кабелей: коаксиал, витая пара, волоконно– оптические.

- •Методы передачи дискретных данных: аналоговая модуляция, цифровое кодирование.

- •Модель взаимодействия открытых систем osi. Понятие многоуровнего подхода. Функции уровней модели osi.

- •Технология Ethernet (ieee 802.3). Метод доступа csma/cd. Этапы доступа к среде. Возникновение коллизий.

- •Технология Ethernet (ieee 802.3). Форматы кадров технологии Ethernet.

- •Технология TokenRing (ieee 802.5). Основные характеристики. Маркерный доступ к разделяемой среде.

- •Технология TokenRing (ieee 802.5). Форматы кадров TokenRing. Физический уровень технологии TokenRing.

- •Технология fddi. Основные характеристики. Особенности метода доступа. Отказоустойчивость технологии. Физический уровень технологии fddi.

- •Сетевое оборудование: сетевые адаптеры. Функции и характеристики сетевых адаптеров. Классификация.

- •Сетевое оборудование: концентраторы и коммутаторы. Основные и дополнительные функции. Конструктивное исполнение. Принцип работы. Основное отличие концентраторов от коммутаторов.

- •Сетевое оборудование: мосты. Принцип работы мостов. Логическая структуризация сети с помощью мостов и коммутаторов.

- •Сетевое оборудование: маршрутизатор. Функции маршрутизатора. Протоколы маршрутизации.

- •Глобальные связи на основе выделенных линий. Аналоговые и цифровые выделенные линии. Модемы для работы на выделенных линиях.

- •Глобальные связи на основе сетей с коммутацией каналов. Аналоговые телефонные сети. Модемы для работы на коммутируемых аналоговых линиях.

- •Структурированная кабельная система /скс/. Иерархия в кабельной системе. Выбор типа кабелей для различных подсистем.

- •Линии связи. Аппаратура линий связи. Характеристики линий связи.

- •Дисциплина: «периферийные устройства вычислительной техники»

- •Определение, состав и назначение системной платы в составе пк.

- •Ide(дисководы, старые харды) и разъем бп

- •Bios, определение, назначение и основные функции.

- •Блок питания. Определение, назначение. Форм-фактор at. Основные технические параметры блока питанияAt.

- •Блок питания. Определение, назначение. Форм-фактор atx. Основные технические параметры блока питанияAtx.

- •Жесткий диск. Определение, назначение. Состав основных узлов. Основные технические параметры жесткого диска.

- •Определение, назначение, состав основных узлов дисковода гибких дисков. Принцип работы гибких дисков.

- •Конструкция дискеты. Логическая структура гибкого диска.

- •Определение, назначение, разновидности приводов cd-rom. Основные технические параметры приводов cd-rom.

- •Принцип действия монитора на основе элт. Основные технические параметры мониторов на основе элт.

- •Принцип действия жк монитора. Основные технические параметры жк монитора.

- •Назначение и принцип действия видеоадаптера.

- •Назначение и принцип звуковой карты.Основные технические параметры звуковой карты.

- •Функциональная схема видеоадаптера. Основные технические параметры видеоадаптеров.

- •Классификация принтеров.

- •Принцип действия струйного принтера.

- •Принцип действия лазерного принтера.

- •Принцип действия струйного плоттера.

- •Классификация сканеров, принцип действия планшетного сканера.

- •1. Ручные – в магазах штрих коды считывает

- •Классификация цифровых фотокамер. Принцип действия цифровой фотокамеры. Основные технические параметры цифровой фотокамеры.

- •Функциональная схема цифровой фотокамеры.

- •Назначение, принцип действия мыши. Основные технические параметры клавиатуры.

- •Назначение, принцип действия клавиатуры. Основные технические параметры клавиатуры.

- •Дисциплина: «программирование на языке высокого уровня»

- •Понятие алгоритма. Методы описания алгоритма.

- •107. Основные алгоритмические конструкции: линейный алгоритм, разветвляющийся, циклический.

- •Базовые алгоритмические структуры

- •Разветвляющиеся вычислительные процессы в языках высокого уровня (Pascalили си): ветвление и множественный выбор.

- •109. Организация циклических процессов в языках высокого уровня (си или Pascal). Три типа операторов цикла.

- •Алгоритм сортировки массивов. Метод установки.

- •111. Алгоритмы сортировки массивов. Метод пузырька.

- •Матрица. Ввод и вывод элементов матрицы.

- •113.Определение индексов элементов матрицы, расположенных на, над и под главной и побочной диагональю.

- •Представление символьных и строковых данных в языках высокого уровня (си или Pascal). Объявление типа, описание переменных.

- •115. Операции над строковыми переменными.

- •Процедуры и функции пользователя в языках высокого уровня (си или Pascal). Описание и вызов процедур и функций. Формальные и фактические параметры, связь между ними.

- •117. Организация работы с файлами из программы (стандартные функции обработки файлов).

- •Ввод и вывод данных из файла (матрица и массив).

- •119. Стандартные функции ввода и вывода данных (си или Pascal).

- •120. Ввод и вывод элементов в одномерном массиве. Обращение к элементам массива при помощи индекса и при помощи указателя.

10. Организация подсистемы прерываний микропроцессорной системы. Классы прерываний. Структура контроллера прерываний. Процедура обслуживания прерывания.

В мультипроцессорных ВС вычисления выполняються по нескольким независимым программам. Для перехода от одной команды к другой и правильного взаимодействия ВС вводиться понятие прерывание программы

Прерывание программы – способность ЦВМ и ВС временно прекращать выполнение программы при возникновении определенных условий и передавать управление прерывающей прграмме.

Существует 5 основных классов прерываний:

программные прерывания - при обнаружении ошибок в программе или при получении особых результатов ( переполнение разрядной сетки, нулевой результат, потеря значимости мантиссы или порядка )

обращение к ОСпредусмотрено в случаях выполнения каких либо действий по управлению ЦВМ и ВС

от устройств вода вывода - Направлено на обеспечение процессором запросов на прерывание

От схем контроляВозникает при обнаружении сбоев, неисправностей. При этом происходит переключение на диагностические программы.

Внешние прерывания происходят при обращении к данному процессору, другого процессора многопроцессорной системы.

Запросы от ВУ через входы ЗП(0-7) запоминаются в регистре запросов. Регистр состояния, каждый разряд которого соответствует одному из входов ЗП(0-7) содержит все запросы на прерывания, обслуживаемые в текущий момент.

Регистр маски содержит 1 в разрядах, соответствующим маскируемым в данный момент входам запросов.

Запросы на прерывания по каждому входу могут быть переданы в потенциальной или импульсной форме, однако каждый последующий запрос на прерывание воспринимается контроллером только после подпрограммы обслуживания текущего запроса по данному входу и сброса соответствующего разряда регистра состояний, что осуществляется программным способом - специальной командой. Установка в 1 того или иного разряда регистра маски блокирует передачу запроса на прерывание, если через некоторое время после подачи сигнала маска будет снята, запрос будет обслужен.

11. Организация режима прямого доступа в память. Контроллер пдп.

Контроллер предназначен для непосредственного обмена информацией между ЗУ и ВУ используется режим ПДП. Его инициализация осуществляется подачей асинхронного сигнала ЗХ, поступающей на МП от ВУ, приэто МП устанавливает свои выходы адресов и данных в состояние Z, выдает сигнал ПЗХ, завершает выполнение внутренних операций текущего цикла и переходит в состояние ТОЖЗХ. Выход из ПДП - в обратном порядке.

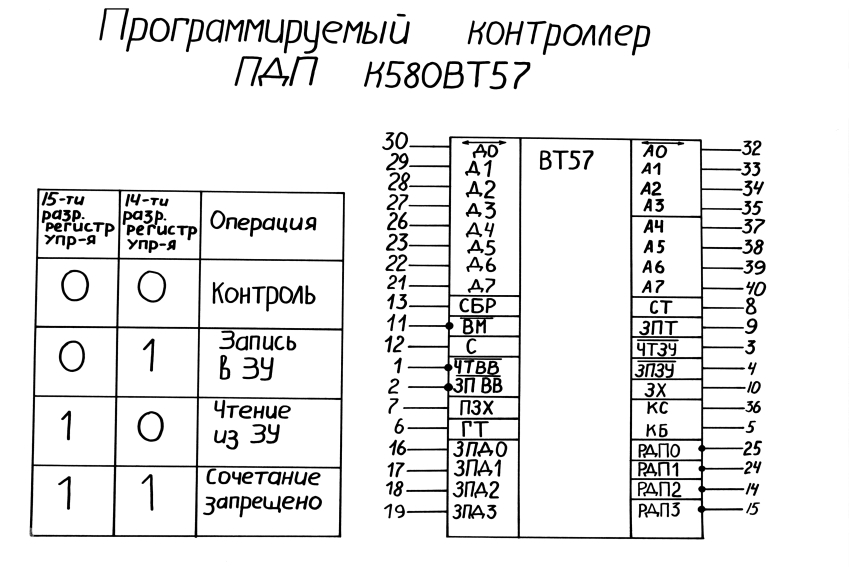

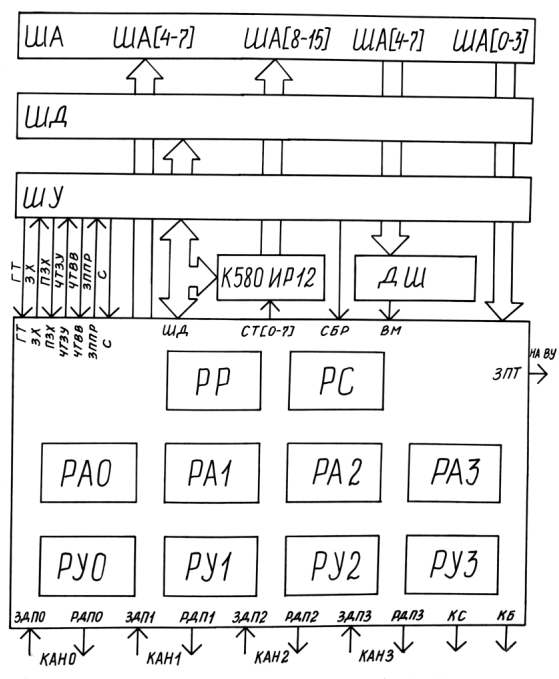

БИС КР580ВТ57 предназначен для управления передачей информации между ВУ и ЗУ в режиме ПДП. Основное назначение контроллера – формировать в процессе обмена последовательность адресов ЗУ, а также сигналы управления обменом и процессом предоставления ПДП.

БИС размещена в пластиковом корпусе с 40 выводами. Потребляемая мощность 250мВт, напряжение питания 5В.

Контроллер ПДП имеет 4 независимых канала обмена. Блок управления каждого из каналов включает два 16-разрядных регистра: начального адреса РА, в который заносится начальный адрес ЗУ для передаваемого массива данных и регистра управления РУ, в 14 младших разрядах которого помещается число, указывающее длину передаваемого массива. Т.о. при такой организации работы контроллера длина массива=16кб. Два старших разряда РУ определяют тип операции обмена.

При

выполнении операции контроля блок

управления каналом формирует все

сигналы, обычно вырабатываемые при

передаче массива, за исключением

чтения/записи информации в ВУ или ЗУ: ,

следовательно передача информации не

происходит, МП отключается от шин

системы, контроллер выдает сигнал

разрешения ПДП (

,

следовательно передача информации не

происходит, МП отключается от шин

системы, контроллер выдает сигнал

разрешения ПДП ( )

на ВУ.

)

на ВУ.

м.б. использован ПУ-вом для начала подсчета контрольной суммы для разрешения внутреннего доступа только что прочитанных из ЗУ данных.

Записи информации в РА и РУ каналов(0-3) происходит при помощи команд IN и OUT и осуществляется МП-ром. Возможна организации МПС, в которых обращение к БИС ВТ57 производится как к ячейке памяти.

ВТ57 использует для управления регистрами адреса и управления две команды: команда занесения в МП младшего байта, а затем старшего байта.

Чтобы разрешить работу одного или нескольких каналов прямого доступа после занесения требуемой информации в РА и РУ, необходимо записать в 8-разрядный РГРЖ (на схеме видимо РР) управляющее слово.