- •1. По виду архитектуры

- •Принципы построения современных контроллеров.

- •Прерывания в микропроцессорных системах

- •Прерывания

- •Таймеры-счетчики микроконтроллеров

- •Параллельные порты ввода/вывода микроконтроллеров avr

- •Аналого-цифровое преобразование в мк avr

- •Простейший цап

- •Простейшие исполнительные устройства в мпт

- •Подключение матричной клавиатуры

- •Подключение матричной клавиатуры с использованием дешифратора

- •Динамический режим индикации

- •Особенности последовательного обмена данными

Особенности последовательного обмена данными

Универсальный асинхронный приемопередатчик (UART) МК AVR

Для приема и передачи данных в асинхронном последовательном формате, как это показано на рисунке 2, AVR-микроконтроллеры содержат универсальный асинхронный приемопередатчик (Universal Asynchronous Receiver and Transmitter - UART). Также этот периферийный узел называют адаптером последовательного канала. Отличительными особенностями его работы являются:

Наличие программно управляемого тактового генератора, специализированного только для обслуживания UART, обеспечивающего большой набор тактовых частот и возможность передачи данных на высоких частотах даже при низкой системной тактовой частоте;

Способность работы в дуплексном режиме (одновременная передача и прием данных);

Возможность передавать как 8-и, так и 9-битные данные;

Фильтрация помех на входе путем многократного опроса каждого бита;

Аппаратная фиксация ошибок переполнения и кадрирования (ложный стоп-бит) при приеме данных;

Формирование трех различных прерываний с индивидуальными адресами векторов прерывания: при завершении передачи (TX Complete), при завершении приема (RX Complete) и при освобождении регистра данных передатчика (TX Data Register Empty).

Управление приемопередатчиком осуществляется посредством двух регистров: регистра статуса USR и регистра управления UCR. Регистр статуса USR доступен только по чтению и обеспечивает информацию о состоянии UART. Регистр управления UCR предназначен для задания режимов работы UART и доступен как по чтению, так и по записи.

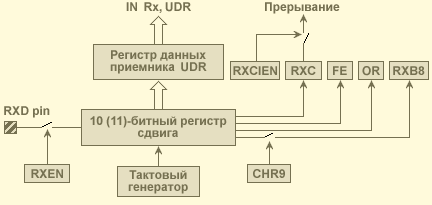

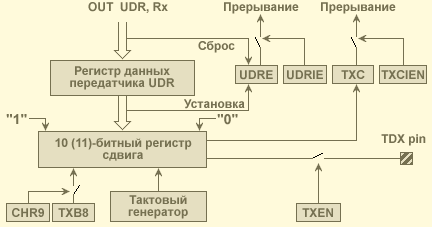

На рисунках 5 и 6 изображены программные модели приемника и передатчика UART соответственно.

Рисунок 5. Программная модель приемника UART

Рисунок 6. Программная модель передатчика

Установка бит управления TXEN=1 (Transmitter Enable) и RXEN=1 (Receiver Enable) в регистре управления UCR разрешает соответственно передачу и прием данных по последовательному каналу. При этом выход передатчика и вход приемника соединяются с внешними выводами TXD и RXD AVR-микроконтроллера и настраиваются соответственно на выход и на вход независимо от установки бит в регистре направления данных порта DDRx. При сбросе TXEN и RXEN выводы TXD и RXD могут использоваться как обычные цифровые входы/выходы.

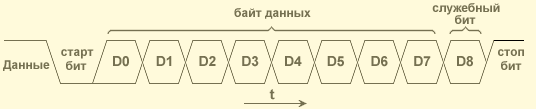

Формат асинхронной передачи (Рисунок 2) позволяет после 8 бит данных передавать один служебный бит, который, например, может быть битом четности или дополнительным стоп-битом. В AVR-микроконтроллерах такой режим 9-битного обмена задается одновременно и для передачи, и для приема данных установкой бита СНR9=1 в регистре управления UCR.

Передатчик и приемник UART содержат по одному буферному регистру данных UDR (UART Data Register) (рисунок 5, рисунок 6). Регистр данных приемника UDR и регистр данных передатчика UDR - это два физически раздельных регистра, имеющих один адрес в адресном пространстве регистров ввода/вывода. Процессор определяет, к какому физическому регистру осуществлять обращение по типу выполняемой операции. При выводе (команда OUT UDR, Rx) данные записываются в регистр данных передатчика UDR, а при считывании (команда IN Rx, UDR) выборка осуществляется из регистра данных приемника.

Передача в последовательный канал инициируется записью байта в регистр данных передатчика UDR (рисунок 6). Все остальные операции по преобразованию данных из параллельной формы в последовательную и формированию кадра передачи байта берет на себя передатчик UART. Он переписывает данные из регистра UDR в регистр сдвига передатчика, где к ним автоматически добавляются старт-бит, стоп-бит и, если установлен режим 9-битной передачи, бит TXB8 из регистра UCR.

Если в момент записи UDR регистр сдвига уже освободился от передачи предыдущего байта, то данные переписываются из UDR в регистр сдвига немедленно. В противном случае перепись осуществляется лишь после того, как стоп-бит передаваемого в настоящий момент байта появится на выводе TXD.

Когда данные посылаются в регистр сдвига из UDR, устанавливается бит UDRE (UART Data Register Empty) в регистре статуса USR (UART Status Register), что означает, что UART готов получить от процессора новый байт. Когда процессор записывает очередной байт в регистр данных UDR, флаг UDRE автоматически сбрасывается. Если же новые данные не будут записаны в UDR к тому времени, как закончится передача текущего байта из регистра сдвига, то дополнительно к установленному флагу UDRE устанавливается флаг окончания передачи TXC (TX Complete Flag) в регистре USR.

Приемник UART выполняет операции по преобразованию входных данных из последовательной формы в параллельную. Он производит предварительную выборку сигнала на входе RXD с частотой, в 16 раз большей скорости обмена (рисунок 7).

Рисунок 7. Выборки входного сигнала

Когда линия последовательной передачи свободна (данные не передаются), она находится в состоянии логической "1". Выборка приемником логического "0" после того, как линия была свободна, интерпретируется как срез старт-бита и инициирует последовательность определения старт-бита. Приемник, считая от первой нулевой выборки, анализирует 8-ю, 9-ю и 10-ю выборки. При обнаружении двух или более логических "1" в этих трех выборках старт-бит воспринимается как импульсная помеха, и приемник начинает следить за следующим перепадом "1/0".

Если старт-бит фиксируется, то затем осуществляется распознавание бит данных, причем для каждого бита также анализируются три значения входного сигнала в выборках 8, 9 и 10, считая от начала бита. За истинное значение бита принимается логическое значение, которое появилось хотя бы в двух выборках. Такие значения, полученные в результате голосования, последовательно посылаются в регистр сдвига приемника.

При поступлении стоп-бита результатом голосования трех выборок должна быть логическая "1". Если обнаружены хотя бы два логических "0", устанавливается флаг ошибки кадрирования FE (Framing Error) в регистре USR. Независимо от того, выявлен или нет стоп-бит в конце цикла приема байта, данные посылаются в регистр данных приемника UDR и устанавливается флаг завершения приема RXC (Receive Complete) в регистре USR.

Если установлен 9-битный режим обмена, 9-й бит регистра сдвига приемника загружается в бит RXB8 регистра UCR.

Если символ принят регистром сдвига, а предыдущая посылка еще не считана из регистра данных приемника UDR, то устанавливается флаг переполнения OR (OverRun) в регистре USR. Это означает, что последний байт данных, принятый регистром сдвига, не мог быть передан в регистр данных приемника UDR и был потерян. Для выявления ошибок переполнения, которые могут возникать при высоких частотах передачи или при большой загрузке процессора, бит OR следует опрашивать после считывания регистра UDR. При этом состояние бита OR=0 будет говорить, что между последними двумя байтами, считанными из UDR, не было потерь информации. Напротив, состояние бита OR=1 информирует процессор о том, что между последним и предпоследним байтами, считанными из UDR, были безвозвратно потеряны один или более байт. Обработкой такой ситуации может быть, например, запрос на повторную передачу утерянных данных. После того, как в регистр UDR успешно запишутся подряд два байта, бит OR снова сбросится.

Для тактирования приемопередатчика UART AVR-микроконтроллеры содержат специализированный программно управляемый тактовый генератор, который является делителем системной тактовой частоты и задает скорость обмена в соответствии со следующим уравнением:

![]() ,

,

где BAUD – скорость

обмена, бод;

![]() -

частота тактового генератора

микроконтроллера, МГц; UBRR

– содержание 8-битногодоступного для

записи регистра UBRR (0÷255).

-

частота тактового генератора

микроконтроллера, МГц; UBRR

– содержание 8-битногодоступного для

записи регистра UBRR (0÷255).

Таким образом, для задания скорости передачи или приема необходимо записать в регистр UBRR определенное числовое значение.

UART можно использовать успешно для организации обмена данными между двумя устройства, которые поддерживают протокол обмена RS-232. Например, COM-порт персонального компьютера и микропроцессорное устройство. Рассмотрим протокол RS-232 подробней.

Параметры физического уровня протокола RS-232

Рассмотрим параметры физического уровня протокола, которые определяют скорость обмена, метод кодирования информации и схему передачи[3].

В протоколе RS-232 принято двухуровневое кодирование сигнала. Все сигналы передаются специально выбранными уровнями, обеспечивающими высокую помехоустойчивость связи (рисунок 1). Отметим, что данные передаются в инверсном коде (логической единице соответствует низкий уровень, логическому нулю - высокий уровень).

|

Рисунок 1. Уровни сигналов RS-232 |

Такое кодирование позволяет достичь максимальной скорость передачи данных 115200 бит/с при длине соединительного провода 15 метров.

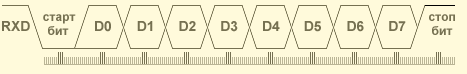

Формат передаваемых данных показан на рисунке 2. 5, 6, 7 или 8 бит данных сопровождаются стартовым битом, битом четности и одним или двумя стоповыми битами. Получив стартовый бит, приемник выбирает из линии биты данных через определенные интервалы времени.

Рисунок 2. Формат данных RS-232

Важно, чтобы тактовые частоты приемника и передатчика были одинаковыми, допустимое расхождение составляет не более 10%. Скорость передачи по RS-232C может выбираться из ряда: 110, 150, 300, 600, 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200 бит/с[4].

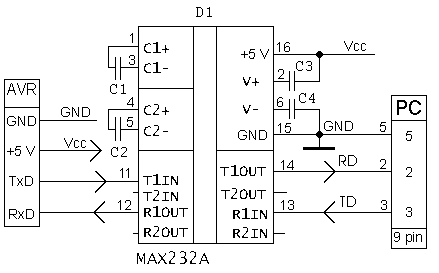

Отметим, что подключение микроконтроллера к персональному компьютеру по протоколу RS-232 напрямую не возможно, так как сигнал передается уровнями -3..-15 В (логическая «1») и +3..+15 В (логический «0»). Для преобразования уровней RS-232 в стандартные логические уровни TTL обычно используют специальные микросхемы преобразователей. Схема одного из возможных конвертеров уровней представлена на рисунке 3.

Рисунок 3. Схема конвертера уровней RS-232-TTL

Основу предлагаемого конвертера составляет широко распространенная микросхема преобразователей уровней MAX232A фирмы Maxim, которая имеет множество аналогов других производителей (Analog Devices, LG и другие). Данная микросхема рассчитана на напряжение питания 5В и имеет встроенные удвоитель и инвертор напряжений на переключаемых конденсаторах для получения напряжения ±10 В, необходимых для работы с сигналами стандарта RS-232. Для работы микросхемы требуется 4 внешних конденсатора (C1, C2, C3, C4) емкостью 0.1 мкФ, которые используются в преобразователе напряжения.

Использование такого конвертера удобно не только для организации обмена информацией между персональным компьютером и готовым внешним устройством, но и на этапе отладки проектируемого модуля, что позволяет во многих случаях обойтись без внутрисхемного отладчика[5].

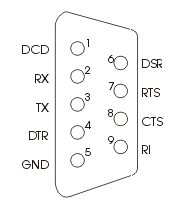

Схема разводки стандартного 9-ти штырькового разъема для подключения устройств через последовательный порт компьютера представлена на рисунке 4.

Рисунок 4. Схема разводки разъема

Назначение каждого из выводов сведено в таблице 1.

Таблица 1

Наименование |

Направление |

Описание |

DCD |

IN |

Carrier Detect (Определение несущей) |

RXD |

IN |

Receive Data (Принимаемые данные) |

TXD |

OUT |

Transmit Data (Передаваемые данные) |

DTR |

OUT |

Data Terminal Ready (Готовность терминала) |

GND |

-- |

System Ground (Корпус системы) |

DSR |

IN |

Data Set Ready (Готовность данных) |

RTS |

OUT |

Request to Send (Запрос на отправку) |

CTS |

IN |

Clear to Send (Готовность приема) |

RI |

IN |

Ring Indicator (Индикатор) |

Несмотря на то, что стандарт связи RS-232 был разработан более 35 лет назад, его до сих пор с успехом применяют в устройствах автоматики, в компьютерной технике и других приложения. Учитывая это, многие производители современных микроконтроллеров в набор средств периферии своих продуктов включают универсальный асинхронно-синхронный приемопередатчик.