- •Часть 2

- •Раздел 1 преобразовательные устройства и устройства электропитания

- •Выпрямители переменного тока

- •Классификация выпрямителей:

- •Параметры выпрямителей:

- •Однополупериодный выпрямитель

- •Двухполупериодный мостовой выпрямитель

- •Двухполупериодный выпрямитель с выводом средней точки вторичной обмотки трансформатора

- •Трехфазный выпрямитель с нейтральным выводом

- •Трехфазный мостовой выпрямитель

- •Сглаживающие фильтры

- •Емкостные фильтры

- •Индуктивные фильтры

- •Электронные фильтры

- •Стабилизаторы напряжения и тока

- •Параметрические стабилизаторы

- •Компенсационные стабилизаторы

- •Импульсные стабилизаторы постоянного напряжения

- •Управляемые выпрямители

- •Инверторы

- •Инверторы, ведомые сетью

- •Автономные инверторы

- •Автономный инвертор напряжения

- •Раздел 2 элементы импульсной и цифровой техники

- •2.1 Импульсный способ представления сигналов информации

- •Общая характеристика импульсных устройств

- •2.3 Простейшие формирователи импульсов

- •2.4 Бесконтактные логические элементы

- •Параметры логических схем

- •2.5 Триггеры Принципы построения триггеров

- •Асинхронные rs–триггеры

- •Синхронный rs-триггер

- •Несимметричный триггер с эмиттерной связью (триггер Шмитта)

- •Мультивибраторы

- •Автоколебательные мультивибраторы

- •Ждущий мультивибратор

- •2.8 Блокинг-генераторы

- •2.9 Генераторы линейно-изменяющегося напряжения (глин)

- •2.10 Цифроаналоговые и аналого-цифровые преобразователи

- •2.11 Дешифраторы и демультиплексоры

- •2.12 Мультиплексоры (multiplex – англ. Многократный)

- •2.13 Регистры

- •2.14 Цифровые счетчики импульсов

- •Двоичные счетчики

- •Работа счетчика

- •23 22 21 20 Вход у с к у с к у с к у с к t t t t d c b a

- •Раздел 3 микропроцессорная техника

- •3.1 Общие сведения о микропроцессорах и микропроцессорных системах Основные определения и классификация

- •Микропроцессорные средства в системах управления технологическими процессами

- •3.2 Арифметические и логические основы микропроцессорной техники Способы представления информации

- •Арифметические основы микропроцессорной техники

- •Логические основы микропроцессорной техники

- •3.3 Цифровые запоминающие устройства Типы запоминающих устройств

- •Оперативные запоминающие устройства

- •Постоянные запоминающие устройства

- •3.4 Архитектура и структура микропроцессорных систем и микропроцессора Архитектура микропроцессорных систем

- •Организация работы микропроцессорной системы

- •Архитектура микропроцессора

- •3.5 Интерфейс в микропроцессорных системах Общие сведения об интерфейсе

- •Способы обмена данными между устройствами мп-систем

- •3.6 Программирование микропроцессорных систем Общие сведения о командах

- •Система команд мп кр580ик80

- •Программирование и алгоритмические языки

- •Литература

- •Содержание

- •Раздел 1 преобразователи устройства и устройства электропитания...............................................................................................3

- •1.1 Выпрямители переменного тока….................................................................3

- •Раздел 2 элементы импульсной и цифровой техники…..35

- •Раздел 3 микропроцессорная техника…………………………..87

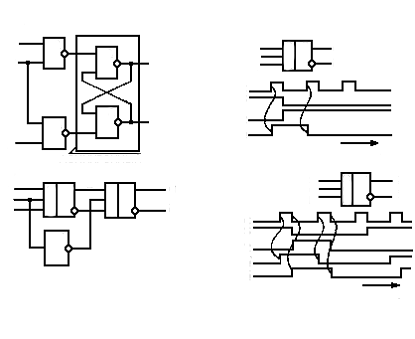

Синхронный rs-триггер

Простейшим представителем синхронных триггеров является одноступенчатый синхронный RS-триггер (рисунок 2.11). Данный триггер имеет статическое управление, т.е. при активном сигнале синхронизации прием информации («1») осуществляется в течение всего интервала времени, пока С = 1. Изменение сигналов S, R в течение этого интервала нежелательно. Если при С = 1, S = 1 и R = 0, то в триггер запишется единица.

Если при C = l, S = 0 и R = l, то в триггер запишется нуль. Комбинация сигналов S = R = 1 при С = 1 является запрещенной.

Рассмотренные триггеры со статическим управлением (рисунок 2.11, а) имеют одну ступень запоминания информации. В них прием (запись) и передача информации на выходы схемы происходит одновременно.

В результате во время записи информации возможно нарушение информационного состояния на выходах схемы. Чтобы этого избежать, используют двухступенчатые триггеры.

1

Q

R

C

S

Q'

T

R

C

S

R

C

S

Q'

R

CS

Q

R

C

T

S

R

SC

t

Q

R

CS

Q

R

C

R

C

S

S

T

&

&

Q

&

&

б

а

Асинхронный

RS-триггер

t

C

R

S

Рисунок 2.11 – Т-триггер на логических элементах И-НЕ

Двухступенчатый

синхронный RS-триггер

строится на базе двух последовательно

соединенных одноступенчатых синхронных

RS-триггеров

со специальной организацией цепи

синхронизации. При С

= 1 осуществляется прием

информации в

первый RS-триггер,

а при С

= 0 осуществляется

передача

информации из

первого триггера во второй и блокируются

информационные входы первого триггера.

Выходами

всей схемы являются выходы Q

и

второго триггера. Поэтому смена состояния

триггера для внешних схем происходит

в момент перехода синхросигнала из

единицы

в нуль (рисунок 2.11, б).

второго триггера. Поэтому смена состояния

триггера для внешних схем происходит

в момент перехода синхросигнала из

единицы

в нуль (рисунок 2.11, б).

D-триггер

Распространенным вариантом синхронного RS-триггера является D-триггер, схема которого приведена на рисунке 2.12, а.

Рисунок

2.12 – Схема (а), условное графическое

обозначение (б) и временные диаграммы

D-триггера

T

t

Q

D

C

Q

C

D

D

а

Синхронный

RS-триггер

1

&

&

Q

&

&

C

D

в

б

Она

получается из схемы синхронного

RS-триггера

(рисунок 2.12, а),

если на вход S

подать сигнал D,

а на вход R

– введением логического элемента НЕ.

Тактовые синхронизирующие импульсы С,

разрешающие переключение триггера в

строго фиксированные моменты времени

выполняют вместе с тем задержку передачи

входного сигнала. Временные диаграммы

работы D-триггера

приведены на рисунке 2.12, б.

введением логического элемента НЕ.

Тактовые синхронизирующие импульсы С,

разрешающие переключение триггера в

строго фиксированные моменты времени

выполняют вместе с тем задержку передачи

входного сигнала. Временные диаграммы

работы D-триггера

приведены на рисунке 2.12, б.

D-триггер со статическим управлением принимает информацию со входа D в течение всего интервала, пока С = 1 (активен). Изменение сигнала D в это время нежелательно. D-триггер с динамическим управлением принимает информацию со входа D в течение интервала (1 – 2) τЛЭ, вблизи фронта сигнала, т. е. можно считать, что триггер срабатывает в момент соответствующего фронта сигнала.

Триггер может быть построен с динамическим управлением, когда его переключение происходит в момент изменения управляющего сигнала от «0» к «1» (прямой динамический вход) или от «1» к «0» (инверсный динамический вход). На рисунке 2.12, б приведено условное обозначение D-триггера с прямым динамическим тактовым входом.

Можно создать D-триггер, используя только логические элементы И–НЕ (рисунок 2.13).

Рисунок

2.13 – D-триггер

на логических элементах И-НЕ

t1

t2

t

t

t

Q

0

Q

C

0

D

B

A

&

&

Q

&

DD1

&

DD3

∆t1

∆t2

0

0

t

C

D

Схема

D-триггера

содержит четыре логических элемента

И–НЕ.

Здесь элементы DD1

и DD2

образуют RS-триггер.

Дополнительные элементы DD3

и DD4

обращают его в D–триггер.

Работает триггер следующим образом.

Если D

= 1, то при наличии на входе С

тактового сигнала С

= 1 на выходе DD3

формируется сигнал, вид которого показан

на рисунке 2.13. Сигнал действует на

-триггер

подобно сигналу S,

и на выходе Q

устанавливается напряжение высокого

уровня (Q

= 1,

-триггер

подобно сигналу S,

и на выходе Q

устанавливается напряжение высокого

уровня (Q

= 1,

= 0).

В этом случае на выходе DD4

напряжение высокого уровня, поскольку

в отсутствие тактового импульса на

входе А

будет напряжение высокого и на входе В

–

низкого уровня. С приходом тактового

импульса (С

= 1) на входе А

возникает напряжение низкого, а входе

В –

высокого уровня.

= 0).

В этом случае на выходе DD4

напряжение высокого уровня, поскольку

в отсутствие тактового импульса на

входе А

будет напряжение высокого и на входе В

–

низкого уровня. С приходом тактового

импульса (С

= 1) на входе А

возникает напряжение низкого, а входе

В –

высокого уровня.

Если

на вход D

подано напряжение низкого уровня на

выходе DD3

будет напряжение высокого уровня, а

тактовый импульс (показан на рисунке

штрихами), инвертированный логическим

элементом DD4,

действует подобно сигналу

.

Вследствие этого триггер примет состояние

Q

= 0

и

=

l.

.

Вследствие этого триггер примет состояние

Q

= 0

и

=

l.

Т-триггер

Q

б

"0"

Q

T

C

Q

C

T

TT

C

T

Q

T

TT

&

C

T

а

T

TT

"0"

Q

T

T

Q

SCR

TT

T

t

t

Рисунок 2.14 – Схема, условные графические обозначения и временные диаграммы работы двухступенчатых Т-триггеров: а – асинхронного;

б – синхронного

Асинхронный Т-триггер может быть реализован на базе двухступенчатого D–триггера путем введения обратных связей, показанных на рисунке 2.14 а. Вход синхронизации С при этом преобразуется в счетный вход Т-триггера. Состояние такого триггера изменяется на противоположное при каждом изменении сигнала на входе синхронизации от «0» к «1».

Синхронный Т-триггер в отличие от асинхронного Т-триггера реагирует на импульсы, поступающие на вход синхронизации (рисунок 2.14, б) только при подаче на управляющий вход активного уровня.

(Т = 1). Т-триггеры самостоятельного применения в цифровой технике не находят, однако на их базе реализуются некоторые типы счетчиков в интегральном исполнении.

Т-триггер на логических элементах И–НЕ можно построить по схеме рисунка 2.15.

t

t4

t3

t2

t1

Q

T

Q

(R)

&

&

DD2

DD4

T

B

&

(S)

DD1

A

&

DD3

t

t

Рисунок 2.15 – Т-триггер на логических элементах И-НЕ

В

отличие от D-триггера

вход А

логического элемента DD3

постоянно

соединен с выходом

.

Действует триггер следующим образом.

Когда Q

= 1, на другом выходе

=

0. Так как вход А

соединен с

выходом

,

то и А = 0. После поступления тактового

импульса на вход Т

на выходах установится Q

= 0 и

=

l.

На выходе А

при поступлении следующего тактового

импульса уже будет напряжение высокого

уровня и произойдет очередная смена

состояния.

.

Действует триггер следующим образом.

Когда Q

= 1, на другом выходе

=

0. Так как вход А

соединен с

выходом

,

то и А = 0. После поступления тактового

импульса на вход Т

на выходах установится Q

= 0 и

=

l.

На выходе А

при поступлении следующего тактового

импульса уже будет напряжение высокого

уровня и произойдет очередная смена

состояния.

JK-триггер

JK-триггер представляет собой обобщенную версию RS–триггера, представленную на рисунках 2.16, 2.17.

Вход J соответствует входу S, а вход К – входу R. В отличие от RS-триггера, состояние которого не определено при комбинации S = 1 и R= l, JK-триггер при комбинации J = 1, К = 1 по синхроимпульсу изменяет свое состояние на противоположное, т. е. реализует функции Т-триггера. Поэтому на базе JK-триггера легко реализуется синхронный Т-триггер путем объединения входов и использовании их в качестве входа Т.

в

б

а

Запись

Запись

Хранение

Режим

T-триггер

"0"

"0"

CJ K

Q

TT

JCK

JCK

Q

SCR

TT

&

&

SCR

t

Q

Рисунок 2.16 – Схема (а), условное графическое обозначение (б) и временная диаграмма (в) работы синхронного JK-триггера

Рисунок

2.17 – JK-триггер

на логических элементах И–НЕ

t5

t4

t3

t2

t1

0

0

0

0

K

J

Q

0

1

K

(R)

B4

A4

Q

0

1

J

(S)

&

&

&

&

B3

A3

DD2

DD4

DD1

DD3

t

t

t

t

Функционирование JK-триггера описывается таблицей перехода, приведенной в сокращенной форме в таблице 2.4.

Таблица 2.4

J |

К |

Q |

0 |

0 |

Q(t) |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

|