- •Р еферат

- •Т ехнічне завдання:

- •Цифрові комбінаційні пристрої

- •1.2 Цифрові Пристрої з пам’яттю

- •2. Практична частина: Завдання 1

- •Хід роботи:

- •Побудуємо схему перетворювача кодів.

- •Завдання 2

- •Хід роботи:

- •Аналіз перехідних процесів

- •Завдання 3:

- •Хід роботи:

- •Завдання 4

- •Рішення:

- •С писок літератури

- •В исновок

М іністерство

освіти і науки, молоді і спорту України

іністерство

освіти і науки, молоді і спорту України

Державний вищий навчальний заклад

Український Державний хіміко-технологічний університет

факультет: «Сучасних технологій»

Кафедра: «Спеціалізованих комп’ютерних систем»

Курсова робота

з предмету: «Комп.схемотехніка»

на тему: «Цифрові комбінаційні пристрої. Цифрові пристрої

з пам’яттю»

Виконав: ст.групи 2-СКС-5 Піотровский А.С

Перевірив: доц.каф. СКС Сергєєва О.В.

м. Дніпропетровськ

2012

З міст:

міст:

Вступ………………………………………………….3

Реферат………………………………………………4

Технічне завдання………………………………….5

Теоретичні відомості про:

4.1 Цифрові комбінаційні пристрої…………….….6

4.2 Цифрові пристрої з пам’яттю……………….…11

Практична Частина……………………………….20

Висновки…………………………………………..32

Список Літератури………………………………33

В ступ

Головними задачами при виконання курсової роботи є :

- закріплення та розширення знань по предмету схемотехніка;

набуття навичок самостійної роботи;

отримання навичок збору та аналізу необхідної літератури;

вміння працювати з літературою;

формування досвіду по роботі з документацією

Комп’ютерна схемотехніка – це технічний напрямок, зв’язаний із розробкою, від лагодженням, обслуговуванням комп’ютерних, комп’ятеризованих та інтегрованих систем.

Ці знання необхідні фахівцям, зв'язаним з інтенсивним використанням комп'ютерної техніки, автоматизованих систем обробки даних і керування, спеціалістам з електроніки та радіотехніки, цифрових автоматів і робототехніки.

Знання комп'ютерної схемотехніки потрібно також всім тим, хто зв'язаний із створенням програмного забезпечення автоматизованих систем і комп'ютерів, що визначається тісною взаємодією апаратних й програмних засобів. Програміст, що добре знає апаратну частину завжди має перевагу перед іншими, його програми будуть більш ефективнішими та досконалішими.

Р еферат

Пояснювальна записка: джерела інформ.

Об’єкт розробки курсової роботи цифрові комбінаційні пристрої і цифрові пристрої з пам’яттю.

Мета роботи: Розробка цифрових комбінаційних пристроїв та цифрових пристроїв з пам’яттю.

Ключові слова: суматор, дешифратор, шифратор, перетворювач кодів, мультиплексор, демультиплексор, тригер, регістр, лічильник.

Т ехнічне завдання:

Завдання 1

Розробити перетворювач коду по схемі дешифратор-шифратор з шифратором виконаним по матричній діодній схемі, для перетворення вхідних функцій, заданих табл., у відповідні їм вихідні за умови, що вхідні функції задані двійковим чотирирозрядним кодом, вихідні — двійковим п'ятирозрядним кодом, а діапазон зміни параметра що складає (0...1) π/2 з дискретністю 0,1.

Завдання 2

Розробити на основі мультиплексора 8×1 (наприклад, мікросхема

К155КП7) комбінаційну схему для реалізації чотиримісних логічних функцій

Завдання 3:

Розробити на основі мультиплексора 8х1 (наприклад, мікросхема К155КП7) комбінаційну схему для реалізації 4-місних логічних функцій, заданих табл.1.

Дослідити роботу пристрою за допомогою електронного симулятора MicroCap.

Завдання 4

Розробити 3-розрядний паралельний регістр реалізації трьох функцій y1, y3, y9 з використанням Т-тригера. Побудувати і намалювати схему, виконати моделювання симулятором MicroCap, по часових діаграмах визначити час виконання мікрооперації tМО і максимальну частоту надходження керуючих сигналів fymax.

Завдання 5:

Розробити на основі мікросхеми К155ИЕ6 та К155ИЕ7 дільник частоти послідовних імпульсів, який робить з двійковими і двійково-десятковими кодами, з коефіцієнтом ділення Kділ. Побудувати і намалювати схему, виконати моделювання симулятором MicroCap, по часових діаграмах визначити максимальну частоту надходження вхідних імпульсів fmax.

Цифрові комбінаційні пристрої

Пристрої, що оперують з двійковою (дискретною) інформацією, підрозділяються на два класи: комбінаційні і послідовнісні (часові). [1]

Комбінаційні пристрої характеризуються відсутністю пам'яті. Сигнали на їх виходах у будь-який момент часу однозначно визначаються поєднанням сигналів на входах і не залежать від попередніх станів. Схемними ознаками таких пристроїв служить відсутність ланцюгів зворотного зв'язку, тобто замкнутих петель, для проходження сигналів з виходів на входи. Комбінаційні пристрої характеризуються великою різноманітністю, проте серед них можна виділити ряд типових, таких, що найчастіше зустрічаються на практиці. До них відносяться суматори, дешифратори, шифратори, перетворювачі кодів, мультиплексори, демультиплексори, схеми порівняння код та інші.

1.1.1 Суматори.

Суматорами є функціональні цифрові пристрої, що виконують операцію складання чисел. У цифровій техніці додавання здійснюється в двійковому або, рідше, двійково-десятковому коді. По характеру дії суматори підрозділяються на комбінаційні (що не мають елементів пам'яті) і накопичувальні (такі, що зберігають результати обчислень). У свою чергу, кожен з суматорів, що оперує з багаторозрядними числами, залежно від способу їх складання може бути віднесений до послідовного або паралельного типу.

Складання багаторозрядних чисел в послідовних суматорах здійснюється порозрядно, послідовно в часі, а в суматорах паралельного типу — одночасно.

Як послідовні, так і паралельні суматори будуються на основі однорозрядних додавальних схем.

Складання виконується в кожному розряді окремо, але з урахуванням результату складання попереднього розряду. Так, складання цифр А1 і В1 молодшого розряду дає біт суми S1, і біт перенесення Р1. У наступному (другому) розряді відбувається складання цифр Pl, А2 і В2, яке формує суму S2 і перенесення Р3. Операція триває, поки не буде складена кожна пара цифр в усіх розрядах. Результатом складання буде число , де Рп і S1 відображають 1 або 0, отримані в результаті порозрядною складання.

1.1.2 Дешифратори. Дешифратор (декодер) — це комбінаційний пристрій з декількома входами і виходами, у якого певним комбінаціям вхідних сигналів відповідає активний стан одним з виходів. Дешифратори перетворюють двійковий і двійково-десятковий коди в унітарний код, тобто код двійкового п-розрядного числа, представленого 2n розрядами тільки один з розрядів якого рівний 1.

Дешифратори можуть бути повними і неповними У повного дешифратора n входам відповідає 2n виходів.У неповного дешифратора число виходів m <2n.

Відомі три основні структури дешифраторів: матрична (лінійна), каскадна і пірамідальна.

Матричні (лінійні) дешифратори складаються з 2n логічних схем збігу кожна з яких має n входів. На входи цих логічних елементів подаються всі можливі комбінації прямих і інверсних розрядів числа X, що дешифрується.

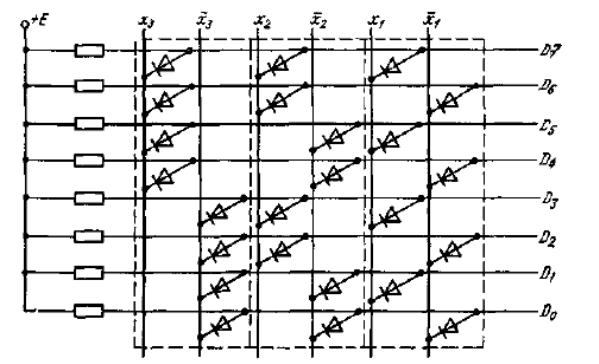

Матричні дешифратори мають найвищу швидкодію. Час затримки появи сигналу на виході в дешифраторах з n-вхідними логічними елементами складає час затримки одного елементу (ЗЗttΣ=, але їх недолік — велике число входів логічних елементів із зростанням розрядності Цей недолік є менш істотним при використанні діодної логіки. Приклад схеми дешифратора 3.8, виконаного на діодній логіці, приведений на рис. 1. Для того, щоб такий дешифратор мав властивість наращуваності для збільшення розрядності вхідного числа, він повинен будуватися з однакових схем (на рис. 1. обведені пунктирною лінією). Так, матричний дешифратор 2.4 може бути побудований на основі двох таких схем, дешифратор 3.8 — на основі трьох схем, дешифратор 4.16 — на основі 8 схем, дешифратор 5.32 — на основі 20 схем і т. д.

Рис. 1.1. Схема дешифратора 3.8, виконаного на діодній логіці

При каскадній побудові дешифраторів вхідне число розбивається на декілька підчисел, кількість яких може знаходитися в діапазоні від 2 до 2n.При непарному значенні n кількість підчисел округляється у бік найближчого більшого цілого числа. Для кожною підчисла формуються всі його мінтерми шляхом побудови окремих матричних дешифраторів. Всі дешифратори підчисел складають перший каскад дешифратора. У кожному подальшому каскаді утворюють кон'юнкції мінтермів з попереднього каскаду. Залежно від n і числа входів логічних елементів каскадний дешифратор можна виконувати в різних варіантах що відрізняються числом каскадів, числом матричних дешифраторів і т. iн.

Мікросхема має чотири адресні входи D0…D3, два входи дозволу і 16 виходів, пронумеровані від 0 до 15. Якщо на обох входах дозволу підтримується рівень V0 = V1 = 0, мікросхема працює як дешифратор. Потенціал U1 на будь-якому з входів дозволу встановить рівень U1 на всіх виходах незалежно від стану входів. Для нарощування розрядності (наприклад, отримання дешифратора 5.32) шини молодших чотирьох розрядів з’єднують з входами D0…D3 обох мікросхем, а сигнали старшого розряду подають в прямому вигляді на один з входів дозволу першої мікросхеми, в інверсному — на вхід дозволу другої. Інші входи дозволу заземлюють.

1.1.3 Шифратори. Шифратором називається комбінаційний пристрій, що перетворює унітарний код, який подається на вхідні шини, у відповідний код на вихідних шинах. Таким чином, шифратори виконують функцію, зворотну тій, що виконується дешифратором. Якщо з вихідних шин шифратора знімається n-розрядний то максимальне число вхідних шин визначається числом можливих кодових комбінації і складає 2n. [3]

Розглянемо як приклад синтез шифратора з п'ятьма входами, що перетворює унітарний код в двійковий. Фрагмент таблиці істинності цього шифратора приведений вигляді табл.3. На решті наборів вхідних змінних вихідні функції мають байдужі значення.

Таблиця 1.1

Входи |

Виходи |

|||||||

х1 |

х2 |

х3 |

х4 |

х5 |

F1 |

F2 |

F3 |

|

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

|

Рівняння, що описують функції F1, F2 і F3, найзручніше представити у вигляді

1531243321,,.FxxxFxxFxx=++=+=+.

Найпростіше шифратори реалізуються на діодній логіці. Так, для приведеного прикладу діодний шифратор повинен мати п'ять вхідних і три вихідних шини, причому кожна вхідна шина з'єднується через діоди з вихідними відповідно до рівнянь або безпосередньо по таблиці істинності.

1.1.4 Перетворювачі кодів (ПК). Призначені для перетворення одного паралельного коду в іншій. Вони використовуються для шифруванняі дешифрування цифрової інформації і можуть мати n входів і k виходів Співвідношення між числами n і k можуть бути будь-якими n = k, n < k, n > k.

За призначенням ПК можна розділити на два типи з неваговим і з ваговим перетворенням кодів. У перетворювачах першого типу відсутній числовий взаємозв'язок вхідного і вихідного коду, а має місце символьний взаємозв'язок наприклад перетворення двійково-десяткового коду в код семисегментного індикатора десяткових цифр. Перетворювачі другого типу використовуються, як правило, для перетворення числової інформації, тоді між числами вхідного і вихідного коду має місце заданий математичний взаємозв'язок.

Перетворення n-елементного коду в k-елементний можна здійснити з попереднім дешифруванням першого коду і без нього. В першому випадку спочатку дешифрується n-елементний код і на кожній з 2n вихідних шин виходить сигнал, відповідний одній з вхідних кодових комбінацій. Потім кожен з вихідних сигналів кодується в k-елементному коді за допомогою шифратора.

Як дешифратор використовується повний дешифратор 3.8, а як шифратор — діодний матричний шифратор.

1.1.5 Myльтиплексори. Myльтиплексором називається комбінаційний пристрій призначений для комутації у бажаному порядку сигналів з декількох вхідних шин на одну вихідну. За допомогою мультиплексора здійснюється часове розділення інформації, що поступає по різних каналах. Його можна уподібнити безконтактному багатопозиційному перемикачу.

Входи мультиплексора діляться на інформаційні, адресні і вирішуючі (стробувальні). На інформаційні входи подається інформація передавана на вихід мультиплексора. Адресні входи допомагають вибрати потрібний інформаційний вхід, а на вирішуючий вхід подається стробуючий сигнал, що вирішує підключення вибраного входу на один загальний вихід (рідше два взаємоінверсних). Вирішуючий вхід, як правило, один, а число інформаційних і адресних входів взаємозв'язане. Якщо число адресних входів n, то з їх допомогою можна комутувати 2n каналів тобто число інформаційних входів 2n.

1.1.6 Демультиплексори. Демультиплексори у функціональному відношенні протилежні мультиплексорам. У них сигнали з одного інформаційного входу розподіляються в необхідній послідовності по декількох виходах відповідним кодам на адресних входах. При n адресних входах демультиплексор може мати до 2n виходів.

Принцип роботи демультиплексора, де х — інформаційний, А — адресний входи. Залежно від сигналу А по адресному входу відкритий верхній або нижній логічний елемент і через нього сигнал х підключається або до виходу F0, або до виходу F1. Як і мультиплексори, демультиплексори доповнюються керуючім входом V. Демультиплексори можуть також бути виконані з використанням дешифратора і додаткової логіки .В цій схемі дешифратор виконує роль адресного пристрою, за допомогою якого вибирається відповідна схема І, на інші входи кожної схеми І подаються загальні інформаційний х і сигнал дозволу V.