- •Вопрос 42. Аппаратные методы ускоренного умножения: умножители по схеме Уоллеса.

- •Вопрос 43. Деление с восстановлением и без восстановления остатка. Структура арифметико-логического устройства для целочисленного деления.

- •Вопрос 44. Организация операций сложения, умножения и деления над числами с плавающей запятой.

- •Подготовительный этап.

- •Выполнение операции.

- •Заключительный этап.

- •Вопрос 45. Организация шин. Типы шин. Арбитраж шин.

- •Вопрос 46. Принципы работы системной шины p6.

- •Вопрос 47. Шина pci. Адресация на pci шине.

- •Вопрос 48. Базовая операция чтения на шине pci.

- •Вопрос 49. Базовая операция записи на шине pci.

- •Вопрос 50. Архитектура ibm system z.

Вопрос 46. Принципы работы системной шины p6.

Теория от Попова

Частота:66,100,133.

Количество абонентов: 16

Разрядность адреса: 32

Разрядость данных: 64

Контроль информации: PE и ECC

Поддержка операций с кэш

Пакетная и транзакционная передача

Каждое устройство-агент, подключенное к этой шине (например, любой из процессоров), до инициализации запроса должно получить через механизм арбитража право на использование шины запроса. Запрос выходит за два смежных такта: в первом такте передается адрес, тип обращения (чтение-запись памяти или ввода/вывода) и тому подобная информация. Во втором такте передается уникальный идентификатор транзакции, длина запроса, разрешенные байты шины и т. п. Через три такта после запроса проверяется состояние ошибки (error status) для защиты от ошибок передачи или нарушений протокола.

Любая обнаруженная ошибка вызывает повтор запроса, а вторая ошибка для того же запроса вызывает исключение контроля (machine check exception).

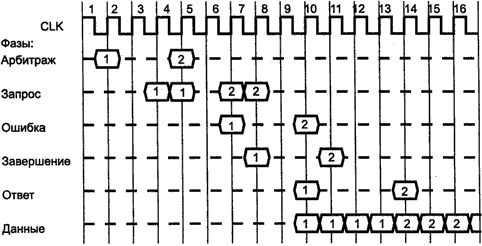

Рисунок 46.1 – Две транзакции на системной шине P6

Теория с http://www.psv-cmos.narod.ru/dib.htm

Применение динамического выполнения резко повышает частоту запросов процессорного ядра к шине за данными памяти и инструкциями, поскольку ядро одновременно обрабатывает несколько инструкций. Для обхода узкого места - внешней шины - кристалл процессорного ядра использует архитектуру двойной независимой шины (Dual Independent Bus). Одна из этих шин используется только для связи с кристаллами вторичного кэша, расположенными в том же корпусе микросхемы, а у Pentium-2 - на общем картридже. Эта шина является локальной и в геометрическом смысле - проводники имеют длину порядка единиц сантиметров, что позволяет ее использовать на частоте ядра процессора. Значительный объем вторичного кэша позволяет удовлетворять большинство запросов к памяти сугубо локально, при этом коэффициент загрузки шины достигает 90%. Вторая шина процессорного кристалла выходит на внешние выводы микросхемы, она и является системной шиной процессора Pentium Pro. Эта шина работает на внешней частоте независимо от внутренней шины. Загрузка процессором внешней шины для обычных рядовых применений составляет порядка 10% от ее пропускной способности, а для серверных применений может достигать 60% при четырехпроцессорной конфигурации. Таким образом, ограниченная пропускная способность внешней шины (533 Мбайт/с в пике пакетной передачи при частоте шины 66 МГц) перестает сильно сдерживать производительность процессора. Снижение нагрузки на внешнюю шину позволяет эффективно использовать многопроцессорную архитектуру.

Максимальную пропускную способность для процессоров, использующих архитектуру двойной независимой шины, с некоторыми оговорками можно рассчитать как сумму пропускной способности системной шины (533 Мбайт/с) и пропускной способности шины вторичного кэша.

Системная шина Pentium Pro и Pentium-2 более эффективна для объединения процессоров по симметричной архитектуре, чем шины предыдущих процессоров, оптимизированные для обмена с памятью. Она позволяет без дополнительных схем объединять до четырех процессоров.

Сигналы системной шины объединяются в группы запросов (Request) и ответов (Response). Каждое устройство-агент, подключенное к этой шине (например, любой из процессоров), до инициализации запроса должно получить через механизм арбитража право на использование шины запроса. Запрос выходит за два смежных такта: в первом такте передается адрес, тип обращения (чтение-запись памяти или ввода/вывода) и тому подобная информация. Во втором такте передается уникальный идентификатор транзакции, длина запроса, разрешенные байты шины и т. п. Через три такта после запроса проверяется состояние ошибки (error status) для защиты от ошибок передачи или нарушений протокола. Любая обнаруженная ошибка вызывает повтор запроса, а вторая ошибка для того же запроса вызывает исключение контроля (machine check exception).

Шинные транзакции делятся на множество фаз, перекрывающих друг друга. На рисунке 46.1 изображены две транзакции.

В фазе завершения все агенты, отвечающие на данный запрос, при необходимости могут выставить на шину коды завершения. Другие процессоры в этой фазе управляют линиями Hit# и HitM# в зависимости от попадания запроса в их внутренний кэш. Агент, не успевающий ответить за отведенные четыре такта, может выставить одновременно сигналы Hit# и HitM# для задержки фазы завершения на число тактов, кратное двум. В случае кэш-попадания запрос к памяти удовлетворит процессор, поскольку передачи кэш-кэш происходят быстрее. Однако при попадании в модифицированную строку (HitM#) циклы обращения к памяти неизбежны.

На шине одновременно может присутствовать множество запросов и ответов, однако логический анализатор, "понимающий" протокол шины Pentium Pro, способен разложить их всех на соответствующие транзакции.

Hit#,HitM# |

I/O |

Сигналы результатов операции слежения за транзакцией. Hit# (Snopp hit) указывает на кэш-попадание. HitM#(Hit Modified) указывает на попадание в модифицированную строку, запрещая другим контроллерам шины обращаться к этим данным до выполнения обратной записи. |

Краткое объяснение от Алекса:

В семействе процессоров P6 используется двойная независимая системная шина, позволяющая объединять до 16 абонентов. В данной шине используется транзакционный механизм. Для использования шины запроса каждое устройство должно получить право от схемы арбитража. Запрос занимает два такта, в первой части передается адрес, тип обращения. А во второй части идентификатор транзакции, длина запроса, разрешенные байты шины. В случае ошибки запрос повторяется. В случае повторной ошибки вызывается исключение контроля.