- •Глава_5 Синтез последовательностных схем (элементов памяти), используемых в качестве элементной базы в мп сау.

- •5.1 Синтез асинхронных триггеров.

- •5.1.1 Синтез первой минимальной формы для запоминающего элемента.

- •5.2 Синтез второй минимальной формы при построении запоминающего элемента.

- •Лабораторный практикум №5.1.

- •Лабораторный практикум №5.2.

- •Лабораторный практикум №5.3

- •5.3 Синхронные элементы памяти, используемые в мп сау.

- •5.3.1 Синтез двухступенчатого элемента памяти, работающего в парафазном коде.

- •5.4 Синхронные элементы памяти для последовательных регистров (d - триггеры).

- •5.5 Синтез двухступенчатого т - триггера.

- •5.5.1. Синхронный т - триггер на элементах и-не.

- •5.5.2. Синтез комбинированного rst – триггера

- •Лабораторный практикум № 5.4.

- •5.6 Универсальные элементы памяти. Принцип организации специальных элементов памяти на базе универсальных.

- •5.6.1 Синтез универсального jk – триггера.

- •Лабораторный практикум №5.5.

- •Вопросы для самоконтроля знаний по материалам главы 5.

Глава_5 Синтез последовательностных схем (элементов памяти), используемых в качестве элементной базы в мп сау.

5.1 Синтез асинхронных триггеров.

Синтез асинхронных триггеров основан на использовании функции переходов запоминающего элемента с двумя устойчивыми состояниями (табл.5.1). Такую функцию представим в виде таблицы переходов:

Таблица 5.1

Sn |

Rn |

Qn |

Qn+1 |

0 0 |

0 0 |

0 1 |

0 1 |

0 1 |

1 0 |

0 1 |

0 1 |

1 0 |

0 1 |

0 1 |

1 0 |

1 1 |

1 1 |

0 1 |

- - |

n-автоматное (целочисленное) время;

Q-состояние запоминающего элемента.

1. При отсутствии входных возмущений Sn или Rn запоминающий элемент сохраняет исходное состояние: Qn+1 = Qn (сохраняется)

2. Если входной сигнал действует на вход, наименование которого совпадает с исходным состоянием, то такое состояние подтверждается в реакции на возмущение. Qn+1 = Qn (подтверждается)

3. Запоминающий элемент изменяет состояние на противоположное, если возмущение действует на вход, соответствующий требуемому состоянию. Qn+1 =Qn

4. Состояние запоминающего элемента при одновременном воздействии на входы R и S произвольно, поэтому при синтезе различных разновидностей запоминающих элементов этому состоянию можно задавать различные комбинации значений истинности Qn+1 ,Qn+1.

5.1.1 Синтез первой минимальной формы для запоминающего элемента.

Qn+1 |

Q |

0 1 0 1 |

0 1 1 0 |

Перенесем содержимое таблицы переходов в карту Карно (табл.5.2) и заменим два последних состояния значениями 1 и 1.

Таблица 5.2

-

Sn , Rn

Qn

00 01 11 10

0

1

0

0

1

1

1

0

1

1

З апишем

минимальную форму функции переходов.

апишем

минимальную форму функции переходов.

Реализуем это выражение на элементах И-ИЛИ-НЕ, НЕ (рис.5.1).

Рис.5.1 Схема запоминающего элемента.

Построим расширенную таблицу переходов для вычисления функций Qn+1 ,Qn+1 и перенесем каждую пару этих вычисленных состояний в расширенную матрицу Карно (табл 5.3).

Таблица 5.3

-

Sn , Rn

Qn , Qn

00 01 11 10

00

01

11

10

11

11

10

10

(01)

(01)

00

00

00

01

00

00

(10)

11

(10)

(10)

Установившимися состояниями запоминающего элемента называются такие комбинации значений (Qn+1 ,Qn+1), которые соответствуют исходным состояниям схемы Qn ,Qn. В матрице отметим эти состояния скобками.

При отсутствии входных возмущений Sn , Rn , запоминающий элемент равновероятно находится в одном из следующих состояний: нулевом 01 или единичном 10.

Устойчивыми считают те из установившихся состояний, которые соответствуют логике работы запоминающего элемента (ЗЭ).

При воздействии на схему сигнала Rn = 1, ЗЭ переходит в нулевое состояние => Qn+1 ,Qn+1 ~ 01; аналогично при воздействии сигнала Sn =1, запоминающий элемент переходит в единичное состояние => Qn+1 ,Qn+1 ~ 10.

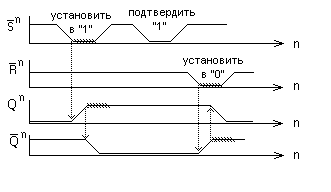

Данный ЗЭ переходит в единичное состояние при одновременном воздействии на него сигналов S и R, при этом он получил название S - триггера и его работа может быть описана следующей временной диаграммой (рис.5.2).

Рис.5.2 Обозначение S-триггера на схемах и его временная диаграмма

Выбор элементной базы для построения ЗЭ в определенных рамках произволен и определяется разработчиком. Все остальные этапы синтеза могут быть формализованы и требуют обязательного анализа установившегося и устойчивого состояний синтезируемого элемента памяти.

Выполним предыдущие этапы синтеза по данным табл.5.4 ,для примера схемы памяти, построенной на элементах И-НЕ (рис.5.3). При условии возмущения ее инверсными значениями сигналов Sn и Rn.

Рис.5.3 Вариант элемента памяти с инверсными входами

Таблица 5.4

-

10 Экв.

Sn

Rn

Qn

Qn

Qn+1

Qn+1

0

0

0

0

0

1

1

1

0

0

0

1

0

1

2

0

0

1

0

1

0

3

0

0

1

1

0

0

4

0

1

0

0

1

1

5

0

1

0

1

0

1

6

0

1

1

0

1

1

7

0

1

1

1

0

1

8

1

0

0

0

1

1

9

1

0

0

1

1

1

10

1

0

1

0

1

0

11

1

0

1

1

1

0

12

1

1

0

0

1

1

13

1

1

0

1

1

1

14

1

1

1

0

1

1

15

1

1

1

1

1

1

-

Таблица 5.6

Sn , Rn

Qn , Qn

00 01 11 10

00

01

11

10

11

11

11

11

(01)

(01)

11

11

00

01

(11)

10

(10)

11

11

(10)

Одновременное воздействие сигналов на инверсные входы схемы Sn и Rn запрещено (табл.5.6), так как исключает общепринятое состояние триггера.

Поэтому функцию переходов этого триггера необходимо дополнить уравнением запрета.

Построим временную диаграмму (рис.5.4) для ЗЭ с инверсными входами.

Рис.5.4 Временная диаграмма синтезированного триггера.

Каждая из возможных разновидностей форм построения ЗЭ может иметь структурные вариации, определяемые конкретными используемыми элементами. Назначение этих вариаций должно быть обосновано конкретным применением синтезируемого элемента в МП САУ.

n+1

n+1