Міністерство освіти та науки України

Національний технічний університет України

«Київський політехнічний інститут»

Факультет інформатики та обчислювальної техніки

Кафедра технічної кібернетики

"КОМП’ЮТЕРНА ЕЛЕКТРОНІКА"

кредитний модуль "Мікропроцесорні системи"

Лабораторна робота №11

Програмування часових затримок

Виконали:

студент гр. ІК-91

Федоров Д. В.

Перевірив:

Ігнатенко В.М.

Київ 2012

Мета роботи: вивчити принцип побудови алгоритмів часових затримок та керування зовнішніми пристроями.

1. Короткі теоретичні відомості.

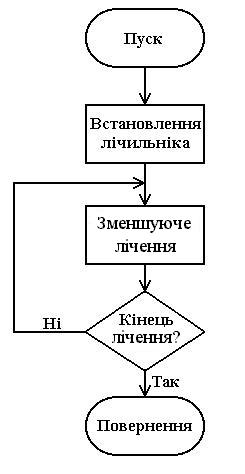

Алгоритм найпростішої програми часової затримки (без видачи керуючих діянь) показаний на мал.1. Для реалізації часової затримки використовується один з внутрішніх регістрів МП, куди спочатку завантажується байт інформації. Після кожного зменшення на одиницю вмісту регістра він перевіряється на рівність нулю; якщо він не дорівнює нулю, програма циклічно повторюється. Час виконання цих двох команд програми відомий, тому тривалість затримки буде визначатися числом циклічних повторень.

Змінюючи значення попередньо завантажуємого байта, можна змінювати тривалість часового інтервалу затримки. Підпрограма, яка реалізує алгоритм затримки, має вигляд:

DELAY: DCR A; зменьшуючий рахунок;

JNZ DELAY; продовжити, якщо не нуль;

RET; повернення.

У програмі використовується акумулятор А. В цьому випадку байт попереднього встановлення лічильника повинен бути завантажений до цього регістру. Це можливо, оскільки результат виконання команд DCR r впливає на стан флагу нуля Z, що входить до регістру флагів F.

Для виконання команд треба:

DCR r; 4 такти;

JNZ 10 тактів у випадку виконання умови;

7 Тактів, якщо умова не виконується;

RET; 10 тактів.

Мал. 1. Алгоритм програми затримки.

Отже, для кожного проходу по петлі треба 4 + 10 = 14 тактів, а для останнього 4 + 7 + 10 = 21 такт, оскільки умова не виконується і JNZ не потребує переходу, але додатково виконується команда RET. Отже, при тривалості такту Т = 0.4 нс максимальна затримка td дорівнює:

td = (( 256 – 1 )* 14 + 21 )* 0,4 = 1436 нс.

Для отримання більш тривалої затримки необхідно використовувати команди, які взаємодіють з парами регістрів:

DELAY: DCX B; зменшуючий рахунок;

MOV A,B; пересилка з В до А;

ORA C; перевірка на нуль;

JNZ DELAY; продовжити, якщо не нуль;

RET; повернення.

Використання команд DCX rp дозволяє завдяки застосування в даному випадку пари регістрів В,С збільшити затримку до N = 2562 = 65536 = 216. Згідно тексту програми регістрова пара повинна бути попередньо завантажена вихідними даними. В підпрограмі перша команда зменшує вміст пари на одиницю (враховуючи перенос між байтами). Оскільки команда не впливає на флаги, для перевірки виконується пересилка вмісту В до акумулятору та порівняння з іншим регістром даної пари, тобто з С, за допомогою команди ОRA C. Флаг (тригер) Z буде встановленний в 1 тільки у тому випадку, якщо вміст В і С буде дорівнювати нулю.

Час затримки td, одержаний при виконанні цієї команди, буде дорувнювати:

td = (( N - 1 )* 24 + 31)* 0,4 (нс),

і для максимального числа N час затримки буде:

td max = ( 65536 – 1 )* 24 + 31)* 0,4 = 0.6 (мс).

Таку затримку можна одержати, якщо попередньо занести "0" до регістрів В і С.

Для отримування ще більшої затримки можна організувати додатковий лічильник, наприклад, в регістровій парі D, який буде визначати, скільки разів виконується затримка у 0.6 мс. Програма, яка це реалізує:

DELAY : LXI B,0000; початок зовнішньої петлі;

LOOP : DCX B; петля затримки 0.6 мс;

MOV A,B; пересилка з В до А;

ORA C; порівняння;

JNZ LOOP; продовження внутрішньої петлі;

DCX D; зовнішня петля затримки;

MOV A, D; пересилка з D до A;

ORA E; порівняння;

JNZ DELAY; продовження зовнішньої петлі;

RET; повернення.

У внутрішньому циклі виконується затримка 0.6 мс, у зовнішньому – послідовність таких затримок. Така організація програми називається вкладанням.

Виконання:

ІДЗ:

Сформувати 3 виводи на світло діоди:

Д4 Д3 – байт 18

Д7 Д0 – байт 81

Д6, Д5, Д4, Д1 – байт 71

Часові затримки: для знаходження кількості зовнішніх циклів потрібно потрібний час затримки t (залежить від частоти процесора, обрана частота 2.5 ГГц) поділити на максимальну довжину затримки, при одному зовнішньому циклі:

10 секунд – 02FF (767) зовнішніх циклів.

1.5 секунд – 0088 (136) зовнішніх циклу.

6 секунд – 01FF (511) зовнішніх циклів.

Адреса |

Код |

Аемблер |

Регістри, лічильники, покажчики |

Коментарі |

|||||

A |

F |

B |

D |

SP |

PC |

|

|||

8000 |

3E |

MVI A,81 |

81 |

- |

- |

- |

83C7 |

8002 |

Програмування інтерфейсу |

8001 |

81 |

||||||||

8002 |

D3 |

OUT FB |

81 |

- |

- |

- |

83C7 |

8004 |

|

8003 |

FB |

||||||||

8004 |

3E |

MVI A, 23 |

18 |

- |

- |

- |

83C7 |

8006 |

Вивід на світлодіоди байту С для вмикання діодів: 4, 3 |

8005 |

23 |

||||||||

8006 |

D3 |

OUT F9 |

18 |

- |

- |

- |

83C7 |

8008 |

|

8007 |

F9 |

||||||||

8008 |

11 |

LXI D, 00C0 |

18 |

- |

- |

02FF |

83C7 |

800B |

Зовнішній цикл затримки (10 с) |

8009 |

C0 |

||||||||

800A |

00 |

||||||||

800B |

CD |

CALL 8025 |

18 |

- |

- |

02FF |

83C5 |

800E |

Виклик підпрограми затримки на 10 секунд |

800C |

25 |

||||||||

800D |

80 |

||||||||

800E |

3E |

MVI A, C0 |

81 |

- |

- |

0 |

83C7 |

8010 |

Вивід на світлодіоди байту 81 для вмикання діодів: 7, 0 |

800F |

C0 |

||||||||

8010 |

D3 |

OUT F9 |

81 |

- |

- |

0 |

83C7 |

8012 |

|

8011 |

F9 |

||||||||

8012 |

11 |

LXI D, 0420 |

81 |

- |

- |

0088 |

83C7 |

8015 |

Зовнішній цикл затримки (1,5 с) |

8013 |

20 |

||||||||

8014 |

04 |

||||||||

8015 |

CD |

CALL 8025 |

81 |

- |

- |

0088 |

83C5 |

8018 |

Виклик підпрограми затримки на 1,5 секунд |

8016 |

25 |

||||||||

8017 |

80 |

||||||||

8018 |

3E |

MVI A, 1C |

71 |

- |

- |

0 |

83C7 |

801A |

Вивід на світлодіоди байту 71 для вмикання діодів: 6, 5, 4,1 |

8019 |

1C |

||||||||

801A |

D3 |

OUT F9 |

71 |

- |

- |

0 |

83C7 |

801C |

|

801B |

F9 |

||||||||

801C |

11 |

LXI D, 06C0 |

71 |

- |

- |

01FF |

83C7 |

801F |

Зовнішній цикл затримки (6 с) |

801D |

C0 |

||||||||

801E |

06 |

||||||||

801F |

CD |

CALL 8025 |

71 |

- |

- |

01FF |

83C5 |

8022 |

Виклик підпрограми затримки на 1,5 секунд |

8020 |

25 |

||||||||

8021 |

80 |

||||||||

8022 |

C3 |

JMP 8004 |

71 |

- |

- |

0 |

83C7 |

8025 |

Безумовний перехід на початок програми (безкінечний цикл) |

8023 |

04 |

||||||||

8024 |

80 |

||||||||

8025 |

01 |

LXI B, FFFF |

X |

- |

FF FF |

Y/0 |

83C7 |

8028 |

Завантаження в р.п. В максимального значення, для отримання затримки 0.786 |

8026 |

FF |

||||||||

8027 |

FF |

||||||||

8028 |

0B |

DCX B |

X |

- |

B-1 |

Y/0 |

83C7 |

8029 |

Зменшення значення р.п. В |

8029 |

78 |

MOV A, B |

B |

- |

- |

Y/0 |

83C7 |

802A |

Занесення до акумулятора старшої половини р.п. В |

802A |

B1 |

ORA C |

B |

0/1 |

- |

Y/0 |

83C7 |

802B |

Порівняння старшої та молодшої половини |

802B |

C2 |

JNZ 8025 |

B |

- |

- |

Y/0 |

83C7 |

802E

|

Перехід на початок внутрішнього циклу |

802C |

28 |

||||||||

802D |

80 |

||||||||

802E |

1B |

DCX D |

B |

- |

- |

Y-1 |

83C7 |

802F |

Зменшення лічильника зовнішнього циклу |

802F |

7A |

MOV A, D |

|

|

|

|

|

8030 |

|

8030 |

B3 |

ORA E |

|

|

|

|

|

8031 |

|

8031 |

C2 |

JNZ 8022 |

B |

- |

- |

0 |

83C7 |

8034 |

Перехід на початок зовнішнього циклу |

8032 |

25 |

||||||||

8033 |

80 |

||||||||

8034 |

C9 |

RET |

B |

- |

- |

0 |

83C7 |

|

Повернення |

Х – в залежності від потрібної послідовності ввімкнутих світодіодів, буде різне значення акумулятора. В даній програмі: 18, 81 та 71.

Y – в залежності від кількості потрібних зовнішніх циклів. В даній програмі: 13, 2 та 8. З кожним проходом зовнішнього циклу D зменшується на 1, отже на виході підпрограми ми отримуємо 0 в регістрі D.

Висновок: в даній лабораторній роботі я навчився програмувати часові затримки за допомогою циклів з потрібною кількістю повторів. Це пояснюється тим, що кожен цикл виконується за певну послідовність тактів. Знаючи частоту процесора можна визначити час виконання одного такту. Звідси час циклу – (кількість тактів у циклі) * (час виконання одного циклу). Для створення більш довгої часової затримки можна використовувати вкладені цикли.