2.3. Уточненная структурная схема контроллера

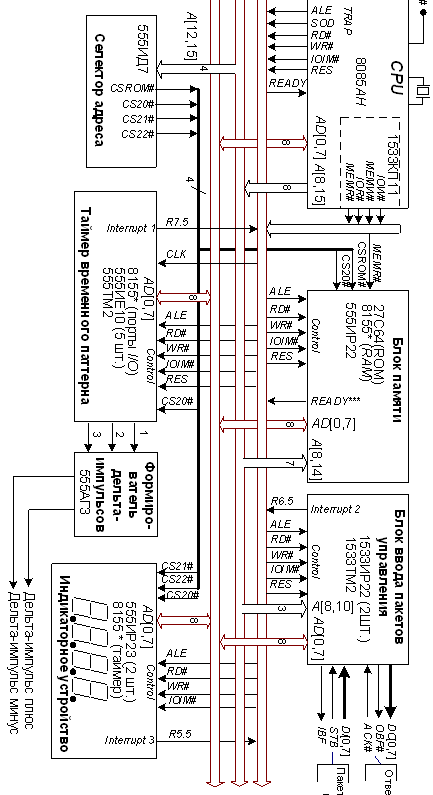

Уточненная структурная схема контроллера (рис. 15) содержит блок CPU, блок памяти, блок ввода пакетов управления, селектор адреса, таймер временного паттерна, формирователь сигналов возбуждения аналогового сигнала (дельта-импульсов) и индикаторное устройство. В составе каждого блока указаны используемые приборы комплекта МСS-85 и другие БИС, а также входные и выходные сигналы, предназначенные для управления.

Системная шина представлена мультиплексной шиной данных/адреса AD[0,7], которая дополнена шиной старшего адреса A[8,15] и шиной управления СВ. Шина управления содержит сигналы, сгенерированные микропроцессором и необходимые для управления приборов комплекта MCS-85, а также системные сигналы приборов общего назначения. В состав СВ введены сигналы запросов прерывания, которые распределены следующим образом:

• Запрос прерывания с высшим приоритетом (R7.5) предоставлен таймеру временного паттерна. Обслуживание этого запроса прерывания представляет наибольшую ценность, он имеет высший приоритет, так как формирует измерительный сигнал.

• Запросы прерывания R6.5 и R5.5 используются для обслуживания входных пакетов управления контроллером и устройства индикации. Задержки в обслуживании этих запросов не имеют столь высокой цены;

• Запрос прерывания TRAP не используется в данной разработке; он предназначен для обслуживания аварийных ситуаций, в частности аварий блока питания контроллера.

• Вход МП Interrupt в данном варианте также не используется.

Селектор адреса представлен на структурной схеме отдельным блоком, и его сигналы выделены в отдельную шину. Это сделано для того, чтобы подчеркнуть особенности двухуровневой дешифрации адреса, использованной в контроллере.

Уточненная структурная схема контроллера представлена на рис.15.

2.4 Таймер временного паттерна

Из описания функционирования имитатора следует, что временной паттерн должен состоять из 16/18 временных интервалов, имеющих значения 1000 мкс, 2000 мкс и 100000-(7*1000) мкс, в начале каждого их которых в аналоговый блок выводятся короткие дельта импульсы положительной или отрицательной полярности.

Для формирования временного паттерна требуется программируемый таймер, способный изменять модуль счёта от 1000/T0 до 93000/T0, где T0 – период счётной частоты таймера, 0,2 мкс. Тогда максимальный модуль счёта, требуемый от таймера равен 465000. Учитывая, что счётчики 74LS593 имеют 8 разрядов, для реализации требуется 3 микросхем. 3 микросхмы 74LS593, соединенные последовательно, создадут счётчик на 24 разряда. Значение 224 = 16777216 – максимальный модуль счёта выбранного варианта таймера. В состав74LS593 включен входной регистр хранения модуля пересчета. В нем реализована возможность подключения схемы непосредственно с системной шине микропроцессора. Последнее избавляет от необходимости предусматривать регистры хранения модуля пересчета

Триггер DD13.2 и логический элемент DD16.2 предназначены для запуска таймера по сигналу "Старт", поступающему от управляющей ЭВМ. В исходном состоянии выход триггера соответствует значению логической "1", которое устанавливается выходным сигналом микропроцессора RESET_OUT при его включении. Запуск триггера производится (по сигналу Intr port A с порта С прибора 8155) по факту прихода третьего байта стартовой последовательности, причем разрешение на запуск триггера DD13.2 (SOD = "1") устанавливается из подпрограммы обработки прерывания после прихода второго байта стартовой последовательности[2].

Список литературы.

Смирнов Б. И. Проектирование микроконтроллеров: Учебное пособие. СПб: Изд-во СПбГЭТУ «ЛЭТИ», 2008. 100 с.

Смирнов Б.И., Добырин В.В. Цифровые и микропроцессорные устройства. Лаб. практикум. СПБ.: Изд-во СПбГЭТУ «ЛЭТИ», 2003. 68 с.

Пухальский Г. И. “Проектирование микропроцессорных устройств”: Учебное пособие для Втузов. СПб.: Политехника, 2001

Пакет программ, документации и шаблонов программного обеспечения по дисциплине «Цифровые и микропроцессорные устройства», CD-верс. 9-14, 2009 года.

Новосельцева Т. Я., Пухальский Г. И. Цифровые устройства: Учеб. пособие для вузов. СПб.: Политехника, 1996.