- •Билет №1 - сети эвм Программная и логическая структура сети.

- •Билет №1. - ипу Интерфейс связи клавиатуры с персональным компьютером. Временная диаграмма передачи данных от клавиатуры в системный блок пк.

- •Билет №2 -сети Методы доступа к каналу в лвс.

- •Билет №2. -ипу Основные этапы выполнения программы прерывания int 9 (ввод данных из клавиатуры)

- •Билет №3 -сети Манчестерские коды.

- •Билет № 3. -ипу Назначение контроллера клавиатуры пк. (Основные функции и основные узлы)

- •Билет №4 -сети Протокол hdlc.

- •Билет №4; Билет №7-ипу Назначение lpt-порта и его регистров

- •Билет №5; Билет №22-сети Методы доступа к спутниковым каналам связи в сетях эвм.

- •Билет №5.-ипу Физическая реализация интерфейса Centronics. Назначение линий интерфейса

- •Билет №6 ; Билет №21-сети Адресация в ip-сетях. Маски.

- •Билет №6. -ипу Назначение и организация интерфейса rs 232-с. Суть асинхронного режима передачи по интерфейсу

- •Билет №8 -сети Задачи проектирования сетей эвм (постановки задач).

- •Билет № 8.-ипу Назначение кэш-памяти винчестера (вместо этого «Контроллер hdd»)

- •Билет №9 -сети

- •Isdn. Технология.

- •Билет № 9.-ипу Назначение узла ramd ac видеоадаптера

- •Билет №10 ; Билет №18 ; Билет №24-сети Стек протоколов tcp/ip.

- •Билет № 10.-ипу Архитектура шины usb

- •Билет №11-сети Технология Frame Relay.

- •Билеты № 11, 25-ипу Назначение сигналов внешнего интерфейса rs-232c

- •Билет №12 -сети

- •Билет № 12.-ипу Перечислите классификационные характеристики стандартных интерфейсов пк

- •Билет №13 -сети Транспортная сеть. Протокол X.25/3.

- •Билет № 13.-ипу

- •2.1.1. Интерфейс isa-8

- •Билет №14 -сети Функции брандмауэра и proxy.

- •Билет № 14.-ипу Билет№ 21. Связь контроллера fdd с накопителем. Назначение сигналов интерфейса с накопителем

- •Билет №15 ; Билет №19-сети

- •Билет № 15.-ипу Организация видеопамяти видеоадаптера в текстовом и графическом режимах

- •Билет №16 -сети Доменная система имен dns.

- •Билет № 16.-ипу Назначение карты agp. Какие компоненты пк соединяет интерфейс agp?

- •Память микроопераций Контроллер атрибутов g

- •Видеопамять

- •Билет №17 ; Билет №25-сети Маршрутизация в сетях. Отличия протоколов rio и ospf.

- •Билет № 17.-ипу Назовите назначение управляющих сигналов ras#, cas#, we#, поступающих в банки памяти пк

- •Билет № 18.-ипу Программа прерывания int 16h (поддержка клавиатуры). Операции программы

- •Билет № 19.-ипу Модули (биСы), выполняющие системные функции в пк. Назначение

- •Билет № 20.-ипу Последовательность пакетов при вводе-выводе по usb

- •А) вывод данных

- •Б) Ввод данных

- •Билет № 22.-ипу Контроллер fdd. Назначение. Регистры контроллера

- •Билет №23 -сети Коммутация каналов, сообщений, пакетов.

- •Билет № 23.-ипу Временная диаграмма передачи данных по интерфейсу “Centronics”. Поясните по диаграмме процесс передачи данных

- •Билет №24-ипу Драйвер (программа обслуживания) внешнего последовательного интерфейса rs 323-c. Операции и их назначение

Билет № 13.-ипу

Физическая реализация интерфейса ISA. Особенности применения интерфейса ISA в компьютерах типа PC\XT и современных компьютерах

Системный интерфейс ISA (Industry Standard Architecture) применялся в ВТ с первых моделей ПК, ставший в последствии промышленным стандартом. По стандарту существует 2 типа интерфейсов ISA: ISA-8 и ISA-16. В ПК PC/XT использовался интерфейс ISA-8 с разрядностью данных 8 бит и адреса -20 бит. В ПК PC/АT шину данных расширили до 16 бит, а шину адреса до 24-х бит. Новый стандарт обозначался ISA-16.

2.1.1. Интерфейс isa-8

Назначение и организация интерфейсa ISA-8. СИ ISA-8 является процессорно-ориентированной системной магистралью, содержащей средства буферизации, декодирования и передачи набора сигналов микропроцессора Intel 8088, дополненного сигналами управления прерываниями и прямого доступа к памяти. Интерфейс предназначен для обмена информацией между центральным процессором с 8-разрядной шиной данных и памятью или контроллерами внешних устройств. Поддерживает однопроцессорную конфигурацию системы. По своим характеристикам является системным, параллельным, мультиплексным и имеет синхронный протокол связи. Связь между двумя функциональными модулями осуществляется по принципу задатчик – исполнитель. Сигналы на интерфейсе имеют стандартные ТТЛ-уровни.

Физически интерфейс ISA-8 представляет собой монтажную системную плату, реализованную в виде многослойной печатной платы с памятью 62-контактными разъемами расширения, позволяющими присоединять дополнительные устройства – платы расширения памяти, платы контроллеров внешних устройств. Большее число разъемов на системной плате устанавливать не рекомендуется из-за превышения допустимой нагрузки на интерфейсе.

По назначению линии сигналов интерфейса ISA-8 можно разделить на следующие группы: передачи данных; прерывания; управления ПДП; общего назначения; электропитания. К группе линий передачи данных относятся:

А19-А0 – «20»-разрядная адресная шина. Адресные линии используются задатчиками для адресации ячеек памяти или портов ввода-вывода. Сигналы на эти линии поступают либо из центрального процессора, либо из котроллера ПДП. Линии А0-А19 обеспечивают доступ к памяти объемом на 1 Мбайт. Для портов ввода-вывода отводится 512 адресов.

D7-D0 – двунаправленная 8-разрядная шина данных. Служит для передачи одного байта данных в процессор, память и порты ввода-вывода. На адресной шине и шине данных используется положительная логика, т.е. единице соответствует высокий уровень напряжения.

ALE – разрешение адреса. Установка сигнала в "1" указывает о начале операции на интерфейсе и начале выдачи адреса микропроцессором. По отрицательному фронту сигнала ALE разрешается считывание адреса с адресной шины. При операциях ПДП линия неактивна.

# MEMR

– чтение из памяти. Используется два

запроса чтения данных из памяти. Поступает

с контроллера шины 8288 или с контроллера

ПДП 8237А Активный уровень сигнала низкий.

MEMR

– чтение из памяти. Используется два

запроса чтения данных из памяти. Поступает

с контроллера шины 8288 или с контроллера

ПДП 8237А Активный уровень сигнала низкий.

#MEMW – запись в память. По сигналу #MEMW данные с шины данных записываются в память. Поступает с контроллера шины 8288 или с контроллера ПДП 8237А. Активный уровень сигнала низкий.

#IOR – чтение из портов ввода-вывода. Низкий уровень сигнала чтения #IOR указывает, что на адресной шине выставлен адрес порта внешнего устройства, который должен выдать данные на шину данных. Сигнал поступает в порт с контроллера шины 8288 или с котроллера ПДП 8237А.

#IOW – запись в порты ввода-вывода. Низкий уровень сигнала записи #IOW указывает, что адресуемый порт внешнего устройства должен принять данные с шины данных. Сигнал поступает в порт с контроллера шины 8288 или с контроллера ПДП 8237А.

Группу линий прерывания составляют линии IRQ2-IRQ7 (запросы на прерывание от внешних устройств). Запросы поступают от внешних устройств в контроллер прерываний 8259А. При использовании интерфейса ISA-8 в ПК запросы имеют фиксированный приоритет после инициализации. Запрос IRQ2 имеет наивысший приоритет, запрос IRQ7 – наинизший. Предполагается, что источники запросов IRQ0 и IRQ1 находятся в системном устройстве ПК, т.е. подключаются не через разъемы расширения. Поэтому в состав линий прерывания интерфейса эти запросы не входят. Например, запрос на прерывание от таймера.

К группе линий управления ПДП относятся:

DRQ1-DRQ3 – линии сигналов запроса прямого доступа к памяти. Сигналы по этим линиям поступают от внешних устройств в контроллер ПДП 8237А и используются для организации внепроцессорных передач между памятью и внешними устройствами. Подобно линиям запросов на прерывание, в ПК запрос DRQ1 имеет наивысший приоритет, запрос DRQ3 – наинизший. Источник запроса DRQ0 находится в системном устройстве ПК. В ПК PC/XT запрос DRQ0 используется для регенерации динамической памяти.

#DACK0 – #DACK3 – линии сигналов подтверждения прямого доступа к памяти. Сигнал поступает в соответствующее внешнее устройство с контроллера ПДП, указывая, что запрос этого устройства принят и контроллер приступает к выполнению операции ПДП.

AEN – разрешение адреса ПДП. Высокий уровень сигнала отключает центральный процессор от интерфейса (линии адреса, данных и управления центрального процессора переходят в третье состояние). Сигнал можно использовать для блокировки устройств, которые не должны отвечать во время выполнения операции ПДП.

Т/С – завершение счета. Сигнал Т/С поступает с контроллера ПДП на внешнее устройство, сообщая ему, что блок данных заданного объема передан.

К группе линий общего назначения относятся:

RESET DRV – сброс. Сигнал сброса, высокий (активный) уровень которого появляется при включении питания или при нажатии кнопки сброса “RESET”, переводит все схемы в исходное состояние.

CLK - системная синхронизация. Сигнал предназначен для синхронизации работы процессора и устройств системы. Сигнал на линию интерфейса поступает с генератора тактовых импульсов 8284. В большинстве систем частота сигнала СLК равна 4,77 МГц.

ОSС - сигнал генератора. Сигнал поступает с выхода OSC тактового генератора. В ПК PC/XT частота сигнала ОSC равна 14,31818 МГц, скважность - 2. Сигнал предназначен для0 тактирования устройств, размещенных на платах расширения

I/О СН RDY - готовность каналов ввода-вывода. Сигнал готовности используется для увеличения длительности цикла интерфейса для медленнодействующих устройств. Низкий уровень этого сигнала (отсутствие готовности устройства) вводит дополнительные такты ожидания до перехода сигнала на высокий уровень (состояние готовности).

#I/О СН СК - ошибка канала ввода-вывода. Сигнал на линии #I/0 СН СК предназначен для контроля при передаче данных из памяти или через каналы ввода-вывода. Сигнал сообщает процессору о возникших ошибках, например, об ошибке при контроле на честность в блоке памяти.

Линии электропитания предназначены для подачи напряжений питания в устройства системы - -5В, +5В, -12В, + 12В и GND (земля).

Операции интерфейса, На интерфейсе ISA-8 могут выполняться следующие операции: обмен данными, прерывание, захват магистрали (передача данных в режиме ПДП). Операции обмена данными выполняются в режиме программного обмена и разделяются на четыре типа: запись в память; чтение из памяти; запись во внешний порт; чтение из внешнего порта. В этих операциях участвуют два устройства: задатчик (центральный процессор) и исполнитель (память или внешний порт).

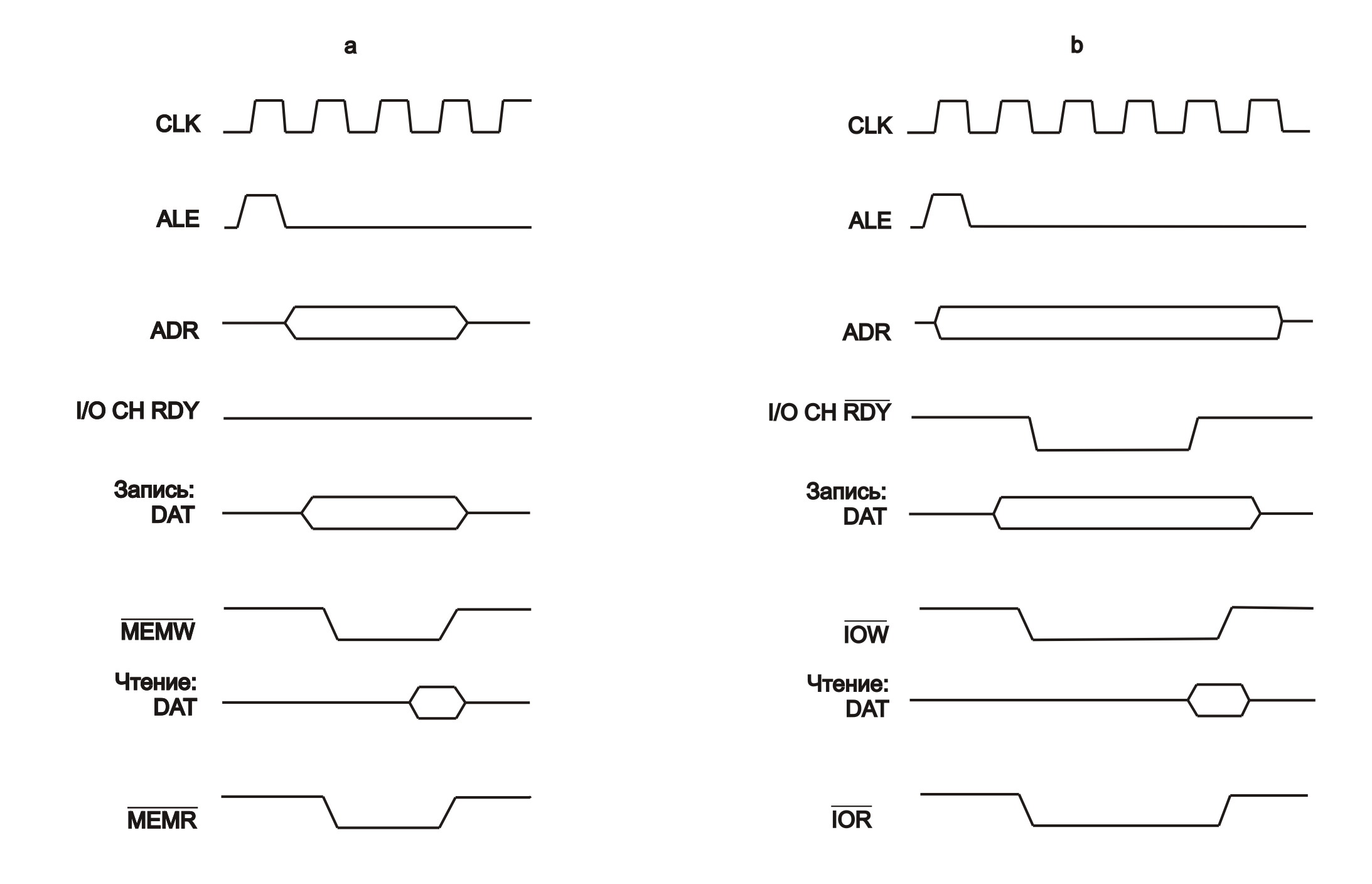

На рис.2.1,а и 2.1,б приведены временные диаграммы циклов обмена с памятью и внешним портом соответственно. Выполнение циклов синхронизируется тактовыми импульсами СLK. Циклы начинаются с выставления задатчиком сигнала ALE и адреса на линиях А0-А19 (при обмене с памятью) или А0-А15 (при обмене с внешними портами). Далее следует собственно команда записи или чтения. При выполнении цикла записи задатчик выставляет сигнал #МEMR (#IОR), в ответ на который исполнитель - память (внешний порт) выдает данные на шину данных (D0-D15). По окончании сигнала #МЕМR (#IOR) данные исполнителем снимаются. В цикле записи задатчик выставляет данные для передачи и сопровождает их сигналом записи #МЕМW (#IOW).

Как показано на рис. 2.1, а в циклах обмена с памятью сигнал готовности I/О СН RDY обычно неизменно активный. Поэтому такты ожидания отсутствуют. На рис 2.1,б приведены временные диаграммах циклов обмена с медленнодействующим внешним устройством. Выданный им низкий уровень сигнала I/О СН RDY свидетельствует о его неготовности к обмену. При этом вводятся два такта ожидания, в течение которых внешнее устройстве подготавливается к обмену.

При выполнении режима ПДП обмен данными производится между памятью и внешним устройством с возможным использованием сигнала готовности I/О СН RDY. Управляет обменом контроллер ПДП, а центральный процессор отключается от шин интерфейса (переходит в третье состояние).

Рис. 2.1. Временные диаграммы циклов обмена: а) с памятью и б) внешним портом

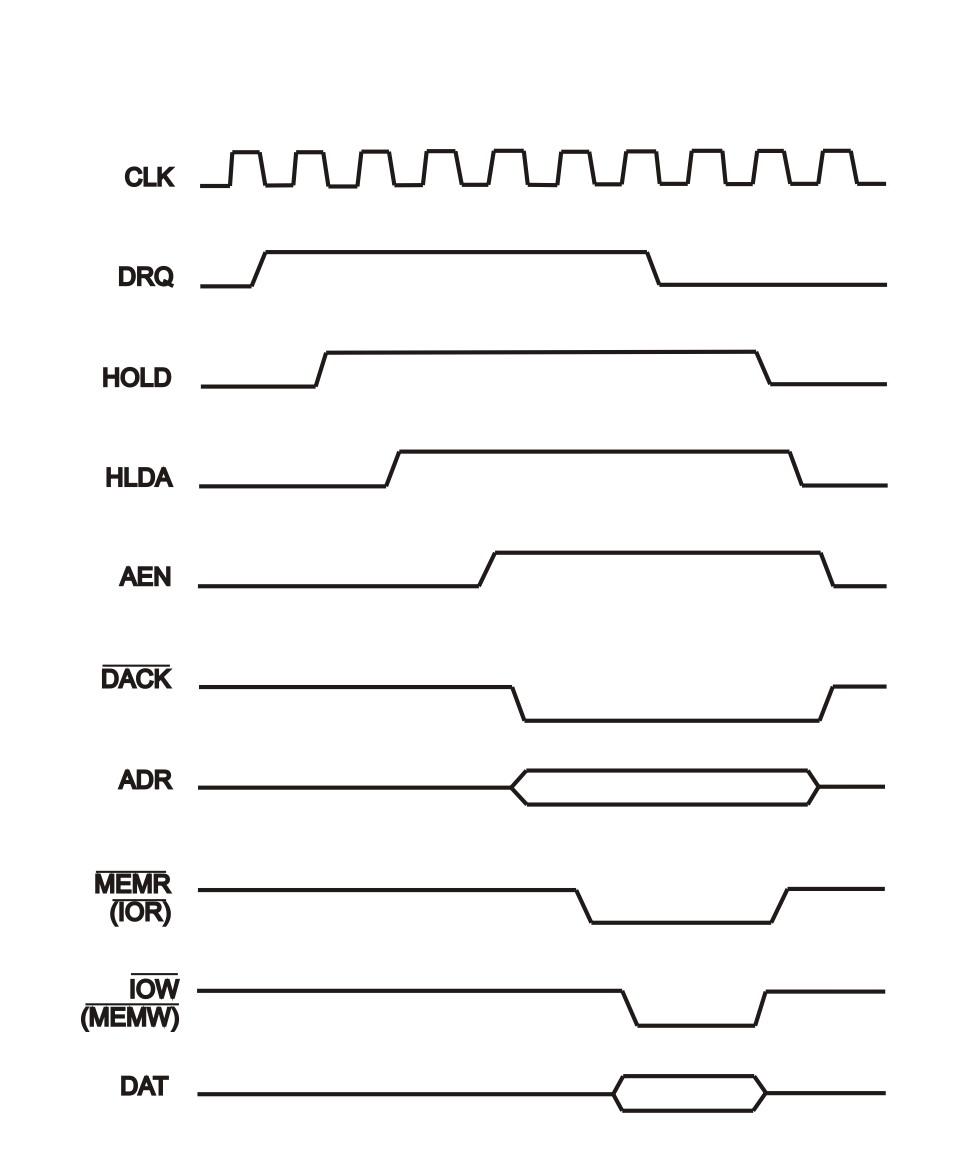

Временная диаграмма операции захвата магистрали (режим ПДП) приводится на рис.2.2.

Рис.2.2. Временная диаграмма операции захвата магистрали

Операция начинается с запроса ПДП от внешнего устройства, желающего произвести обмен с памятью, посылкой сигнала DRQ. Получив сигнал запроса захвата НОLD от контроллера ПДП, центральный процессор освобождает шины интерфейса, о чем сообщает сигналом НLDA. Затем выполняется непосредственно обмен данными в режиме ПДП в следующей последовательности:

1. Контроллер ПДП выдает на интерфейс сигнал АЕN, указывающий, что он взял управление обменом.

2. Контроллер ПДП посылает сигнал #DACK запросившему режим ПДП внешнему устройству, сообщая ему о начале обмена, и выставляет на адресную шину адрес ячейки памяти.

3. Контроллер ПДП выдает сигнал чтения #МЕМR или #IOR в зависимости от цикла обмена.

4. Источник передаваемых данных (память или внешнее устройство) в ответ на сигнал чтения выставляет свою информацию на шину данных.

5. Контроллер ПДП выдает сигнал записи #IOR или #МЕМR, по которому данные записываются в приемник данных.

6. После снятия запроса DRQ снимаются все управляющие сигналы и управление передается центральному процессору.

В операциях прерывания на интерфейсе используются только линии запросов на прерывание от внешних устройств IRQ2-IRQ7.