- •Задание на моделирование

- •Описания лабораторных работ. Лабораторная работа №1. Формирование памяти инструкций.

- •Задание на работу в лаборатории.

- •Лабораторная работа №2. Формирование устройства управления.

- •Задание на работу в лаборатории.

- •Лабораторная работа № 3. Формирование блока регистров.

- •Задание на работу в лаборатории.

- •Лабораторная работа № 4. Формирование блока арифметико-логического устройства (алу).

- •Задание на работу в лаборатории.

- •Лабораторная работа № 5. Построение простейшего risc-процессора.

- •Задание на работу в лаборатории.

Лабораторная работа №2. Формирование устройства управления.

Цель работы. Получение представления о дешифрации потока инструкций в RISC-процессоре.

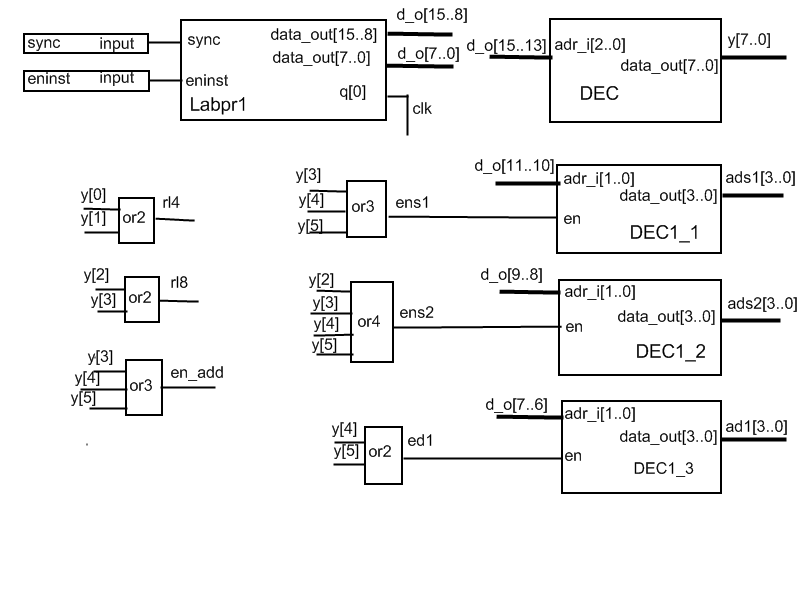

Постановка задачи. Необходимо построить устройство, посылающее сигналы управления на исполнительный блок. Из структуры кода команды следует. Что такое устройство должно иметь основной дешифратор на 3 адресных входа, куда поступает код операции, и дешифраторы адресов источников и приемников. Эти дешифраторы будут иметь по два адресных входа и вход управления подключением, управляемый основным дешифратором. Так как команда пересылки MOV R(s),R(d) исполняется по принципу: R(d)<=R(s) + R(0), то для такой команды необходимы два источника: регистр нуля и регистр общего назначения. Кроме того, два источника могут понадобиться и для случая использования команды сложения двух операндов с занесением результата в третий регистр: ADD R(s1),R(s2),R(d). Поэтому договоримся, что два дешифратора определяют источники по разрядам кода Р11,Р10 и Р9,Р8; а один дешифратор определяет приемник по разрядам кода Р7,Р6. В случае, когда команда имеет только один операнд – источник, приемник определяется по разрядам Р9,Р8, т.е. с помощью дешифратора второго источника.

Основной дешифратор управляет также выводом операнда данных на внутреннюю шину данных, а адресного операнда на позиции, определяющие адрес в пространстве памяти данных, а для команд сложения при любой адресации и переноса с регистровой адресацией формирует сигнал активизации АЛУ (выход en_add).

Задание на работу в лаборатории.

Открыть свою папку в пакете Quartus II и создать в ней проект для лабораторной работы №2. Проекты всех лабораторных работ должны находиться в единой папке.

Открыть VHDL-файл и записать в него текст прогр.2.1 для дешифратора на 3 входа . Сохранить файл под именем dec и установить его приоритет.

Откомпилировать файл программы и проверить с помощью временных диаграмм. На диаграммах установить интервалы adr_i 20ns, 40ns и 80ns соответственно. Создать библиотечный модуль файла dec.vhd.

Открыть VHDL-файл и записать в него текст прогр.2.2 для дешифратора на 2 входа. Сохранить файл под именем dec1 и установить его приоритет.

Откомпилировать файл программы и проверить с помощью временных диаграмм. На диаграммах установить интервалы adr_i 20ns и 40ns соответственно. Создать библиотечный модуль файла dec1.vhd.

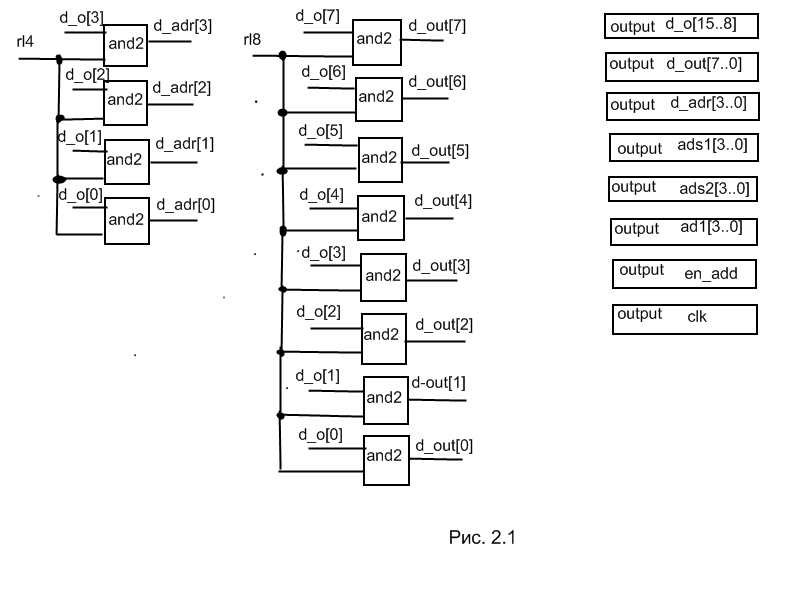

Открыть файл графического редактора и построить в нем схему рис.2.1, используя модули дешифраторов, модуль, полученный в результате работы № 1 и простую логику. Сохранить файл под именем проекта и установить его приоритет.

Откомпилировать файл и проверить с помощью временных диаграмм. На диаграммах установить интервалы: sync =20ns, eninst=400ns. Продемонстрировать диаграммы преподавателю. Создать библиотечный модуль файла.

Отчет должен содержать: схему блока – рис.2.1, программы для дешифраторов; временную диаграмму работы блока. Отчет представлять совместно с отчетом по лабораторной работе № 1.

Прогр.2.1

library ieee;

use ieee.std_logic_1164.all;

entity dec is

port(

adr_i: in bit_vector(2 downto 0);

data_out: out bit_vector(7 downto 0)

);

end dec;

architecture BBB of dec is

begin

p0: process (adr_i)

begin

case adr_i is

when "000"=>data_out<="00000001";

when "001"=>data_out<="00000010";

when "010"=>data_out<="00000100";

when "011"=>data_out<="00001000";

when "100"=>data_out<="00010000";

when "101"=>data_out<="00100000";

when "110"=>data_out<="01000000";

when "111"=>data_out<="10000000";

end case;

end process;

end ;

Прогр.2.2

library ieee;

use ieee.std_logic_1164.all;

entity dec1 is

port(

adr_i: in bit_vector(1 downto 0);

en: in bit;

data_out: out bit_vector(3 downto 0)

);

end dec1;

architecture BBB of dec1 is

begin

process (adr_i)

begin

if (en = '1') then

data_out(0)<=(not(adr_i(0)))and(not(adr_i(1)));

data_out(1)<=(adr_i(0))and(not(adr_i(1)));

data_out(2)<=(not(adr_i(0)))and(adr_i(1));

data_out(3)<=(adr_i(0))and(adr_i(1));

elsif (en ='0') then

data_out(3 downto 0)<="0000";

end if;

end process;

end ;