Сапр зв Лекція № 4

Проектування вузлів вимірювання часових параметрів сигналів.

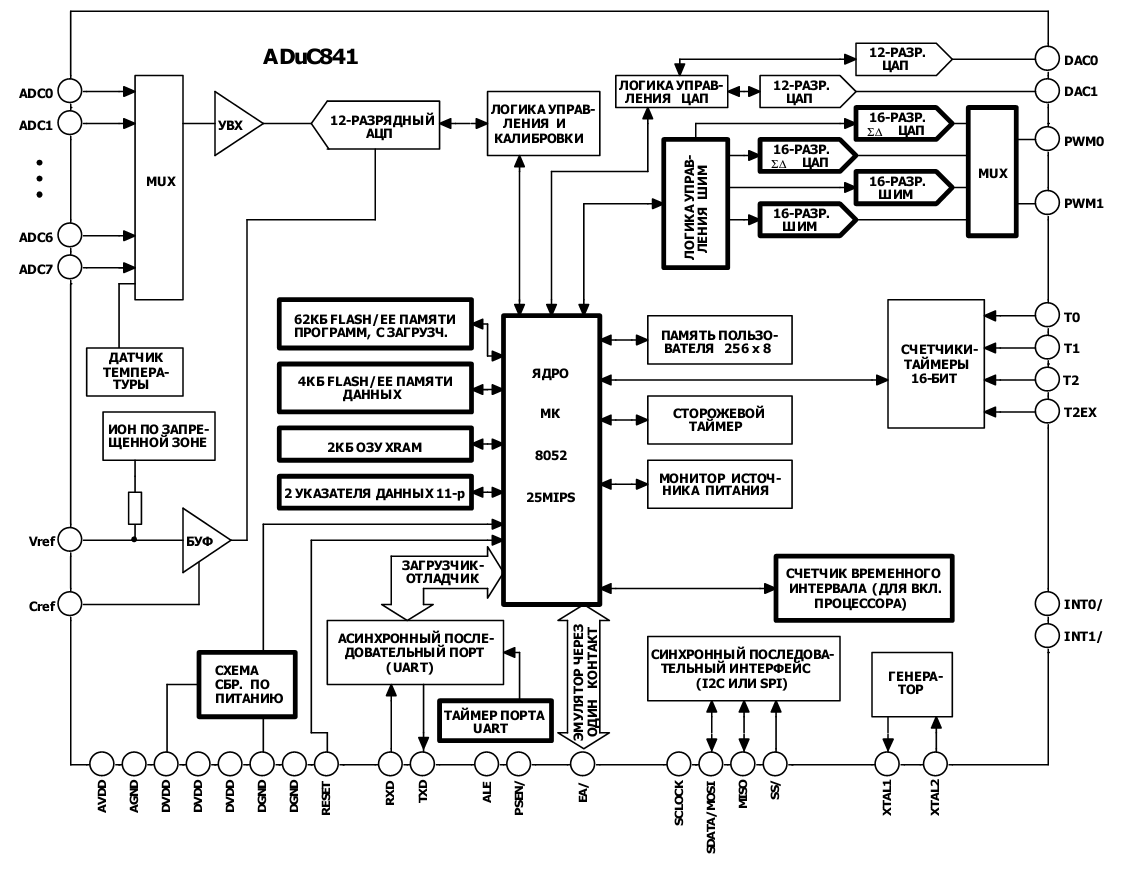

Структура і режими роботи таймерів ОЕОМ сімейства MCS51.

Задання часових iнтервалiв i пiдрахунку зовнiшньої частоти.

У типових задачах, які розв'язують мікроконтролери, часто виникає необхідність, наприклад, визначити час між двома подіями або ініціювати одну подію через заданий час відносно деякого другого. У цих і подібних їм випадках кажуть про необхідність реалізації мікроконтролером часових функцій. Вирішують такі завдання, використовуючи важливий елемент архітектури процесора — блок таймерів/лічильників.

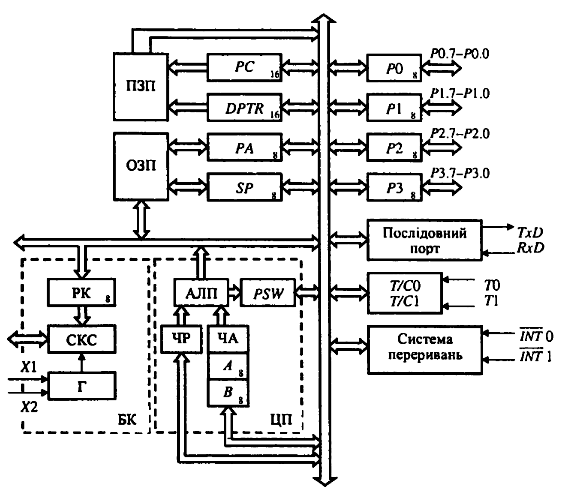

Рисунок 2.1 — Внутрішня структура МК сімейства MCS-51

Регістри TH0, TL0, TH1, TL1; (+TH2, TL2) (Timer/counter Low (High) byte).

Регістр TMOD (Timer/counter Mode). Найменування й призначення розрядів регістра TMOD наведено в табл.2.4. Усі розряди цього регістра доступні для записування і читання.

При

роботі в режимі таймера вміст T/Cj

![]() інкрементується з частотою

інкрементується з частотою

![]() ,

де f є частота синхронізації мікроконтролера.

,

де f є частота синхронізації мікроконтролера.

При роботі T/Cj в режимі лічильника зовнішніх подій, його вміст інкрементується у відповідь на перехід з "1" у "0" сигналу на j-ом рахунковому вході мікроконтролера.

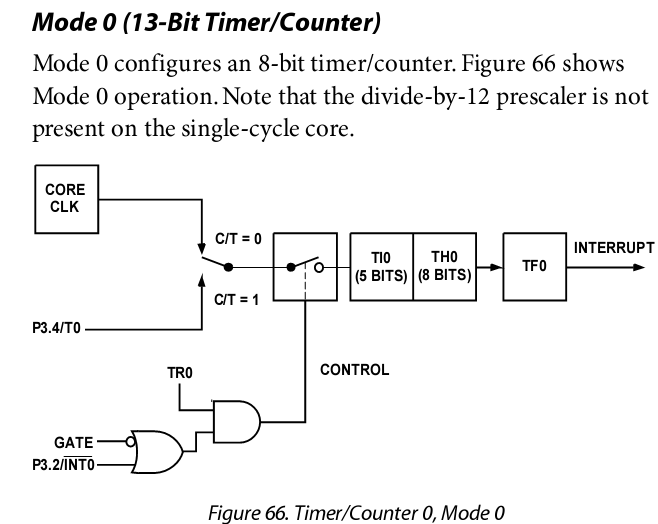

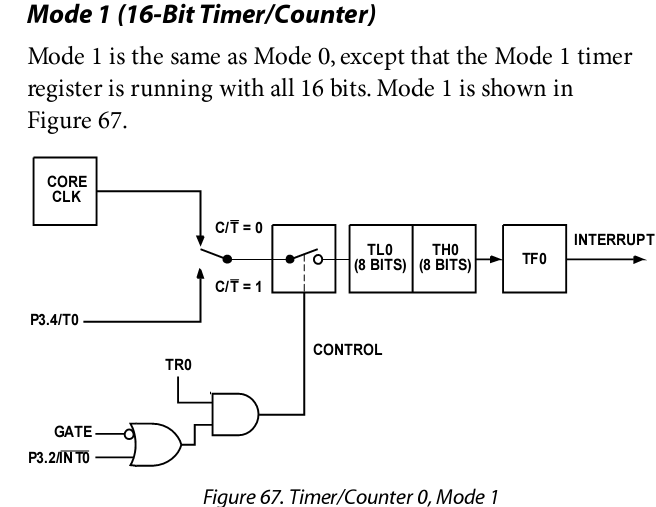

Реж. 0,1: Таймер/лічильник T/Cj у режимі 0 (1) являє собою пристрій на основі 13- (16-) розрядного регістра, що складається з 8-ми розрядів регістра THj і 5-ти молодших розрядів (8-ми розрядів) регістра TLj.

Реж. 2: T/Cj 8-розрядного лічильник (TLj) з автоперезавантаженням.. При кожному переповненні TLj, крім установки в регістрі TCON прапора TFj, відбувається автозавантаження регістра TLj вмістом THj, причому зазначене автозавантаження не впливає на вміст регістра THj.

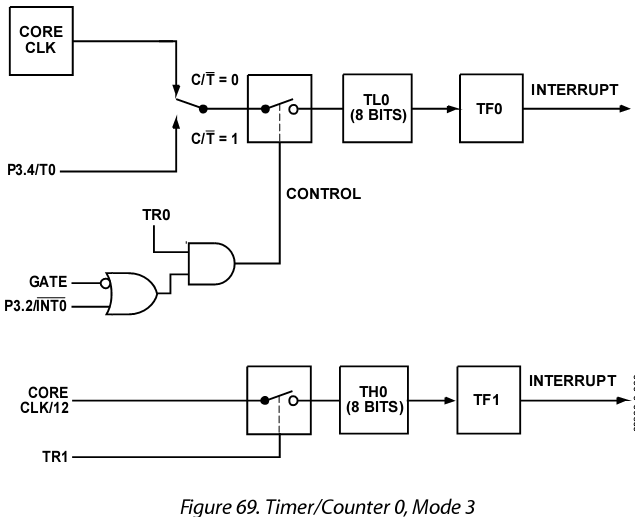

Реж. 3: Таймер/лічильник T/C1 у режимі 3 заблокований (значення коду в регістрах TH1, TL1 не змінюється). Ефект такий же, як при скиданні TR1 у "0". Таймер/лічильник T/C0 у режимі 3 являє собою два незалежних пристрої на основі регістрів TH0 і TL0. Пристрій на основі TL0 може працювати в режимі таймера чи в режимі лічильника і при переповненні встановлює прапор TF0. Він використовує біт увімкнення TR1, при переповненні виставляє прапор TF1. Інших бітів керування пристрій на основі TH0 не має.

Таблиця 2.4 — Найменування і призначення розрядів регістра TMOD

Біти |

Назва |

Призначення |

|||||

7 |

GATE1 |

Біт

дозволяє (забороняє) керувати T/C1 від

зовнішнього виводу

GATE1=1 – керування дозволене. GATE1=0 – керування заборонене |

|||||

6 |

|

Біт визначає роботу T/C1 в режимі таймера ( =0), лічильника зовнішніх подій ( =1) |

|||||

5 4 |

М1.1 М0.1 |

Біти визначають один з 4-х режимів роботи T/C1. |

|||||

|

|

|

M1.1 |

M0.1 |

Режим |

|

|

|

|

|

0 |

0 |

0 |

|

|

|

|

|

0 |

1 |

1 |

|

|

|

|

|

1 |

0 |

2 |

|

|

|

|

|

1 |

1 |

3 |

|

|

3 |

GATE0 |

Біт

дозволяє (забороняє) керувати T/C0 від

зовнішнього виводу

GATE0=1 – керування дозволене. GATE0=0 – керування заборонене |

|||||

2 |

|

Біт визначає роботу T/C0 як таймер ( =0), лічильника зовнішніх подій ( =1) |

|||||

1 0 |

М1.0 М0.0 |

Біти визначають один з 4-х режимів роботи T/C0. |

|||||

|

|

|

M1.0 |

M0.0 |

Режим |

|

|

|

|

|

0 |

0 |

0 |

|

|

|

|

|

0 |

1 |

1 |

|

|

|

|

|

1 |

0 |

2 |

|

|

|

|

|

1 |

1 |

3 |

|

|

Регістр TCON (Timer/counter Control). Найменування й призначення розрядів регістра TCON наведено в табл.2.3. Усі розряди цього регістра доступні для записування і читання.

Таблиця 2.3 — Найменування й призначення розрядів регістра TCON

Біти |

Назва |

Призначення |

7 |

TF1 |

Прапор переповнення T/C1 |

6 |

TR1 |

Біт увімкнення T/C1 TR1=1 - увімкнений, TR1=0 - вимкнений |

5 |

TF0 |

Прапор переповнення T/C0. |

4 |

TR0 |

Біт увімкнення T/C0 TR0=1 - увімкнений, TR0=0 - вимкнений |

3 |

IE1 |

Прапор запиту зовнішнього переривання |

2 |

IT1 |

Біт, що визначає вид переривання . IT1=0 - переривання за рівнем (низьким), IT1=1 - переривання за фронтом (перехід з"1" у "0") |

1 |

IE0 |

Прапор запиту зовнішнього переривання . |

0 |

IT0 |

Біт, що визначає вид переривання . IT0=0 - переривання за рівнем (низьким), IT0=1 - переривання за фронтом (перехід з"1" у "0") |

TC2

У системах автоматичного керування часто доводиться вимірювати такі величини, як частота f, період T, тривалість , зсув фаз . Для цього застосовують перетворення частота–код. Залежно від того, який саме параметр потрібно виміряти, застосовують різний підхід.

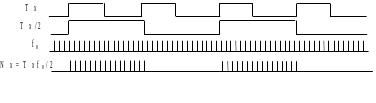

Рисунок 16. Вимірювання частоти fx

При вимірюванні частоти fx використовують підрахунок імпульсів вхідного сигналу протягом фіксованого проміжку часу, рис. 16.

Такий метод прийнятний для вимірювання високих частот понад 100 Гц. Верхня межа обмежується швидкодією елементів схеми і розрядністю лічильників.

Вимірювання частот нижче 100 Гц замінюють вимірюванням періоду Тх. При цьому здійснюють підрахунок імпульсів фіксованої частоти f0 за інтервал, що дорівнює або кратний вимірюваному періоду (рис.17).

У такий самий спосіб вимірюють тривалість імпульсу х, відмінність полягає лише в тому, що при вимірюванні тривалості імпульсу не треба ділити частоту на 2.

Рисунок 17. Вимірювання періоду проходження методом підрахунку кількості імпульсів відомої частоти

При вимірюванні зсуву фаз часовий інтервал формують шляхом кон’юнкції сигналів f1x і f2x (рис.18), отриманий часовий інтервал вимірюють методом, описаним вище. Схеми, що реалізують такий алгоритм, зображено на рисунку 19.

Рисунок 18. Вимірювання зсуву фаз

Рисунок 19. Схеми для вимірювання частоти: а) низької; б) високої

У лабораторному стенді за наявності плати розширення до входу ОЕОМ Т0 під’єднаний постійний генератор частоти, а до входу Т1 – генератор зі змінною частотою. Сигнали цих генераторів можна спостерігати на осцилографі, під’єднаному до BNC роз’єму. Для спостереження сигналу Т0 замкнути перемичку J1, а для Т1 – перемичку J3.

Таймери/лічильники (Т/С) ОЕОМ призначені для підрахунку зовнішніх подій, отримання програмно керованих тимчасових затримок, виконання часозадаючих функцій ОЕОМ.

До складу блока Т/С входять:

1) два 16-розрядних регістри Т/С0, Т/С1;

2) 8-розрядний регістр режимів Т/С (ТМ0D);

3) 8-розрядний регістр керування (ТСОN);

4) схема інкремента;

5) схема фіксації INT0, INT1, Т0, Т1;

6) схема керування прапорцями;

7) логіка керування Т/С.

Два 16-розрядних регістри Т/С0 і Т/С1 виконують функцію збереження вмісту рахунку. Кожен із них складається з пари 8-розрядних регістрів, відповідно ТH0, ТL0 і ТH1, ТL1. Причому регістри ТН0,ТH1 – старші, регістри ТL0,ТL1 – молодші 8 розрядів. Кожен з 8-розрядних регістрів може бути використаний як РЗП, якщо Т/С не використовуються (біт TR0 для Т/С0 і біт TR1 для Т/С1 у регістрі керування TCON дорівнює "0").

Регістр режимів Т/С (TMOD) призначений для приймання і збереження коду, що визначає:

- один із 4-х можливих режимів роботи кожного Т/С;

- роботу в якості таймерів чи лічильників;

- керування Т/С від зовнішнього виводу.

Р

M0-M1(0-1,4-5) – один із 4-х режимів лічильників;

С/Т(2,6) – '0' таймер, '1' лічильник;

GATE – дозвіл керування від зовнішнього виводу '0' заборонено, '1' дозволено (INT0,INT1).

Регістр керування (TCON) призначений для приймання і збереження коду керуючого слова. Регістр TCON не можна використовувати в якості РЗП. Схема інкременту призначена для збільшення на 1 у кожному машинному циклі вмісту регістрів Т/С0, Т/С1, для яких:

- встановлений режим таймера і рахунок дозволений;

- встановлений режим лічильника, рахунок дозволений і на відповідному вході схеми Т0 (для Т/С0) чи Т1 (для Т/С1) зафіксований лічильний імпульс у попередньому машинному циклі.

Регістр керування TCON:

TR – біт увімкнення Т/С, '0' вимкнений;

TF – прапор переповнення Т/С;

IT – визначає вид переривання INT ‘0’ – по низ. рівню, ’1’ – по фронту;

IE – прапор запиту на переривання.