- •1.Последовательный односторонний ограничитель

- •Переходные процессы.

- •2.Паралельные диодные ограничения

- •Выходной сигнал диодного ао имеет искаженную форму из–за с0.

- •Стремятся, чтобы Сд и Rпр были как можно меньше (выбирают специальные быстродействующие импульсные диоды у которых Сд и Rпр малы).

- •Для уменьшения времени фронта необходимо увеличивать амплитуду включающего тока.

- •Для уменьшения времени рассасывания необходимо уменьшать амплитуду включающего тока до величины тока базы насыщения и увеличивать амплитуду выключающего тока.

- •Для уменьшения времени спада необходимо увеличивать амплитуду выключающего тока.

- •Для сложения двух многоразрядных двоичных чисел на каждый разряд необходим один sm и только в младшем разряде можно обойтись hs.

- •Аппаратная сложность и быстродействие сумматора являются очень важными параметрами. Поэтому разработано множество вариантов сумматоров, которые имеют разветвленную классификацию.

- •Перечислим основные типы сумматоров:

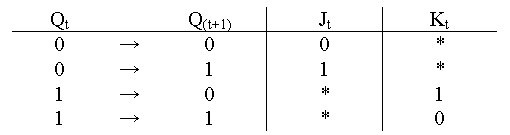

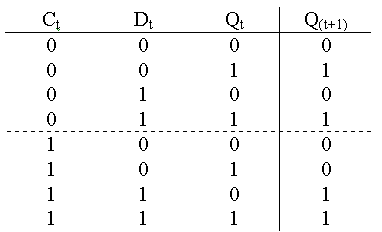

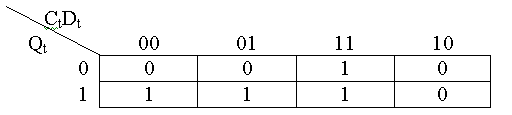

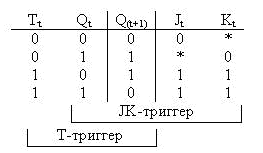

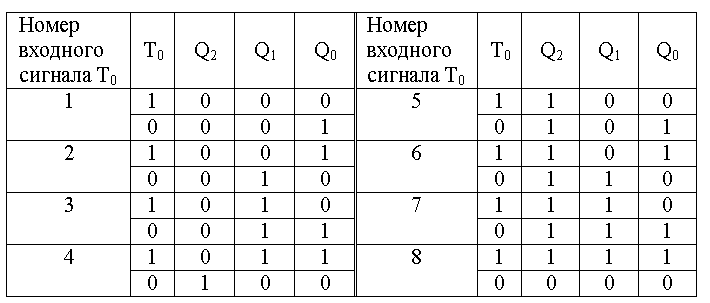

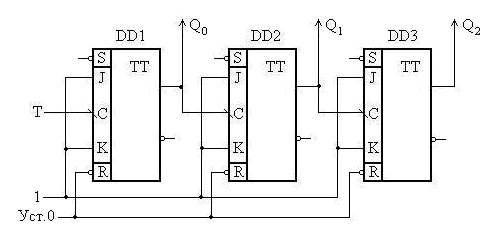

- •Составим таблицу состояний проектируемого счетчика на основе синхронных jk–триггеров*. При заполнении таблицы учитывают таблицу переходов jk–триггера (слайд 5).

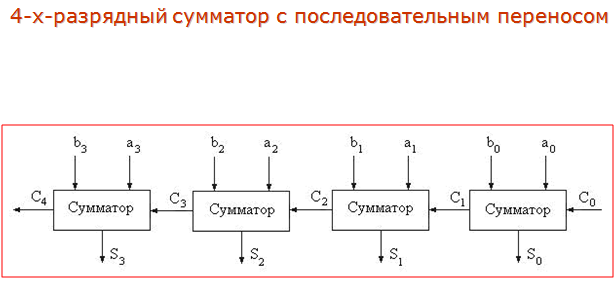

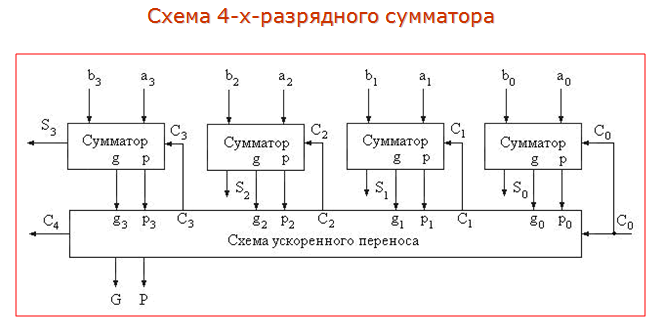

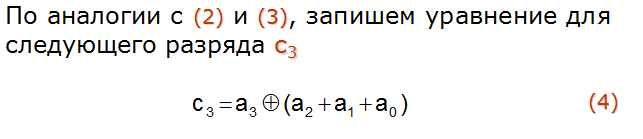

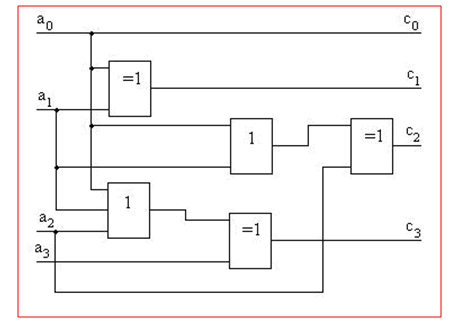

При построении многоразрядного сумматора для каждого разряда необходима логическая схема с тремя входами ai, bi, Ci и двумя выходами Si, Ci+1. Такая схема и есть полный сумматор (SM), который можно реализовать с помощью двух полусумматоров (HS).

Для сложения двух многоразрядных двоичных чисел на каждый разряд необходим один sm и только в младшем разряде можно обойтись hs.

Вывод

Время выполнения операции в сумматоре с последовательным переносом намного больше времени сложения в одноразрядном сумматоре. Действительно, сигнал переноса С4 только тогда может принять истинное значение, когда последовательно будут установлены правильные значения С1, С2, С3. Поэтому такой порядок выполнения операций называется последовательным переносом (Ripple Carry).

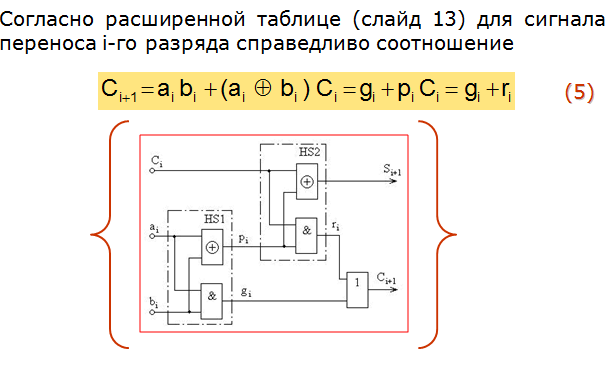

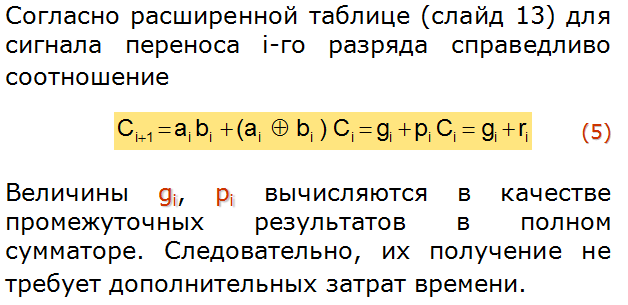

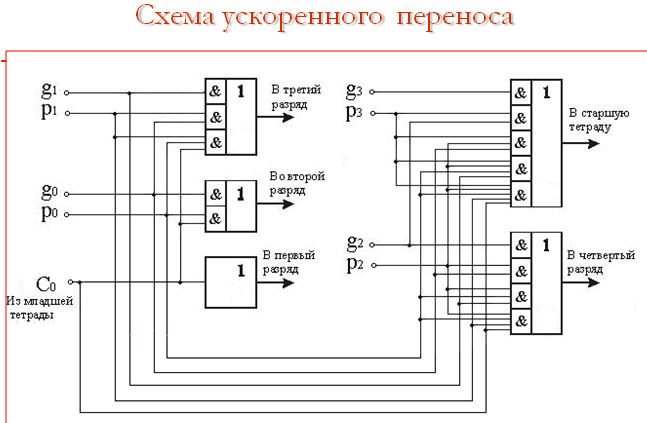

Для уменьшения времени операции сложения многоразрядных чисел используют схемы параллельного переноса (Carry look-ahead). При этом все сигналы переноса вычисляются непосредственно по значениям входных переменных.

№38Многоразрядный сумматор с параллельным переносом.

Для уменьшения времени операции сложения многоразрядных чисел используют схемы параллельного переноса (Carry look-ahead). При этом все сигналы переноса вычисляются непосредственно по значениям входных переменных.

Смысл величин gi, pi, ri

Сигнал gi называют функцией генерации переноса. Он вырабатывается тогда, когда в данном разряде перенос происходит из-за комбинации входных переменных ai,bi.

Сигнал рi ¾ функция четности. Он вырабатывается тогда, когда на входах ai и bi присутствует нечетное число единиц.

Сигнал ri называется функцией распространения переноса. Он показывает, передается ли полученный в младшем разряде сигнал переноса Ci дальше.

Вывод

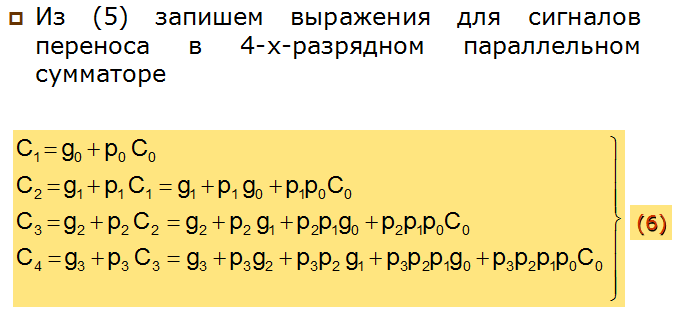

Хотя выражения (6) достаточно сложные, время формирования сигнала переноса в любой разряд с помощью вспомогательных функций определяется только временем задержки распространения сигнала на двух элементах.

Функции (6) реализуются специальным КУ — схемой ускоренного переноса (СхУП).

Аппаратная сложность и быстродействие сумматора являются очень важными параметрами. Поэтому разработано множество вариантов сумматоров, которые имеют разветвленную классификацию.

Перечислим основные типы сумматоров:

одноразрядный сумматор;

сумматор для последовательных операндов;

сумматор для параллельных операндов с последовательным переносом;

сумматор для параллельных операндов с параллельным переносом;

накапливающий сумматор.

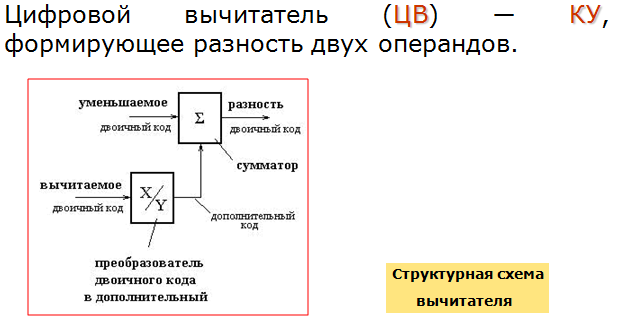

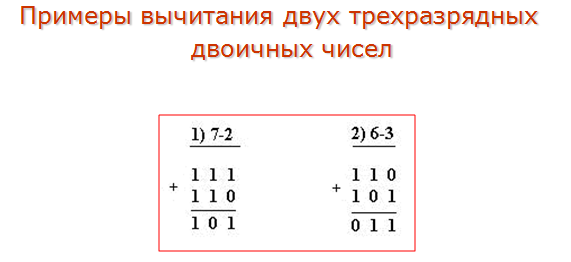

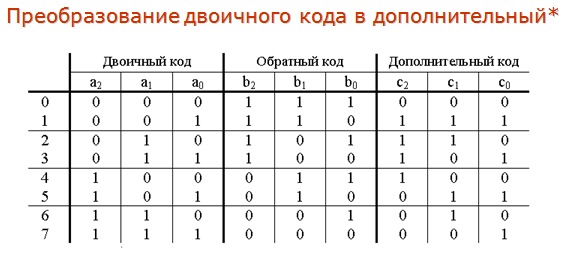

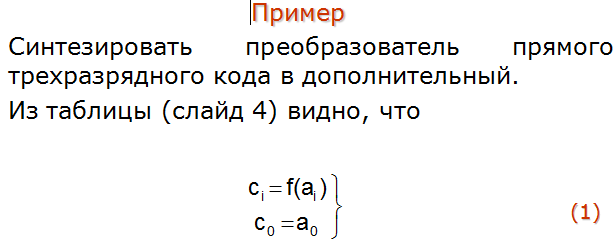

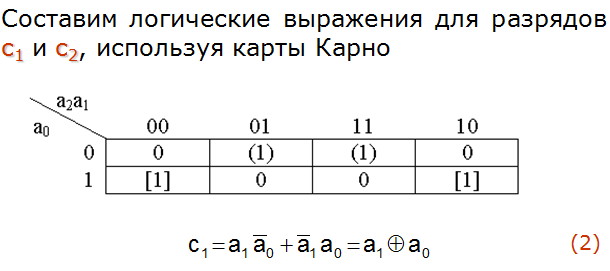

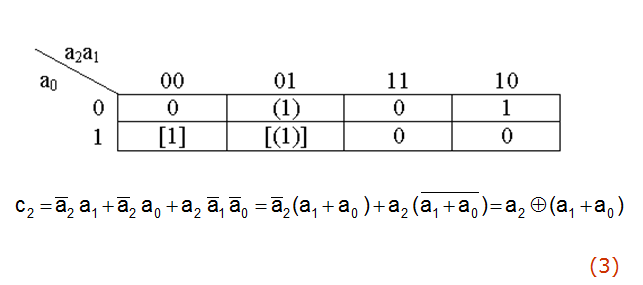

№39Цифровой вычитатель. Порядок построения преобразователя кода.

№40Цифровой компаратор.

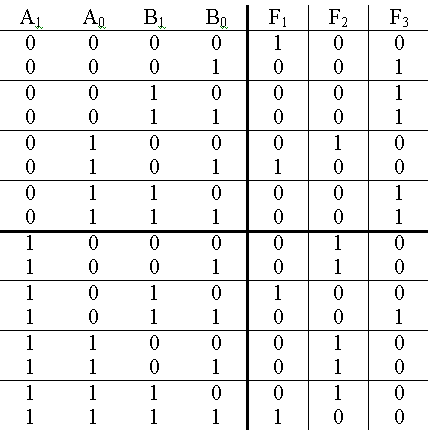

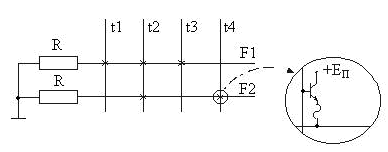

Цифровым компаратором называется КУ, осуществляющее сравнение двух операндов. Его аббревиатура "СП". Применяется СП в информационно ― измерительных системах и процессорах. Операция сравнения двух напряжений может быть также реализована на аналоговом компараторе.

Таблица истинности СП*

Функции F1, F2, F3 принимают единичные значения при выполнении следующих условий:

F1=1, если Ai=Bi [критерий равенства],

F2=1, если Ai>Bi

F1=1, если Ai<Bi.

Составим логические выражения для функций F1, F2, F3 , используя карты Карно.

Вывод

Выражения (4)…(6) позволяют осуществить синтез цифрового компаратора в заданном базисе на основе простейших логических элементов.

№41Арифметико-логическое устройство.

АЛУ предназначено для выполнения арифметических, логических и арифметико-логических операций*.

По своим функциям АЛУ является операционным блоком, выполняющим микрооперации, обеспечивающие прием из других устройств операндов (например из ОЗУ**), их преобразование и выдачу результатов преобразования в другие устройства.

Классификация АЛУ

По способу действия над операндами различают АЛУ параллельного и последовательного действия.

По способу представления чисел выделяют АЛУ для чисел с фиксированной и плавающей запятой, для десятичных чисел.

По способу организации работы АЛУ подразделяются на синхронные и асинхронные*.

Классификация АЛУ (продолжение)

По характеру использования элементов и узлов АЛУ делятся на универсальные* и функциональные.

В универсальных АЛУ операции для всех форм представления чисел выполняются одними и теми же схемами.

В функциональных АЛУ операции над операндами с фиксированной и плавающей запятой, с десятичными числами и логическими переменными осуществляются в отдельных операционных блоках.

По связи с ОЗУ различают АЛУ с непосредственной и магистральной связями.

В АЛУ с непосредственной связью схемы управления передачей информации соединены непосредственно с выходами соответствующих регистров. При этом операнды, участвующие в конкретных микрооперациях, считываются из одних регистров, а в других образуются результаты.

В АЛУ с магистральной структурой схемы для преобразования информации выделены в отдельный блок, а регистры служат лишь для хранения операндов.

№42Программируемая логическая матрица (ПЛМ). Схема ПЛМ. Информационная емкость.

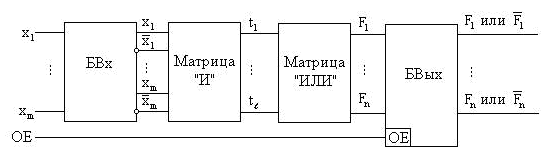

ПЛМ появились в середине 70-х годов прошлого века. Основой их служит последовательность программируемых матриц элементов «И», «ИЛИ». В структуру ПЛМ входят также блоки входных и выходных буферных каскадов (БВх) и (БВых).

Входные буферы формируют сигналы необходимой мощности для питания матрицы элементов «И».

Выходные буферы обеспечивают необходимую нагрузочную способность выходов, разрешают или запрещают выход ПЛМ на внешние шины с помощью сигнала ОЕ.

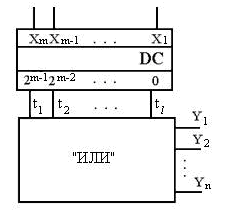

Основными параметрами ПЛМ являются число входов m, число термов l и число выходов n.

Базовая структура ПЛМ

Переменные подают через БВх на входы элементов «И» (конъюнкторов), и в матрице «И» образуются l термов*.

Число формируемых термов равно числу конъюнкторов или числу выходов матрицы «И».

Термы подаются на входы матрицы «ИЛИ», т.е. на входы дизъюнкторов, формирующих выходные функции.

Число дизъюнкторов равно числу вырабатываемых функций n.

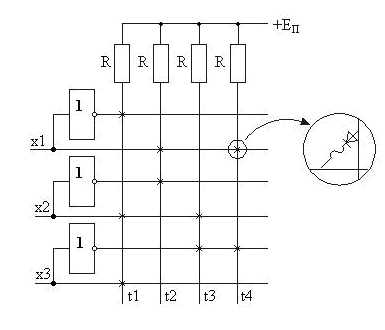

Матричные схемы представляют собой сетку ортогональных проводников, на местах пересечения которых установлены элементы односторонней проводимости (ЭОП) (диоды, транзисторы).

Таким образом, ПЛМ реализуют дизъюнктивную нормальную форму (ДНФ) воспроизводимых функций (двухуровневую логику).

ПЛМ способна реализовать систему n логических функций от m аргументов, содержащую не более l термов.

Воспроизводимые функции являются комбинациями из любого числа термов, формируемых матрицей «И». Какие именно функции будут выработаны и какие комбинации этих термов составят выходные функции, определяется программированием ПЛМ.

Функциональная схема матрицы «И» (Пример*)

Матрица в рассматриваемом примере может реализовать четыре конъюнкции (по числу ортогональных проводников), например:

![]()

![]()

В общем случае, если какие-либо ортогональные проводники не участвуют в реализации конъюнкций, их число может быть меньше l.

Реализация необходимых конъюнкций осуществляется путем прожига перемычек (включенных последовательно с полупроводниковым диодом), расположенных на местах пересечения ортогональных проводников и не участвующих в образовании конъюнкций.

В исходном состоянии на всех пересечениях проводников матрицы «И» имеются соединения, т.е. матрица реализует все конъюнкции переменных, причем в каждую конъюнкцию входят все переменные и с отрицанием, и без него. Очевидно, что такие конъюнкции логического смысла не имеют. Для получения необходимых конъюнкций следует прожигать все легкоплавкие перемычки, находящиеся на узлах, не участвующих в конъюнкциях.

Функциональная схема матрицы «ИЛИ»

Схема матрицы дизъюнкции содержит сопротивления нагрузки и транзисторные ключевые соединители (на местах пересечений ортогональных проводников).

Пример

Матрица «ИЛИ», изображенная на слайде 11, реализует две дизъюнкции (с учетом (1))

![]()

![]()

Информационная емкость матрицы

Объем информации, который можно записать в матричную схему, определяется как информационная площадь (емкость) матриц

№43Постоянные запоминающие устройства (ПЗУ). Функциональная схема ПЗУ. Масочные, программируемые и репрограммируемые ПЗУ.

ПЗУ состоят из матриц «ИЛИ» и полного дешифратора.

ПЗУ ― это элемент (устройство) памяти, позволяющий хранить записанную в нем информацию после выключения напряжения источника питания.

По способу записи ПЗУ подразделяются на масочные, программируемые и репрограммируемые.

Масочные ПЗУ программируются заводом–изготовителем с помощью специальных масок, т.е. соединения на местах пересечения ортогональных проводников заложены в технологию производства ПЗУ.

Программируемые ПЗУ (ППЗУ). ППЗУ выпускаются заводом–изготовителем в «чистом виде», т.е. по всем адресам записаны «нули». Программирование ППЗУ осуществляется пользователем на специальной установке, называемой программатором. В ППЗУ можно записать информацию (запрограммировать его) только один раз. Изменить записанную информацию или исправить ее нельзя. ППЗУ нашли широкое применение в ЭВМ для хранения запускающих программ. Они обладают большим быстродействием, чем репрограммируемые ПЗУ (РПЗУ).

Репрограммируемые ПЗУ (РПЗУ) позволяют перепрограммировать ПЗУ, т.е. стереть ранее записанную информацию и записать новую. По способу стирания ранее записанной информации РПЗУ бывают с ультрафиолетовым (ультрафиолетовыми лучами) и электрическим стиранием.

РПЗУ позволяют многократно (до 1000 раз) перепрограммировать и сохранять записанную информацию десятки и сотни тысяч часов.

Быстродействие РПЗУ несколько хуже быстродействия ППЗУ.

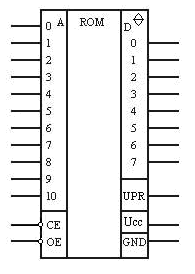

Структура ПЗУ

Структурная схема ПЗУ содержит дешифратор на m входов и 2m выходов, а также матрицу «ИЛИ».

Информационная емкость ПЗУ определяется как Sпзу = 2m, где m ― количество входов х.

В этом определении емкости (объема) памяти не учтено количество выходов ПЗУ n. Обычно n равно 4, 8 или 16 (полубайтовая, байтовая и двухбайтовая организация памяти). Тогда «битовая» емкость ПЗУ определяется как

Sпзу (бит) = 2m n (бит).

Пример

Р ПЗУ

с ультрафиолетовым стиранием К573РФ2 *

ПЗУ

с ультрафиолетовым стиранием К573РФ2 *

Обозначения на схеме РПЗУ

А ― адресные входы;

D ― информационные выходы.

UPR ― вход подачи напряжения записи (в режиме хранения на этот вход подается Ucc);

Ucc ― вывод для подачи напряжения питания.

СЕ и ОЕ ― входы управления состоянием выводов, если СЕ=ОЕ=1, входы D имеют высокоимпедансное состояние. При СЕ=ОЕ=0 вывод информации разрешен.

Микросхема РПЗУ К573РФ2 (РФ5) имеет одиннадцатиразрядный дешифратор, выходы которого соединены с восьмиразрядной матрицей «ИЛИ».

В процессе записи выходные элементы РПЗУ находятся в режиме приема информации через выводы D0 ... D7 (на входе «ОЕ» уровень «1»). В режиме считывания записанной информации выводы «UPR» и «Ucc» объединяются и на них подается напряжение питания +5В.

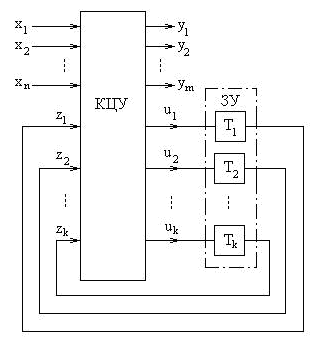

№44Математическая модель и общая структурная схема последовательного цифрового устройства.

Последовательностные цифровые устройства (ПЦУ) иначе называют цифровыми автоматами или автоматами с памятью (АП). Для описания АП применяют различные математические модели.

Наиболее часто в электронике применяют модель конечного* автомата (КА)

КА преобразует слова входного алфавита X в слова выходного алфавита Y .

КА имеет один вход и один выход. В любой момент дискретного времени t*, находясь в некотором состоянии s(t)ÎS** он способен воспринимать букву входного алфавита х(t)ÎХ, преобразуя ее в букву выходного алфавита y(t)ÎY.

Задается КА в виде алгебраической системы

А=áX, Y, S, s0, j, yñ, (1)

где s0=S(0) ¾ начальное состояние КА;

j ¾ функция переходов КА;

y ¾ функция выходов КА.

Функции переходов

![]()

и

выходов

![]()

определяют правила функционирования КА.

Вывод

Если КА имеет только одно состояние, то в этом случае он вырождается в автомат без памяти (в комбинационную схему), выход которой не зависит от предыстории и в каждый момент времени определяется только входным сигналом в тот же момент времени.

Структурная схема ПЦУ

С

труктурная

схема последовательностного автомата

состоит из двух частей:

комбинационного устройства (КЦУ) и

памяти (ЗУ), состоящей из элементов

памяти (T).

труктурная

схема последовательностного автомата

состоит из двух частей:

комбинационного устройства (КЦУ) и

памяти (ЗУ), состоящей из элементов

памяти (T).

Элементы памяти ПЦУ

В качестве элементов памяти (ЭП) могут быть применены как однобитовые элементы памяти (различные типы триггеров), так и многобитовые (многоразрядные) цепочки триггеров.

ЭП часто реализуется на основе бистабильных ячеек (БЯ). Обычно применяются динамические и статические ЭП.

Статические ЭП реализуются на БЯ.

Динамические ЭП используют свойство полевого транзистора МОП–структуры сохранять заряд между затвором и истоком.

БЯ является простейшим типом триггера, реализованного с помощью элементов базиса И–НЕ или ИЛИ–НЕ с соответствующими обратными связями и позволяет хранить один бит цифровой информации (бит ― единица цифровой информации, соответствующая одной логической «1» или логическому «0»).

Закон функционирования ПЦУ

Закон функционирования АП может задаваться в виде уравнений, таблиц и графов.Под законом функционирования понимается совокупность правил, описывающих последовательность переключения состояний автомата и последовательность выходных сигналов в зависимости от последовательности поступления входных сигналов.

№45Автоматы Мура и Мили.

Автоматы Мура и Мили – две модели АП, зависящие от способа определения выходного сигнала.

Автомат Мили

Его поведение определяется системой равенств (2) и (3), где выходной сигнал определяется входным сигналом x(t) и состоянием s(t).

Автомат Мура

Его поведение определяется следующей системой равенств

![]()

![]()

В модели Мура выход однозначно определяется только текущим состоянием.

Модели Мура и Мили могут представлять как полностью определенный, так и частично определенный КА.

У полностью определенного КА области определения функций переходов j и выходов y совпадают с множеством S´X всевозможных пар вида {si, xj}.

У частичного КА области определений функций j и y строго включены в множество S´X.

№46. Асинхронный RS-триггер.

RS–триггер представляет собой элементарный цифровой автомат с двумя устойчивыми состояниями и двумя входами R и S.

Запрещенная комбинация RS-триггера

Запрещенной является комбинация входных сигналов, вызывающая неопределенное состояние триггера. Эта комбинация исключается при выполнении условия

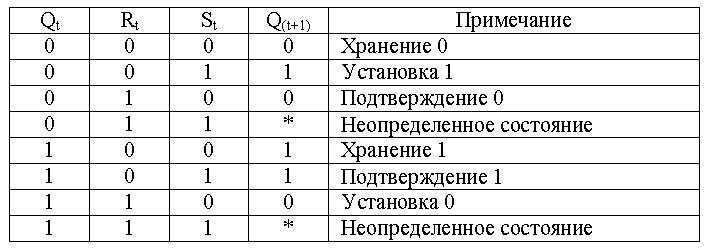

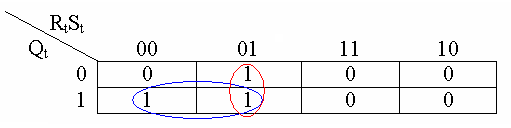

Вариант таблицы переходов RS-триггера

Характеристическое уравнение RS–триггера

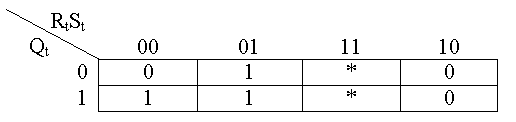

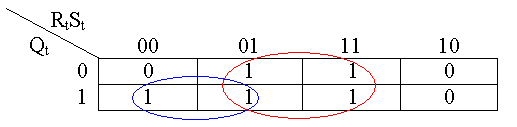

Составим карту Карно для Qt+1

Вариант 1

Доопределим звездочки (*) единичными значениями

Получим (при выполнении условия (1))

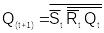

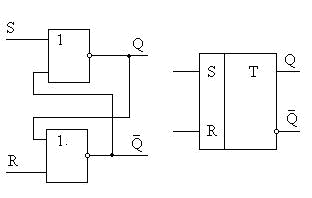

Выберем базис И–НЕ и преобразуем функцию (2), используя правило де Моргана

Выражение (3) задает схему асинхронного RS–триггера. Она построена на двух ЛЭ И-НЕ, соединенных т.о., что выход каждого ЛЭ подключен к одному из входов другого.

Такое соединение элементов в схеме обеспечивает два устойчивых состояния.

Э2 асинхронного RS –триггера с инверсными* входами и его УГО

Характеристическое уравнение RS–триггера

Вариант 2

Доопределим звездочки (*) нулевыми значениями

Получим (при выполнении условия (1))

![]()

Выберем

базис ИЛИ–НЕ и преобразуем функцию

(4), используя правило де Моргана

![]()

Выражение (5) задает схему асинхронного RS–триггера. Она построена на двух ЛЭ ИЛИ-НЕ, соединенных таким образом, что выход каждого ЛЭ подключен к одному из входов другого.

Такое соединение элементов в схеме обеспечивает два устойчивых состояния.

Э2 асинхронного RS –триггера с прямыми входами и его УГО

П

ри

переключении асинхронного RS-триггера

из

одного состояния в другое его элементы

последовательно переключаются и время

переключения tпер

равно удвоенному среднему времени

задержки распространения сигнала в

логическом элементе:

ри

переключении асинхронного RS-триггера

из

одного состояния в другое его элементы

последовательно переключаются и время

переключения tпер

равно удвоенному среднему времени

задержки распространения сигнала в

логическом элементе:

Или

Г де

время задержки сигнала на элементе

И-НЕ;

де

время задержки сигнала на элементе

И-НЕ;

― время

задержки сигнала на элементе ИЛИ-НЕ.

― время

задержки сигнала на элементе ИЛИ-НЕ.

Вывод

Чем меньше tпер, тем большее число переключений триггера можно произвести в единицу времени, т.е. тем выше быстродействие триггера.

№47. Синхронный RS-триггер.

На входы логического элемента (ЛЭ) или устройства сигналы не всегда поступают одновременно, т.к. могут иметь место гонки.

Это отрицательное явление можно устранить временным стробированием, когда на элемент кроме информационных сигналов подаются синхроимпульсы, к моменту прихода которых информационные сигналы успевают установиться на входах.

Основное условие правильной работы логических схем с использованием RS-триггеров — недопустимость одновременного действия сигнала Rt или St, переключающего триггер, и съема информации с выхода Qt+1 триггера.

Поэтому в потенциальных сериях элементов содержатся только синхронные триггеры.

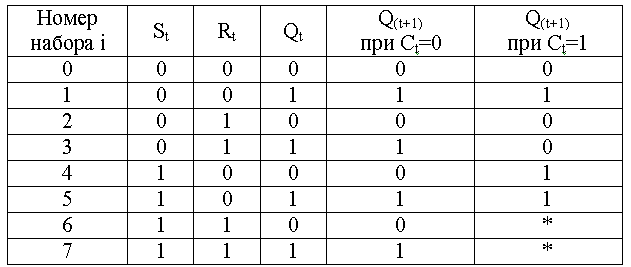

Таблица функционирования синхронного RS-триггера

Синхронные RS–триггеры кроме информационных входов R и S имеют вход синхронизации С.

Если на входе С действует логический уровень Сt = 0 (или Сt=1), то триггер сохраняет свое состояние, а если Сt =1 (или Сt=0), то он работает в режиме асинхронного RS –триггера.

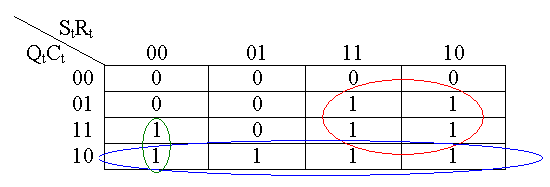

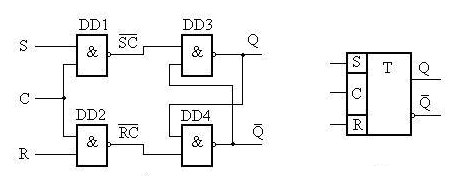

Составим карту Карно для Qt+1, доопределяя единицами значения Qt+1, соответствующие запрещенным комбинациям Rt и St.

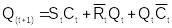

Характеристическое уравнение синхронного RS–триггера

Используя карту Карно, запишем характеристическое уравнение синхронного RS–триггера

Из (6) следует, что при Ct=0 Q(t+1)=Qt, т.е. Т. сохраняет свое состояние.

П ри

Ct=1

ри

Ct=1

т.е. получили уравнение асинхронного RS-триггера.

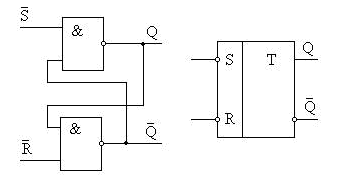

Э2 синхронного RS-триггера и его УГО

Описание работы схемы

Элементы DD1 и DD2 передают переключающую логическую 1 с информационного входа S или R на соответствующие входы асинхронного RS–триггера с инверсными входами (элементы DD3 и DD4) только при наличии на синхровходе С уровня логической единицы.

Аналогичным образом может быть синтезирована функциональная схема одноступенчатого синхронного RS –триггера, тактируемого уровнем логического 0.

№48. Двухступенчатый синхронный RS–триггер

В потенциальных сериях микросхем отсутствуют элементы для задержки сигналов.

Поэтому для надежной работы логических каскадов на каждый двоичный разряд, хранящий один бит информации, используют два триггера, которые управляются двумя сдвинутыми во времени тактирующими импульсами.

Второй тактирующий импульс можно получить инвертированием первого.

Тактирование триггера фронтом импульса или перепадом потенциала можно обеспечить, выполняя его двухступенчатым.

Э2 двухступенчатого синхронного RS-триггера*

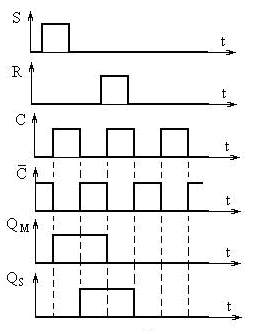

Временные диаграммы УГО

Работа триггера

Если на синхронизирующий вход подается сигнал С=1, то входная информация, определяемая сигналами на R– и S– входах, принимается в основной — ведущий триггер (М).

Состояние ведомого триггера (S) сохраняется, т.к. запись в триггер S блокируется уровнем логического 0 с выхода элемента НЕ.

Как только импульс синхронизации примет значение С=0, триггер M будет переведен в режим хранения информации, а с инвертора НЕ уровень логической единицы запишет информационное состояние триггера М в триггер S.

Двухступенчатые синхронные триггеры называют также MS-триггерами*.

Синхронный триггер обычно имеет дополнительные асинхронные входы

и , по которым он независимо от сигнала на синхровходе С переключается в состояние 0 или 1.

Триггер работает как обычный двухступенчатый синхронный триггер, если на его входах и установлены уровни логической единицы.

Различия между одноступенчатым и двухступенчатым синхронными RS-триггерами со статическим управлением

Одноступенчатый синхронный триггер можно переключить, если при С=1 изменить комбинацию на установочных входах с прежней (например, R = 0, S=1) на новую (R=1, S=0) или наоборот.

В двухступенчатом синхронном триггере при С=1 вторая ступень отключена от первой, а при С=0 первая ступень не принимает информацию с входов R и S. Лишь при изменении сигнала с 1 на 0 на синхронизирующем входе С информация из первой ступени переписывается во вторую ступень и состояния выходов триггера S изменяются.

№49. Синхронный RS-триггер с динамическим управлением.

Работа триггера

Пусть триггер хранит логическую 1 (Q=1, ØQ=0). Уровень С=0 на синхровходе Т. будет блокировать состояние Т. независимо от комбинации входных сигналов на его установочных входах (ØR, ØS), т. к. уровни логической 1 на выходах элементов DD3 и DD4 не смогут изменить состояние триггера Т.

Если перед подачей на вход С логической 1 на установочных входах действовали, например, уровни ØR=0 и ØS=1, то при смене уровня на входе С с 0 на 1 на выходе элемента DD4 образуется уровень логического 0, устанавливающий триггер Т в состояние 0 (Q=0,ØQ=1). Одновременно уровень логического 0 с выхода элемента DD4 подается на вход элемента DD2 и на его выходе возникает уровень логической 1 независимо от последующих значений уровня сигнала на входе ØR.

Уровень логического 0 с выхода элемента DD3 также передается на вход элемента DD1, обеспечивая на его выходе уровень логической 1 независимо от последующих значений уровня на входе ØS. Таким образом происходит логическое отключение триггера Т от входов ØR и ØS. Изменение на входе С логического уровня с 1 на 0 заблокирует состояние триггера Т, т. е. он будет хранить логический 0.

Если теперь на установочных входах триггера будут действовать уровни ØR =1 и ØS=0, то при смене уровня на входе С (с 0 на 1) произойдет переключение триггера Т из состояния 0 в состояние 1 (Q=1,ØQ=0), после чего никакие последующие изменения уровней на входах R и S триггером Т не будут восприниматься, пока на входе С не произойдет новый переход уровней с логического 0 на 1.

№ 50. JK– триггер. Таблица состояний, таблица переходов. Схема триггера. Синхронный JK– триггер. Триггер, выполненный по схеме "мастер – помощник", схема триггера. Особенности работы.

JK– триггер

Триггеры этого типа отличаются от RS–триггеров тем, что при значениях входных сигналов, запрещенных для RS–триггеров, они инвертируют хранимую в них информацию.

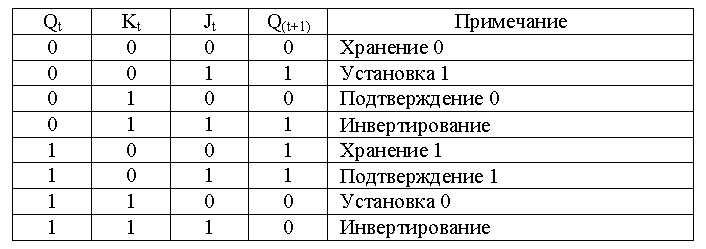

Таблица состояний JK триггера

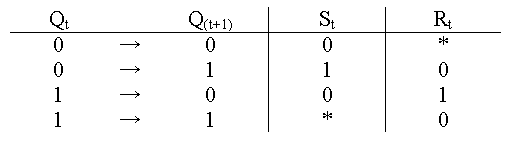

Таблица переходов JK-триггера

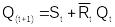

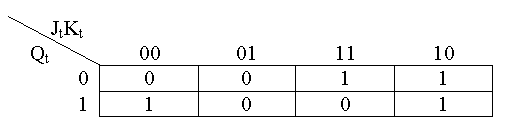

Характеристическое уравнение JK-триггера

![]()

Приведем (1) к базису И–НЕ

![]()

Из таблицы состояний видно, что состояние JK–триггера определяется не только уровнями на информационных входах J и K, но и состоянием Qt, в котором ранее находился JK–триггер. Это дает возможность строить функциональные схемы JK–триггеров на основе двухступенчатых RS–триггеров.

JK–триггеры могут быть асинхронными и синхронными.

Асинхронный JK–триггер состоит из комбинационной схемы и триггера-защелки.

Интегральные JK–триггеры обычно выполняются синхронными.

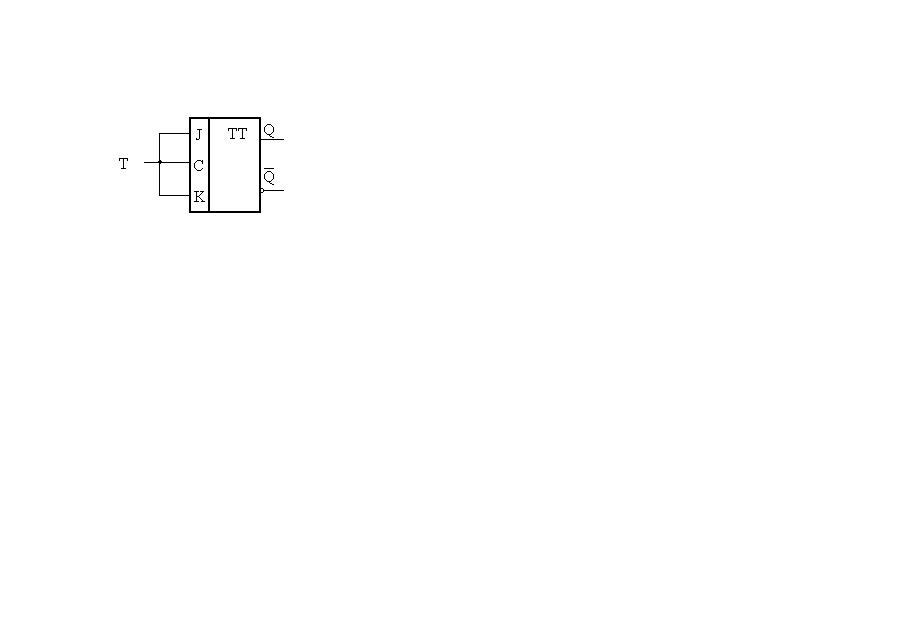

Аббревиатура JK–триггера «ТВ».

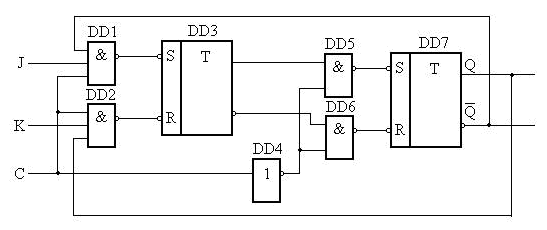

Э2 двухступенчатого JK-триггера

Работа JK–триггера

Если J=K=0, то на выходах элементов DD1, DD2 устанавливается уровень логической 1. Триггер DD3 и, следовательно, JK–триггер сохраняют прежнее состояние.

Пусть JK–триггер находится в состоянии 0 (Q=0;ØQ=1).

Тогда при подаче сигналов J=1, C=1 на выходе элемента DD1 возникает уровень логического 0, который запишет 1 в триггер DD3, а после окончания действия синхронизирующего сигнала (С=0) состояние триггера DD3 уровнем логического 0 с выхода элемента DD5 передается в триггер DD7, т.е. JK–триггер переключается в состояние 1 (Q=1;ØQ=0).

Если теперь на JK–триггер подать сигналы , то с выхода элемента DD2 логический уровень 0 установит триггер DD3 в логический 0. После окончания действия синхронизирующего сигнала (С=0) состояние триггера DD3 будет уровнем логического 0 с выхода элемента DD6 передано в триггер DD7, т.е. JK–триггер переключается в состояние 0 (Q=0;ØQ=1).

При J=K=1 и С=1 JK–триггер изменяет свое состояние на противоположное. Следовательно, при подаче на вход С серии синхронизирующих сигналов (при J=K=1) JK–триггер работает в счетном режиме (Т–триггер).

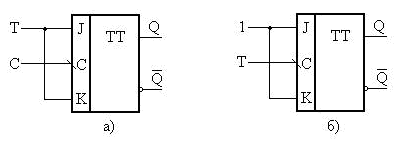

Варианты применения JK-триггера*

На базе синхронного JK–триггера можно реализовать синхронный и асинхронный Т–триггер, D–триггер и синхронный RS–триггер

Выводы

Выводы

Т.к. JK-триггер выполнен по структуре мастер–помощник, то его УГО содержит обозначение ТТ.

Срабатывание JK–триггера происходит по срезу синхроимпульса.

Применение двухступенчатых схем позволяет повышать функциональную надежность триггеров, т.к. в течение длительности синхроимпульса в системе завершаются все переходные процессы.

УГО JK–триггера (а); пояснение обозначения входа синхронизации триггера (б)

№51. Синхронный D –триггер. Таблица состояний, таблица переходов. Схема триггера.

D–триггер (от delay–задержка) называют информационным триггером, а также триггером задержки, т.к. сигнал на его выходе появляется с задержкой на один такт*.

D – триггер бывает только синхронным. Он может управляться (переключаться) как уровнем тактирующего импульса, так и его фронтом.

Для триггера типа D, состояние в интервале времени между сигналом на входе и следующим состоянием триггера формируется проще, чем для любого другого типа.

Однако, устройства, реализованные на D–триггерах, схематически сложнее, чем на других типах триггеров.

Таблица переходов D- триггера

Характеристическое уравнение D-триггера

![]()

т.е. при Ct =0 Qt+1 = Qt,

а при Ct =1 Qt+1 = Dt.

Функциональная схема и УГО D–триггера

Временные диаграммы D-триггера

Выводы

По синхроимпульсу D–триггер принимает состояние, соответствующее информационному сигналу согласно таблице переходов (слайд 20).

D–триггеры могут переключаться как уровнем синхроимпульса, так и его фронтом.

В технической литературе D–триггер, управляемый уровнем синхроимпульса, известен также как триггер–защелка*.

№52. T– триггер.

Т–триггер ― это счетный триггер.

Т–триггер имеет один вход без учета вспомогательных входов принудительной установки «0» и «1».

На вход Т–триггера подают тактирующие (счетные) импульсы. После подачи каждого тактирующего импульса состояние Т–триггера изменяется на обратное (инверсное) предыдущему состоянию.

Аналогично изменяется состояние JK-триггера при комбинации входных переменных J=1 и K=1.

Т–триггеры строятся только на базе двухступенчатых RS– , D– или JK– триггеров.

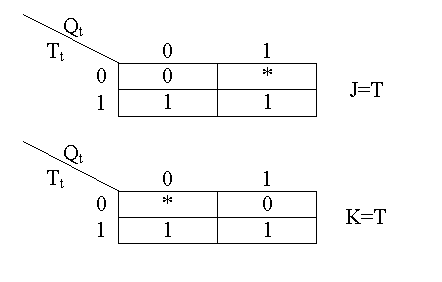

Синтез Т-триггера на базе JK-триггера

Рассмотрим пример синтеза Т–триггера из JK–триггера.*

Представим Т–триггер как совокупность комбинационного устройства (КУ) и JK–триггера

При подаче на входы КУ сигналов Q и Т, КУ должно обеспечить на выходах J и K сигналы управления JK–триггером, соответствующие совмещенной таблице переходов (слайд 28).

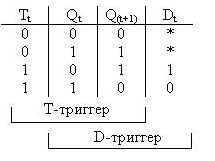

Совмещенная таблица переходов T- и JK-триггеров

Синтез Т-триггера на базе JK-триггера

Из полученных логических выражений (4) и (5) следует, что для построения Т–триггера, достаточно объединить входы C, J и K JK–триггера

Т– триггер на базе D–триггера

Рассмотрим пример синтеза Т–триггера на базе D–триггера, управляемого фронтом синхроимпульса.

Совмещенная таблица переходов T- и D-триггеров

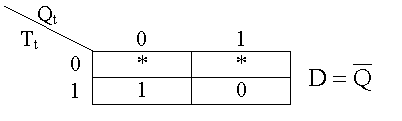

Карта Карно Т–триггера, синтезируемого из D–триггера

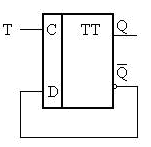

Схема Т-триггера на базе D-триггера

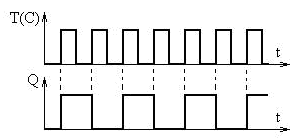

Временные диаграммы, поясняющие принцип работы счетного триггера

Выводы

Из временных диаграмм следует, что переключение состояния счетного триггера на базе D-триггера происходит в моменты прихода передних фронтов синхроимпульсов.

Частота следования импульсов на выходе Т- триггера в два раза меньше частоты входных синхроимпульсов, что позволяет использовать их в качестве делителей частоты. Если один счетный триггер позволяет делить частоту на два, то для реализации делителя частоты на четыре потребуется два триггера, соединенных последовательно и т.д.

№53.Двоичные счетчики. 54. Параметры счетчиков. Классификация счетчиков.

Счетчик — узел ЭВМ, который осуществляет счет и хранение кода числа подсчитанных сигналов.

Под сигналами понимаются как перепады потенциала, так и импульсы.

Аббревиатура счетчика «ИЕ» (например, К555 ИЕ5).

Счетчики представляют собой цифровые автоматы Мура, в которых новое состояние счетчика определяется его предыдущим состоянием и значением логической переменной на входе. Внутренние состояния счетчиков характеризуются коэффициентом пересчета (модулем счета) Ксч, определяющим число его устойчивых состояний.

2. Основные параметры счетчика

Разрешающая способность — минимальное время между двумя сигналами, которые надежно фиксируются счетчиком.

Максимальное быстродействие* — величина, обратная разрешающей способности и равная числу сигналов, фиксируемых счетчиком в единицу времени.

Информационная емкость — максимальное число сигналов, которое может быть подсчитано счетчиком. Количественно емкость счетчика равна коэффициенту пересчета Ксч.

Классификация счетчиков

Счетчики различаются:

назначением,

типом и количеством используемых триггеров,

режимами работы,

порядком изменения состояния,

организацией связей между триггерами счетчика.

Счетчики могут быть одноразрядные, многоразрядные, двоичные, десятичные, а также с любым иным целым по значению коэффициентом пересчета Ксч.

По порядку изменения состояния могут быть счетчики с естественным и произвольным (принудительным) порядком изменения состояния.

В счетчиках с естественным порядком изменения состояния значение кода каждого последующего состояния счетчика отличается на единицу от кода предыдущего состояния.

В счетчиках с произвольным порядком изменения состояния значения кодов соседних состояний могут отличаться более чем на единицу.

Счетчики с естественным порядком изменения состояний подразделяются на простые (суммирующие и вычитающие) и реверсивные, которые в зависимости от управляющих сигналов могут работать как в режиме сложения, так и в режиме вычитания.

Организация режима суммирования или вычитания в реверсивном счетчике осуществляется за счет внешнего управляющего сигнала.

По способу организации счета счетчики делят на асинхронные и синхронные.

В асинхронных или последовательных счетчиках переключение триггеров происходит последовательно во времени, а в синхронных счетчиках — параллельно (одновременно).

По способу организации счета счетчики делят на асинхронные и синхронные.

В асинхронных или последовательных счетчиках переключение триггеров происходит последовательно во времени, а в синхронных счетчиках — параллельно (одновременно).

Возможны два основных режима работы счетчика.

Регистрация числа поступивших на счетчик сигналов: результатом является содержимое счетчика.

Деление частоты. Выходными сигналами являются импульсы переполнения счетчика.

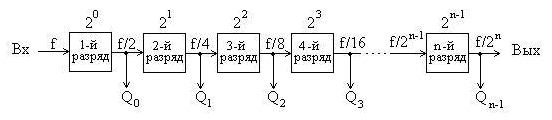

Э1 асинхронного счетчика

Классификация счетчиков

Одноразрядные двоичные счетчики строятся на основе Т–триггеров, осуществляющих сложение по mod2, т. е. счет и хранение не более двух сигналов в соответствии с характеристическим уравнением Т–триггера

![]()

В общем случае n–разрядный двоичный счетчик также считает по mod2.

Обычно выходные сигналы счетчика совпадают с его состоянием. Поэтому состояние счетчика читается как слово

где Q0 — младший разряд счетчика. Из Э1 (слайд 10) видно, что входной сигнал поступает на вход триггера младшего разряда счетчика.

Суммирующие двоичные счетчики

В суммирующих двоичных счетчиках счетный вход каждого последующего триггера соединен с выходом предыдущего т.о., что при переходе триггера младшего разряда из состояния 1 в состояние 0 в цепи переноса между триггерами появляется сигнал переноса, под воздействием которого триггер старшего разряда изменяет свое состояние на противоположное.

В зависимости от способа организации цепей переноса различают двоичные счетчики с последовательным, сквозным, параллельным и групповым переносами.

Двоичные счетчики с последовательным переносом строятся на основе асинхронных Т–триггеров.

№55. Асинхронный счетчик с коэффициентом счета 8.

Рассмотрим трехразрядный суммирующий двоичный счетчик с естественным порядком изменения состояний:

Изменение младшего разряда Q0 связано с изменением единичного значения сигнала счета Т0 на нулевое, а изменение состояния каждого последующего разряда Qi связано с изменением единичного состояния на нулевое предыдущего Qi-1 разряда.

Т.о., в счетчике сигналы переноса распространяются последовательно от младшего разряда к старшему.

Т.к. каждый триггер счетчика осуществляет сложение по mod2, то закон функционирования трехразрядного суммирующего двоичного счетчика может быть представлен уравнениями

![]()

![]()

![]()

Э2 асинхронного счетчика с Ксч=8

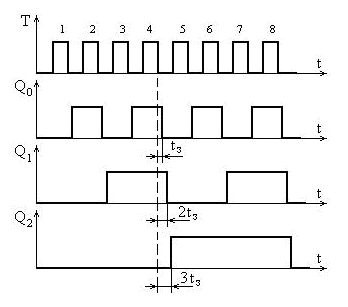

Временные диаграммы работы счетчика

Работа счетчика

Перед началом счета сигналом Уст. 0 счетчик устанавливается в состояние «000». Из временной диаграммы видно, что после прихода 7–го входного сигнала на вход Т показание счетчика будет «111». При поступлении 8–го входного сигнала счетчик переходит в исходное состояние «000». При этом на выходе счетчика Q2 в результате перехода триггера DD2 в состояние 0 возникает сигнал переноса, который называют сигналом переполнения счетчика.

Выводы

Быстродействие двоичного счетчика с последовательным переносом зависит от быстродействия триггера младшего разряда, т.к. каждый последующий триггер уменьшает частоту следования сигналов, поступающих на его вход, и определяется временем Тсч распространения сигналов переноса.

Максимальное время Тсч.макс установления кода в счетчике с последовательным переносом равно

![]()

где n — число разрядов счетчика; tз — время задержки сигнала в одном разряде счетчика, т. е. триггере.

Из (3) следует, что с ростом разрядности увеличивается переходный процесс в счетчике, а следовательно, понижается предельная частота его работы.

Достоинством счетчиков с последовательным переносом является минимальное количество элементов и межэлементных связей.

Асинхронный суммирующий двоичный счетчик м.б. реализован на D– и RS–триггерах, работающих в режиме счетного Т–триггера.

№56. Двоично–десятичный асинхронный счетчик

Из временных диаграмм следует, что после каждого 10–го импульса все триггеры устанавливаются в нулевое состояние. Достигается это за счет того, что в схему вводится комбинационный элемент DD4.

Асинхронные счетчики выпускаются в виде отдельных микросхем (например, К555 ИЕ5).

Существуют микросхемы JK–триггеров (например, К555 ТВ1), которые не требуют применения элементов внешней логики при проектировании двоично-десятичных счетчиков на их основе.

Выводы

Недостатком асинхронных счетчиков является то, что они работают сравнительно медленно.

Кроме того, при увеличении числа разрядов асинхронного счетчика повышается вероятность сбоя в его работе.

Устраняются указанные недостатки в схемах синхронных счетчиков.

№57Синхронные двоичные счетчики.

Синхронный счетчик характеризуется одновременным срабатыванием всех триггеров, входящих в его состав.

Схемотехнически синхронный счетчик сложнее, чем асинхронный. Его основное преимущество по сравнению с асинхронными счетчиками ― повышенное быстродействие.

№58Порядок синтеза синхронных счетчиков на примере двоично-десятичного счетчика (Ксч= 10 и m=4).