- •1.Последовательный односторонний ограничитель

- •Переходные процессы.

- •2.Паралельные диодные ограничения

- •Выходной сигнал диодного ао имеет искаженную форму из–за с0.

- •Стремятся, чтобы Сд и Rпр были как можно меньше (выбирают специальные быстродействующие импульсные диоды у которых Сд и Rпр малы).

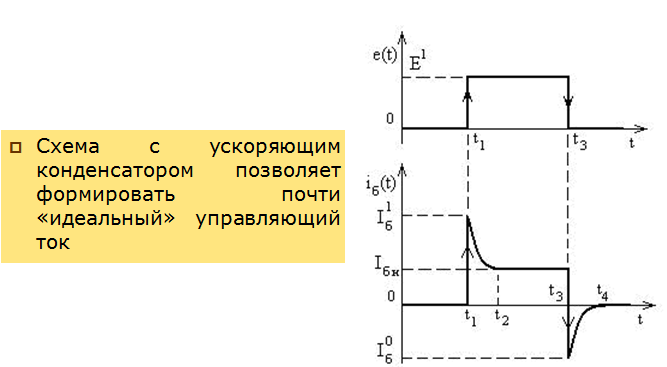

- •Для уменьшения времени фронта необходимо увеличивать амплитуду включающего тока.

- •Для уменьшения времени рассасывания необходимо уменьшать амплитуду включающего тока до величины тока базы насыщения и увеличивать амплитуду выключающего тока.

- •Для уменьшения времени спада необходимо увеличивать амплитуду выключающего тока.

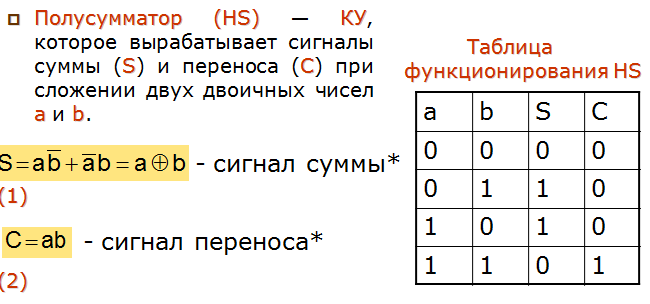

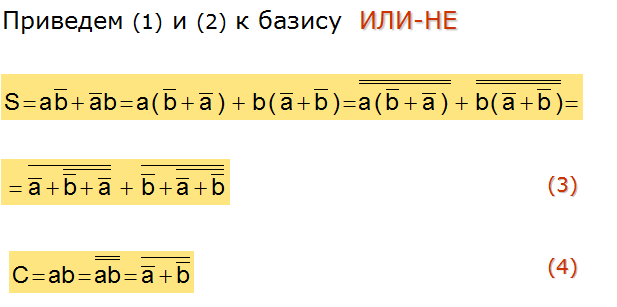

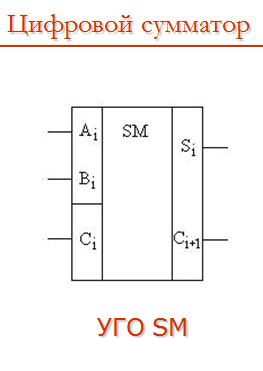

- •Для сложения двух многоразрядных двоичных чисел на каждый разряд необходим один sm и только в младшем разряде можно обойтись hs.

- •Аппаратная сложность и быстродействие сумматора являются очень важными параметрами. Поэтому разработано множество вариантов сумматоров, которые имеют разветвленную классификацию.

- •Перечислим основные типы сумматоров:

- •Составим таблицу состояний проектируемого счетчика на основе синхронных jk–триггеров*. При заполнении таблицы учитывают таблицу переходов jk–триггера (слайд 5).

Для уменьшения времени фронта необходимо увеличивать амплитуду включающего тока.

Для уменьшения времени рассасывания необходимо уменьшать амплитуду включающего тока до величины тока базы насыщения и увеличивать амплитуду выключающего тока.

Для уменьшения времени спада необходимо увеличивать амплитуду выключающего тока.

Из временных диаграмм следует, что в момент t3, когда на вход схемы поступает выключающий перепад напряжения, VT1 находится в ненасыщенном состоянии, поэтому время рассасывания неосновных носителей из базы равно нулю (tр = 0).

На интервале [t3, t4] конденсатор разряжается и к моменту t4 ключ переходит в первоначальное состояние.

Остроконечная форма управляющего тока объясняется тем, что конденсатор С и входное сопротивление VT1 составляют дифференцирующую цепочку.

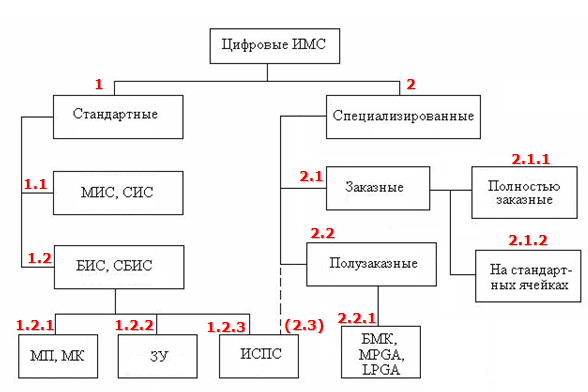

№16Классификация цифровых микросхем.

1 Стандартные ИМС

Приобретаются потребителем как готовые изделия и производятся массовыми тиражами.

Требуют значительных средств на проектирование.

Имеют жесткую внутреннюю структуру.

Потребитель не может влиять на характер их функционирования.

2 Специализированные ИМС*

Имеют индивидуальный характер функционирования.

Разрабатываются по конкретному заказу.

1 Стандартные ИМС

1.1 Микросхемы малого (МИС) и среднего (СИС) уровней интеграции*

Этот класс ИМС представлен очень широко. В настоящее время такие ИМС применяются редко, т.к. построение на них сложных устройств ведет к ухудшению технико-экономических параметров аппаратуры в сравнении с теми, которые могли бы быть получены при применении ИМС высокого уровня интеграции.

1.2.1 БИС/СБИС* микропроцессоров и микроконтроллеров (МП и МК)**

Многочисленные микросхемы МП и МК широко и успешно применяются при решении задач программной реализации алгоритмов.

1.2.2 БИС/СБИС запоминающих устройств***

Относятся к наиболее массовым ИМС с широкой номенклатурой; применяются в устройствах и системах различного назначения для хранения данных и обмена ими с другими блоками систем.

ИМС с программируемой пользователем структурой (ИСПС).

Их появление связано с новым направлением развития элементной базы. Эти БИС/СБИС дают возможность использования микросхем высокого уровня интеграции в проектах практически любой тиражности.

В ИСПС внутреннюю структуру схемы задает сам потребитель. Изготовитель в этом процессе не участвует и поставляет на рынок продукцию, пригодную для многих покупателей, создающих аппаратуру разного назначения.

ИСПС имеют двойственный характер: для потребителя они являются специализированными, а для промышленности — стандартными.

Специализированные ИМС (СпИС)

Проектируются для конкретного заказчика.

От заказчика требуются затраты значительных средств при длительных сроках разработки СпИС.

Для преодоления трудностей создания СпИС были предложены методики проектирования, которым соответствует ряд разновидностей СпИС*.

Различают классы заказных и полузаказных СпИС

Заказные СпИС

Разновидностями заказных* микросхем являются полностью заказные ИМС** и ИMС, спроектированные методом «на стандартных ячейках»***.

2.1.1 Полностью заказные СпИС

Проектируются по требованиям конкретного заказчика. Проектировщик имеет полную свободу действий, определяя схему по своему усмотрению вплоть до уровня схемных компонентов (отдельных транзисторов и т. п.).

Для изготовления схемы требуется разработка всего комплекта фотошаблонов, верификация и отладка всех схемных фрагментов. Такие схемы очень дороги и имеют длительные циклы проектирования.

Полностью заказные схемы позволяют добиваться наивысших технических параметров

Выводы

Заказные БИС/СБИС от начала до конца разрабатываются для конкретного проекта. В них нет лишних элементов, оптимально размещены подсхемы и их межсоединения. Свойственная заказным схемам оптимизация БИС/СБИС по конкретному техническому заданию минимизирует площадь кристалла, т.е. удешевляет его, позволяет добиться максимального быстродействия разрабатываемого устройства и т. д.

Разработка оригинальной БИС/СБИС чрезвычайно дорога и требует спроектировать и изготовить полный комплект фотошаблонов (15—20 штук).

Схемы на стандартных ячейках

Их фрагменты берутся из заранее разработанной библиотеки схемных решений.

Т.к. используемые фрагменты хорошо отработаны, то стоимость и длительность проектирования снижаются.

Разработка шаблонов облегчена.

Проектировщик имеет меньше свободы в построении схемы, т. е. результаты ее оптимизации по критериям площади кристалла, быстродействию и т. д. менее эффективны.

Время разработки схем приблизительно в два раза меньше по сравнению с временем проектирования полностью заказных схем.

2.2 Полузаказные СпИС

К полузаказным* схемам относятся базовые матричные кристаллы БМК**.

2.2.1 БМК

Используется стандартный полуфабрикат, который доводится до готового изделия с помощью индивидуальных межсоединений.

Реализация требует изготовления лишь малого числа фотошаблонов (для MPGA) или цикла операций разрушения некоторых межсоединений лазерным лучом (для LPGA).

Стоимость и длительность проектирования в сравнении с полностью заказными схемами сокращаются в 3—4 раза, однако, результат еще дальше от оптимального, чем в методе стандартных ячеек*** .

2.3 ИМС с программируемой пользователем структурой (ИСПС)*

Первоначально программирование структур было применено в программируемых логических матрицах (ПЛМ), программируемой матричной логике (ПМЛ) и базовых матричных кристаллах (БМК).

Позднее появились более сложные ИСПС

CPLD (Complex Programmable Logic Devices);

FPGA (Field Programmable Gate Arrays);

ИСПС комбинированной архитектуры, сочетающие признаки CPLD и FPGA.

Позднее были разработаны ИСПС с аналоговыми и аналого-цифровыми элементами (программируемые аналоговые интегральные схемы ¾ ПАИС).

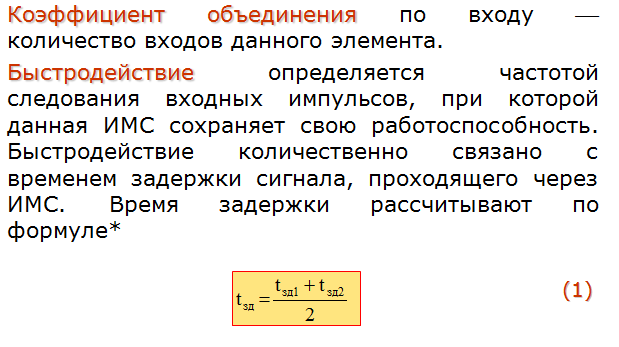

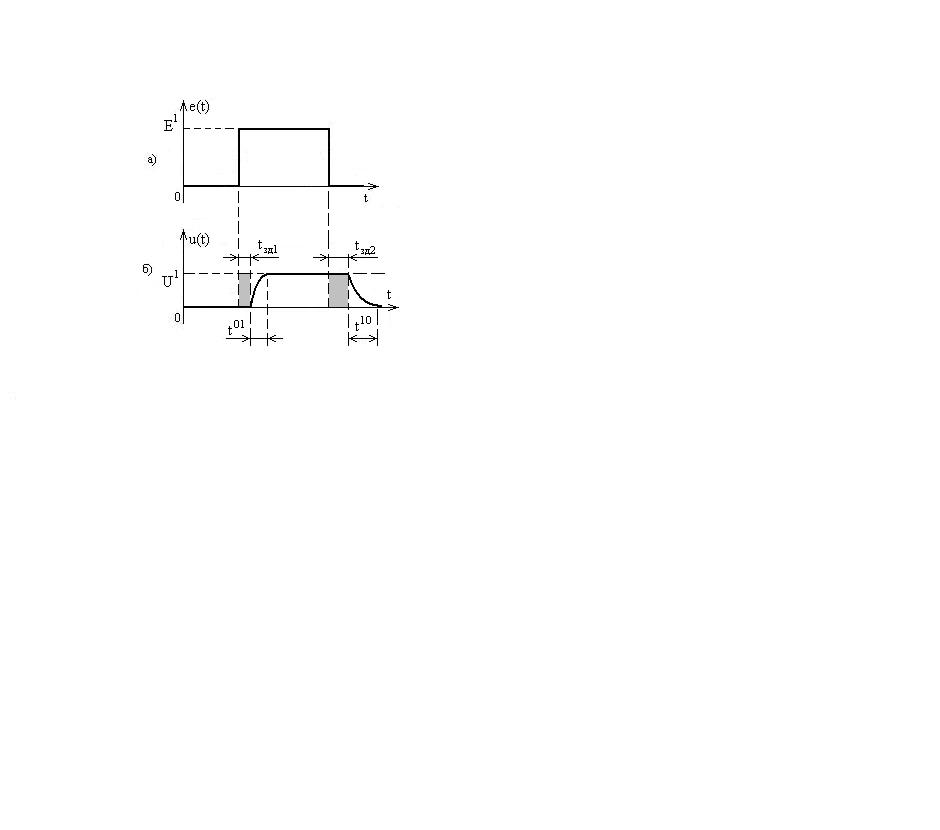

№17Параметры цифровых микросхем.

Уровень логической единицы и нуля: Е1 и Е0.

Порог чувствительности ¾ минимальное значение входного сигнала при котором ИМС работает в соответствии с заданным алгоритмом.

Помехоустойчивость ¾ определяется максимальной величиной помехи, при которой ИМС сохраняет работоспособность.

Коэффициент разветвления ¾ количество однотипных ИМС, которые могут быть подключены к выходу данной ИМС без нарушения работоспособности. Коэффициент разветвления определяет нагрузочную способность элементов ИМС.

По быстродействию различают*

ИМС со сверхвысоким быстродействием, у которых tзд< 5 нс.

К ним относятся ИМС серий К500 и К1500;

быстродействующие ИМС, у которых

5£tзд< 20нс.

К ним относятся ИМС серий К555, К530.

среднего быстродействия, у которых

20£tзд< 50нс.

К ним относятся ИМС серий К155, К131.

низкого быстродействия, у которых tзд > 50нс. К ним относятся ИМС серий К561, К176.

Потребляемая мощность

По этому критерию ИМС делятся на три группы

малой мощности Р£3мВт (К561, К176);

средней мощности 3<P£30 мВт;

большой мощности P>30 мВт (К500 и К1500).

Обычно быстродействие ИМС тем больше, чем больше потребляемая мощность.

Количество энергии, необходимой для обработки одного бита информации

Напряжение источника питания

Uп = 3,3 В; 5 В; 9 В; 12 В; 27 В; -5,2 В.

Вид реализуемой логической функции. Применяется широкий набор интегральных логических элементов (ЛЭ): И, ИЛИ, НЕ, И–НЕ, ИЛИ–НЕ, И-ИЛИ-НЕ.

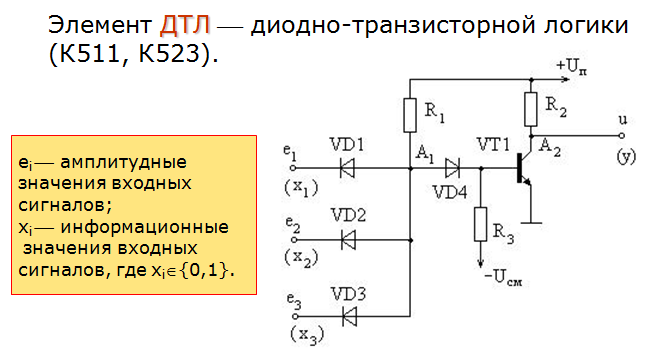

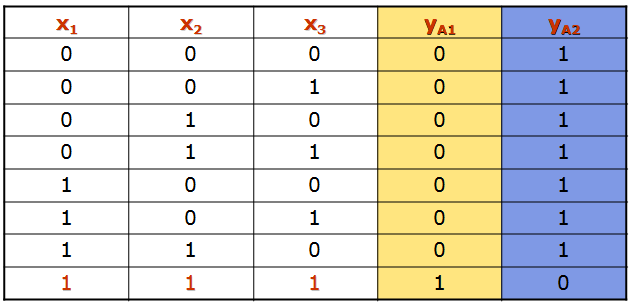

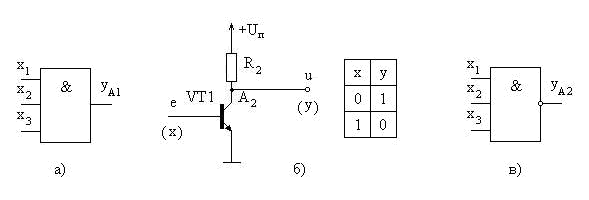

№18Элементная база цифровых микросхем: элемент ДТЛ.

Из схемы на слайде 2 видно, что если на любой из диодов VD1–VD3 подан логический нуль, то соответствующий входной диод находится в открытом состоянии, а потенциал нижнего вывода резистора R1 приблизительно равен нулю. Диод VD4 закрыт.

Транзистор VT1 также закрыт отрицательным напряжением, подаваемым через резистор R3 от источника Uсм. Поэтому на коллекторе транзистора (на выходе схемы) устанавливается напряжение логической единицы, которое равно Uп.

Если на все входы подать напряжение, соответствующее уровню логической единицы, то входные диоды закроются, а потенциал на нижнем выводе резистора R1 станет больше нуля. Поэтому диод VD4 сместится в прямом направлении и образуется делитель напряжения из резисторов R1 и R3 между источниками Uп и Uсм. Через резистор R1 протекает ток в базу транзистора VT1, в результате чего VT1 переводится в режим насыщения. Протекающий через VT1 ток коллектора вызывает падение напряжения на резисторе R2 и, следовательно, на выходе схемы устанавливается напряжение логического нуля.

Замечания

Если на любой из входов схемы подано напряжение логического нуля, то через этот вход и резистор R1 протекает ток в выходную цепь предыдущего каскада (т.е. через коллектор транзистора, находящегося в состоянии насыщения).

Если предшествующий каскад имеет коэффициент разветвления по выходу kр, то это означает, что в выходной транзистор поступают токи kр источников.

Схема является работоспособной до тех пор, пока напряжение на коллекторе остается ниже некоторого уровня, определяемого верхним пределом логического нуля.

Для того чтобы рассеиваемая мощность была не очень большой, резисторы в ИМС должны иметь очень большое сопротивление.

С другой стороны, для обеспечения высокого быстродействия схемы требуется, чтобы сопротивление резисторов было невелико.

Поэтому ДТЛ характеризуются разумным компромиссом между рассеиваемой мощностью и скоростью переключения.

К недостаткам схемы следует отнести дополнительный внешний источник отрицательного напряжения.

Указанного недостатка лишены ИМС транзисторно-транзисторной логики (ТТЛ), в которых диоды заменены транзисторами. Замена диодов транзисторами привела к изменению принципов проектирования, т.к. в интегральных технологиях изготовление транзисторов обходится не дороже диодов. Поэтому, если это необходимо, диоды могут быть заменены транзисторами в диодном включении.

Достоинством элемента ДТЛ является то, что база VT1 непосредственно не связана с источниками сигнала. Поэтому схема обладает высокой помехоустойчивостью.

В элементе ДТЛ входным запускающим является ток низкого уровня, т.е. активным является входное напряжение низкого логического уровня. Применение низкого активного уровня необходимо для обслуживания источников командных сигналов (кнопок, переключателей и контактов реле), т.к. замыканию подвижных контактов на провод с нулевым потенциалом сопутствует гораздо меньше ложных импульсов запуска (дребезг контактов), чем при их замыкании на высокий потенциал.

Транзистор VT1 предназначен не только для инверсии сигнала, но и для усиления его мощности, благодаря чему увеличивается коэффициент разветвления схем

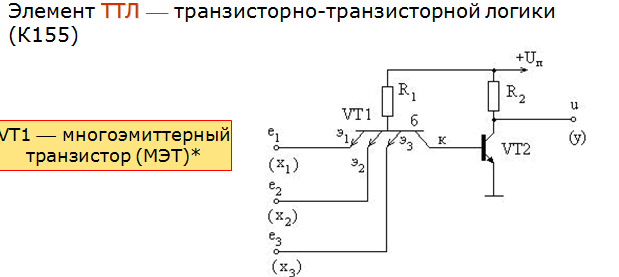

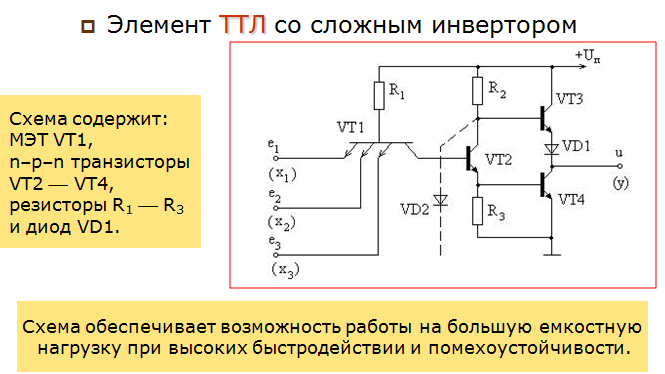

№19Элементная

база цифровых микросхем: элементы ТТЛ

и ТТЛШ.

Выводы

Схемы ТТЛ с простым инвертором (слайд 13) не нашли широкого применения из-за малых помехоустойчивости и нагрузочной способности, а также плохого быстродействия однополярного ключа при работе на емкостную нагрузку.

Они используются как схемы с открытым коллектором для реализации функции "монтажное ИЛИ", а также для включения элементов индикации.

С развитием и совершенствованием полупроводниковых технологий базовым для схем ТТЛ стал ключ со сложным инвертором ¾ двухполярным ключом.

Схема состоит из следующих каскадов

входного МЭМ VT14;

фазорасщепляющего каскада, построенного на проходном транзисторе VT2 (этот каскад работает в режиме с малым рабочим током и имеет малые емкости p–n ¾ переходов);

двухтактного выходного каскада (VT3, VT4).

Высокое

быстродействие микросхем ТТЛ при большой

емкостной нагрузке объясняется тем,

что как заряд, так и разряд нагрузочной

емкости происходят через низкоомную

выходную цепь.

Высокое

быстродействие микросхем ТТЛ при большой

емкостной нагрузке объясняется тем,

что как заряд, так и разряд нагрузочной

емкости происходят через низкоомную

выходную цепь.

Транзистор VT2 включен по схеме с общим эмиттером и содержит резисторы как в цепи коллектора, так и в цепи эмиттера. Следовательно, сигналы, снимаемые с коллектора и эмиттера, находятся в противофазе. Явление получения сигналов, смещенных на 180°, называется фазовым расщеплением сигналов, а соответствующий каскад ¾ фазорасщепляющим.

Транзисторы VT3 и VT4 образуют двухтактный усилитель мощности, что способствует увеличению мощности выходного сигнала. Поэтому нагрузочная способность и коэффициент разветвления элемента ТТЛ со сложным инвертором больше, чем у элемента ТТЛ с простым инвертором.

Диод VD1 позволяет осуществлять температурную компенсацию, что улучшает температурную стабильность элемента ТТЛ со сложным инвертором.

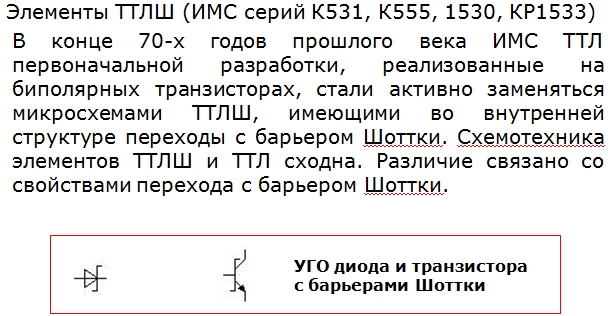

В переходах Шоттки (в металле, куда приходят электроны из полупроводника) отсутствуют процессы накопления и рассасывания неосновных носителей, характерные для электронно-дырочных переходов. ИМС, содержащие переходы с барьерами Шоттки, обладают более высоким быстродействием по сравнению с традиционными, т.к. накопление и рассасывание заряда ¾ инерционные процессы.В частности, ИМС стандартных серий 133, К155 позволяют получить быстродействие 10 нс при мощности рассеивания 22 мВт на ЛЭ*, а микросхемы серии 1533, КР1533 ¾ быстродействие 4 нс при мощности рассеивания 1 мВт на ЛЭ.

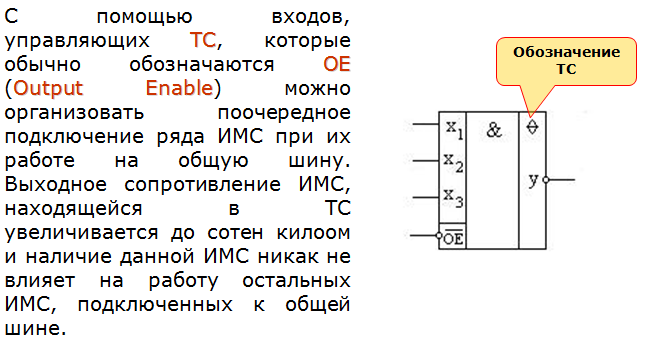

№20Понятие третьего состояния выхода.

Элементы с тремя состояниями выхода

Применение диода VD2 в схеме на слайде 16 позволяет реализовать так называемое "третье состояние" (ТС) выхода ИМС (первое состояние ¾ логический нуль, второе ¾логическая единица). ТС характеризуется тем, что ИМС отключается* от нагрузки.

№21Схемы с открытым коллектором.

Выход с открытым коллектором. Функция "Монтажное ИЛИ"

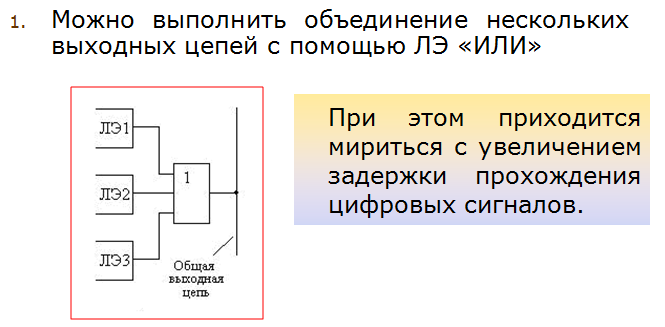

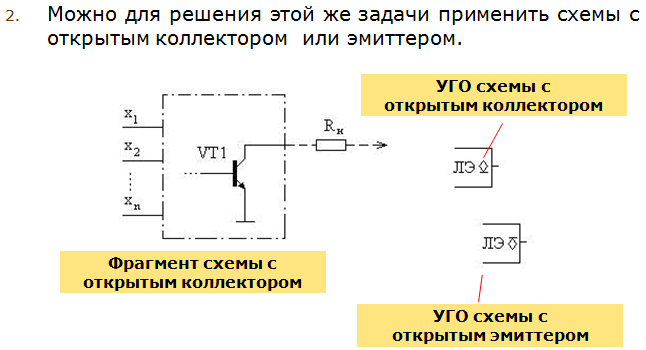

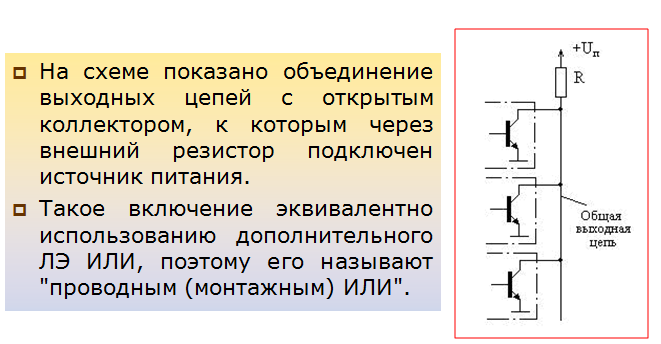

При построении цифровых устройств на базе интегральных логических элементов (ЛЭ) часто возникает необходимость объединения выходов нескольких ЛЭ с целью перехода на общую выходную цепь. Эта задача может решаться разными способами.

Наряду со схемами «монтажное ИЛИ» ИМС с открытым коллектором применяют для подключения к их выходам энергоемких нагрузок, в частности, газоразрядных и полупроводниковых индикаторов.

№22Элементная база цифровых микросхем: элемент ЭСЛ. Основные особенности и применение.

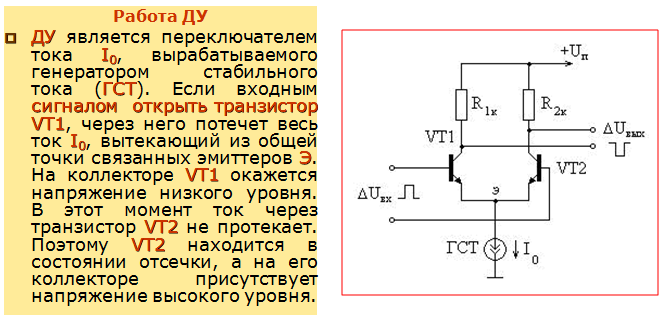

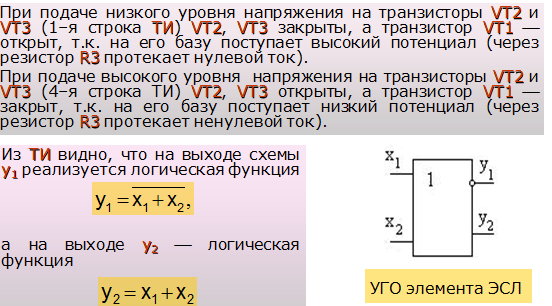

Элементы эмиттерно–связанной логики (ЭСЛ), в частности, ИМС серий К500, К1500 имеют наибольшее быстродействие из всех элементов цифровой схемотехники. Особенность ЭСЛ в том, что схема логического элемента строится на основе интегрального дифференциального усилителя (ДУ), транзисторы которого могут переключать ток и при этом никогда не попадают в режим насыщения.

Назначение ГСТ

Позволяет строго фиксировать выходные логические уровни.

Особенности применения ДУ в цифровых ИМС

В отличие от аналоговых применений ДУ, когда стремятся использовать разность напряжений между коллекторами, цифровая ИМС, переключающая ток I0, снабжается двумя инверсными выходами логических уровней Q и Q’, на которых выделяются напряжения высокого и низкого уровней

Назначение источника опорного напряжения

На базу транзистора VT4 (слайд 5) подается напряжение от источника опорного напряжения Uоп, который превращает ДУ в ЛЭ с двумя состояниями.

Напряжение Uоп фиксирует порог срабатывания переключателя тока.

Переключение осуществляется при условии

Особенности выходных цепей ЛЭ ЭСЛ

Для уменьшения сопротивлений выходов у1 и у2 в схеме применены эмиттерные повторители на транзисторах VT1 и VT5, работающие в линейном режиме.

Эмиттерные выходы у1 и у2 сделаны открытыми, чтобы их можно было соединить по схеме «монтажное ИЛИ»*.

Сопротивления внешних нагрузочных резисторов Rн1 и Rн2 можно выбирать в диапазоне от 300 Ом до 30 кОм.

Назначение R1 и R2

Резисторы R1 и R2 представляют собой внутренние резисторы утечки.

Позволяют оставлять неиспользуемые логические входы неприсоединенными.

Служат предыдущим элементам ЭСЛ нагрузками для их выходных эмиттерных повторителей.

Питание ЛЭ ЭСЛ

Особенность ИМС ЭСЛ ¾ отрицательное напряжение источника питания*.

Отрицательное напряжение питания позволяет повысить помехоустойчивость ИМС ЭСЛ, т.к. ДУ менее чувствителен к помехам, возникающим в шине эмиттерного питания**.

Ток потребления вытекает из микросхемы в источник.

Стандартное напряжение источника питания составляет -5,2 В.

Выводы

Наибольшее быстродействие схем ЭСЛ обеспечивается благодаря применению ДУ, который исключает переход транзисторов в режим насыщения, а также эмиттерных повторителей на выходе ЛЭ.

Недостатки схем ЭСЛ

Высокая потребляемая мощность.

«Отрицательная логика»* из-за которой логические уровни ЭСЛ непосредственно не совместимы со схемами ТТЛ и КМОП.

Сравнительно небольшая амплитуда изменения выходного напряжения, т.е. низкая помехоустойчивость**.

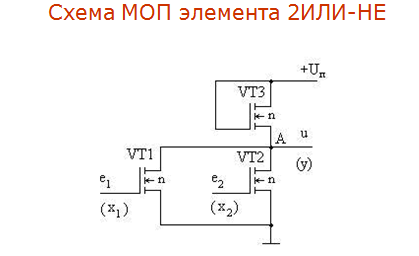

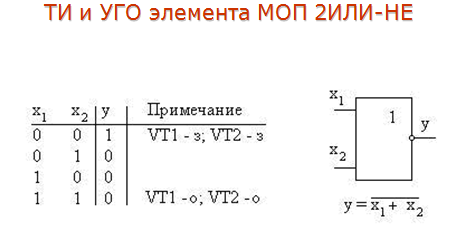

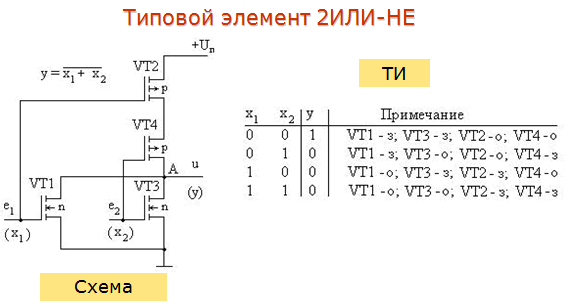

Элемент МОП ¾ ЛЭ, реализованный на полевых транзисторах, изготавливаемых по технологии металл – окисел – полупроводник. Применяются в микросхемах памяти ¾ (серии КМ132, КР565, К568 и др.).

№23Элементная

база цифровых микросхем: элемент МОП.

На слайдах 15 и 17 транзистор VT3 работает в линейном режиме и является нагрузкой переключательных транзисторов VT1 и VT2, которые соединены параллельно или последовательно.

ИМС МОП обладают средним быстродействием и средним энергопотреблением.

Элемент КМОП ¾ ЛЭ, реализованный на полевых транзисторах, изготавливаемых по технологии комплементарные* транзисторы - металл – окисел – полупроводник (серии К561, К564, К1561, К176).

№24Элементная база цифровых микросхем: элемент КМОП.

Выводы

Т.к. в схемах типовых элементов КМОП между "+" и "-" источника питания всегда включен хотя бы один закрытый транзистор, то КМОП ЛЭ отличаются ничтожно малым потреблением мощности источника питания (сотые доли мВт/бит).

ИМС на КМОМ–транзисторах отличаются средним быстродействием и хорошей нагрузочной способностью.

№25Особенности синтеза комбинационных цифровых устройств по заданной логической функции.

Порядок синтеза комбинационных устройств

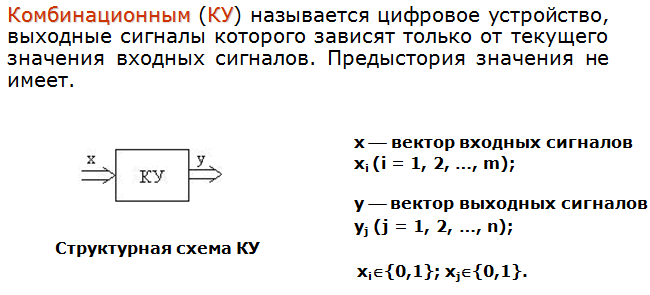

Процесс синтеза КУ устройств состоит из абстрактного и схемного синтеза.

Абстрактный синтез выполняется на основе анализа предметной области и состоит из следующих этапов

формирование задачи, словесное описание функций устройства, определение типа устройства;

описание устройства на формализованных языках (таблица истинности, карта Карно, аналитическое выражение);

минимизация булевых функций с одновременным учетом критерия Хаффмана;

построение логической (функциональной) схемы устройства.

В процессе схемного синтеза выполняется

переход в требуемый базис: чаще других в цифровой электронике применяются базисы Шеффера (И-НЕ) или Пирса (ИЛИ-НЕ);

построение принципиальной схемы, составление перечня элементов;

разработка монтажной схемы;

изготовление устройства и его испытание*.

№26Причины возникновения состязаний.

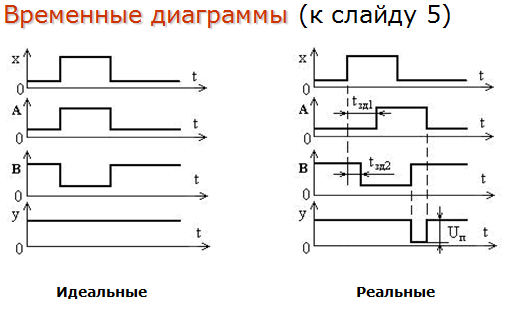

Идеальные временные диаграммы

Если КУ выполнено на базе идеальных, т.е. безинерционных элементов, то состояние выходов однозначно определяется состоянием входов в тот же момент времени.

Реальные временные диаграммы

Инерционность элементов приводит к задержке появления выходных сигналов КУ. При этом в переходный период возможно появление на выходах устройства некоторых промежуточных значений сигналов, не соответствующих заданному состоянию устройства. Такое явление получило название состязаний или гонок.

Обычно, вырабатываемые узлами КУ промежуточные значения сигналов, представляют собой импульсы очень малой длительности, являющиеся помехой для всей цифровой системы. Они могут приводить к непредусмотренным срабатываниям триггеров, счетчиков и осуществлять нежелательные записи в регистры.

Борьба с гонками

Применяется три основных способа борьбы с гонками

тактирование;

построение противогоночных схем;

учет минимального времени задержки распространения сигнала.

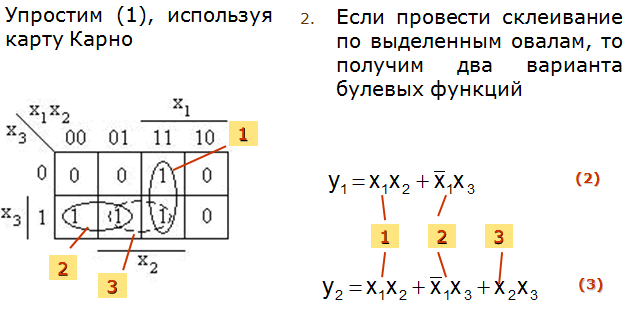

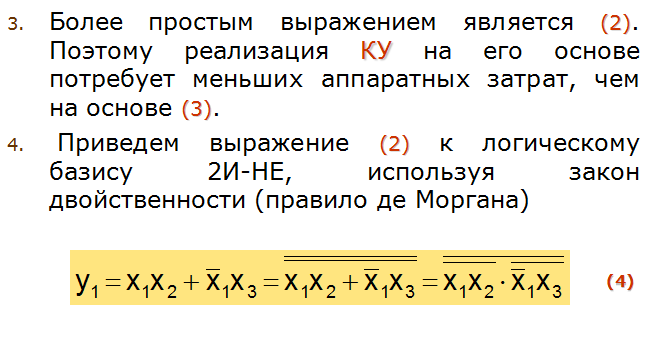

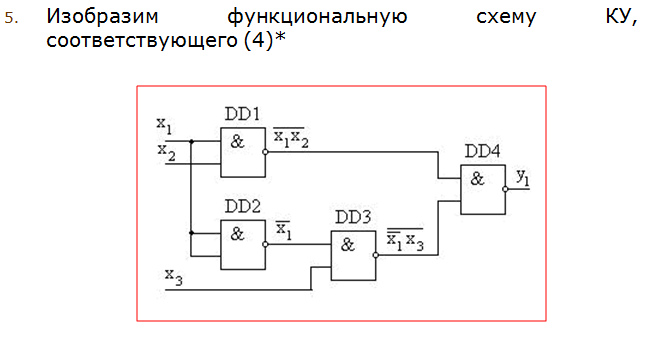

№27Пример синтеза цифрового комбинационного устройства.

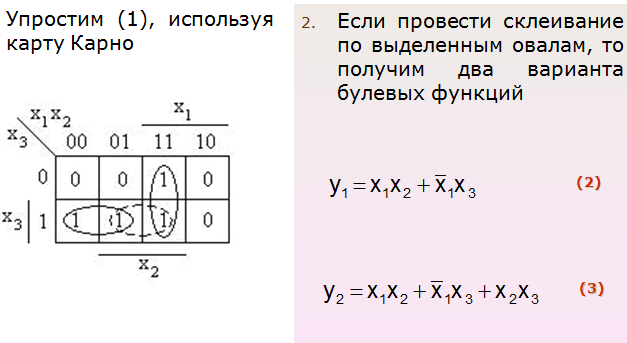

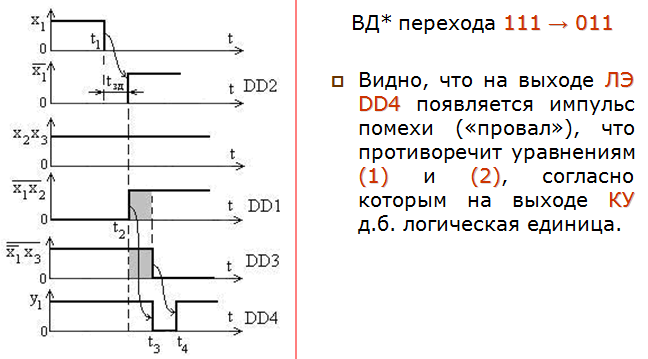

Рассмотрим возможные временные диаграммы КУ, изображенного на слайде 13, с учетом задержек при распространении сигналов по конкурирующим цепям схемы. Для этого переключим КУ из одного состояния в другое, где состоянию соответствуют значения переменных кортежа {x1, x2, x3}*.

Например, необходимо осуществить переход 111 → 011. Будем также полагать, что длительности фронта и спада импульсов равны нулю, т.е. t01=t10=0, а времена задержек (tзд) при прохождении каждого ЛЭ одинаковы.

№28Критерий Хаффмана.

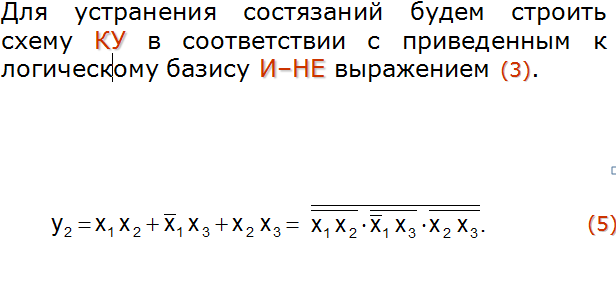

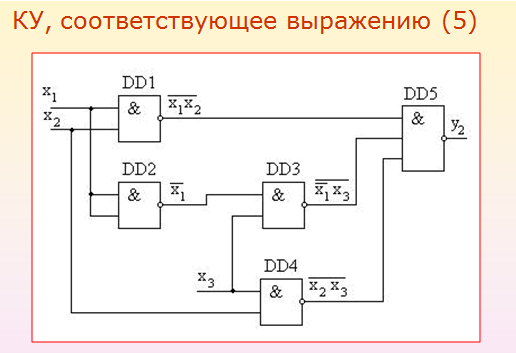

Явление состязаний исключается в противогоночной схеме (слайд 17), построенной на основании логического выражения (5), полученного с учетом критерия Хаффмана.

Критерий Хаффмана

Повышение функциональной надежности цифрового устройства достигается путем охвата соседних клеток на карте Карно овалом. Чтобы устранить ненадежность, необходимо склеить все соседние клетки, содержащие единицы.

Вывод

Усложнение КУ с целью повышения его функциональной надежности приводит к уменьшению электрической надежности и увеличению мощности, потребляемой от источника питания.

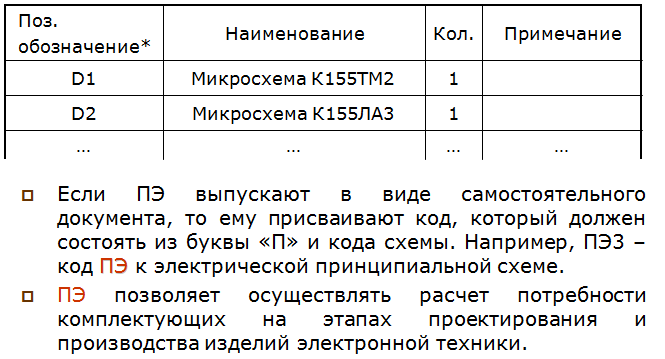

№29Перечень элементов к принципиальной схеме и его назначение.

Перечень элементов

Данные об элементах и устройствах, изображенных на схеме изделия, записывают в перечень элементов (ПЭ), который оформляют в виде таблицы*.

Связь между УГО и ПЭ осуществляется через позиционные обозначения.

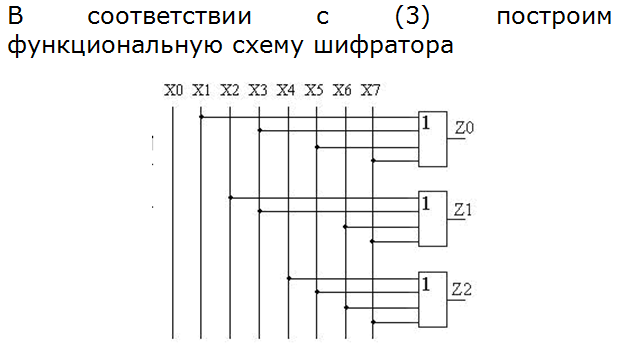

№30Цифровой шифратор.

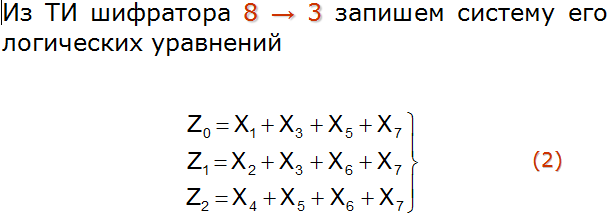

Шифратор (его аббревиатура «ИВ» или «CD») ― это комбинационное устройство (КУ), выполняющее преобразование позиционного, т.е. унитарного кода, в n разрядный двоичный код. Если принять, что M ― разрядность кода на входе CD, а m ― на его выходе, то должно выполняться неравенство

M>m

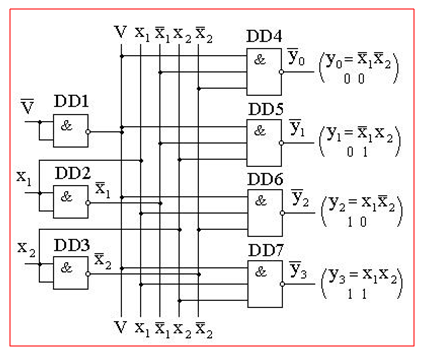

№31Цифровой дешифратор. Схема дешифратора 2 ® 4. Назначение входа разрешения.

Линейный или одноступенчатый дешифратор (аббревиатура «ИД» или «DC») ― это КУ, предназначенное для преобразования параллельного двоичного кода в унитарный, т.е. позиционный код.

В любой момент времени выходной сигнал будет иметь место только на одном выходе дешифратора.

В дешифраторах каждой выходной функции соответствует только один минтерм, а количество функций определяется количеством разрядов двоичного числа.

Если дешифратор реализует все минтермы входных переменных, то он называется полным дешифратором (пример неполного дешифратора ¾ дешифратор двоично-десятичных чисел).

В зависимости от типа дешифратора, этот сигнал может иметь как уровень логической единицы (при этом на всех остальных выходах уровень логического 0), так и уровень логического нуля (при этом на всех остальных выходах уровень логической 1).

Вход V’ ― вход разрешения включения микросхемы. При подаче на этот вход низкого уровня напряжения на все выходные элементы DD4…DD7 элементы поступают логические единицы и дешифратор готов к восприятию входного кода.

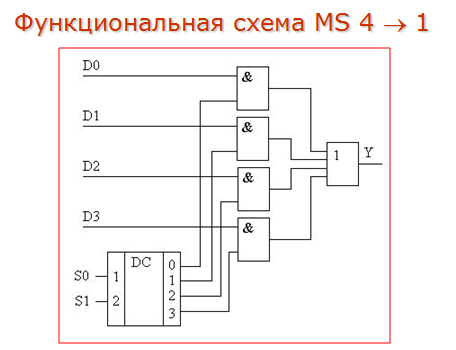

№32Мультиплексор, его назначение. Разновидности мультиплексоров. Схема мультиплексора 4®1. Уравнения функционирования мультиплексоров.

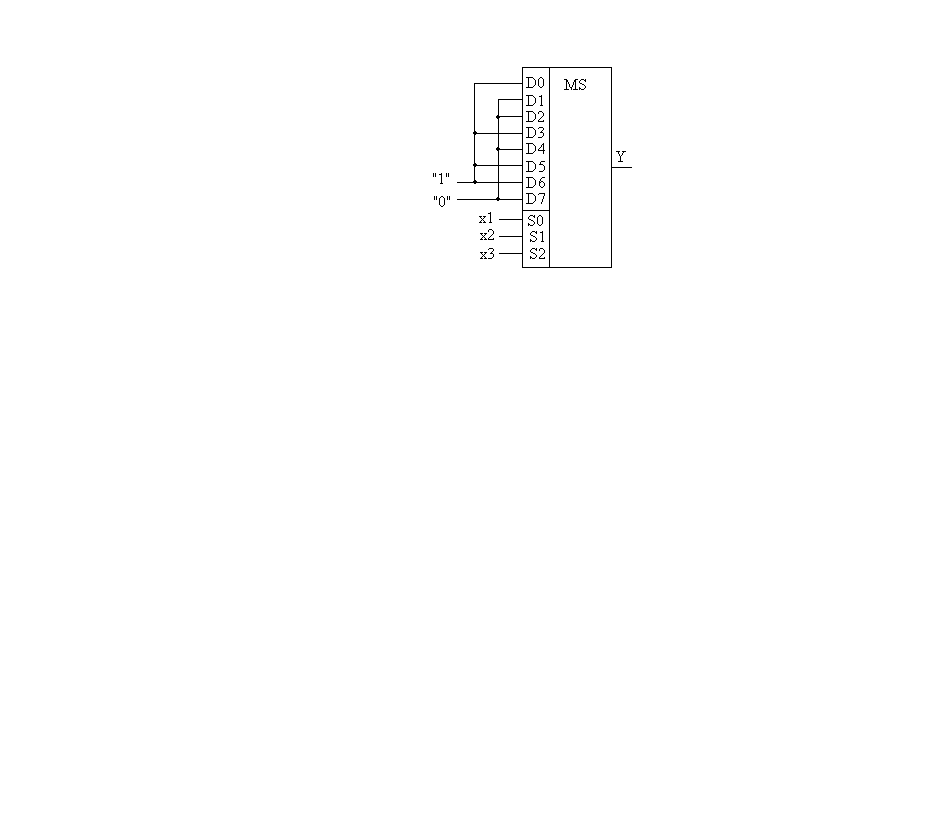

Мультиплексор (MS) ― коммутатор цифровых сигналов, представляющий собой КУ с m информационными, n управляющими входами и одним выходом. Функционально MS состоит из m элементов конъюнкции, выходы которых объединены дизъюнктивно с помощью элемента «ИЛИ», имеющего m входов. На одни входы всех конъюнкторов подаются информационные сигналы, а другие входы этих элементов соединены с соответствующими выходами дешифратора с n входами.

Мультиплексор имеет аббревиатуру «КП» (например, К555КП2). Количество управляющих (адресных) и информационных входов мультиплексора связаны соотношением

m=2n (1)

Обозначают мультиплексор: m®1 (2®1, 4®1, 8®1), учитывая, что MS является КУ, коммутирующим m входных каналов с одним выходным.

Число входов элементов «И» может быть равным двум.

Если возникает необходимость стробирования выходного сигнала MS импульсами независимого источника, то применяются элементы «И» с тремя входами. В этом случае один из входов каждого конъюнктора соединяется с общей линией, по которой подается сигнал разрешения работы MS (стробирующий сигнал).

Наличие дополнительного управляющего входа расширяет функциональные возможности MS и упрощает борьбу с гонками.

Из (2) видно, что на выход MS будет передаваться сигнал только с одного входа, номер которого совпадает с числом, соответствующим кодовой комбинации S0 и S1. Если S0=S1=0, на выход мультиплексора будет передаваться сигнал с входа D0. Когда на адресных (управляющих) входах S0=1 и S1=0, то на выход будет передаваться сигнал с входа D1 и т.д.

Применение MS

MS нашли широкое применение в вычислительной технике в качестве коммутаторов цифровых сигналов.

MS используются в компьютерах и микропроцессорных контроллерах для коммутации адресных входов динамических оперативных запоминающих устройств, в узлах объединения или разветвления шин и т.д.

На базе MS можно построить различные КУ с минимальным числом дополнительных элементов логики.

Хотя MS и предназначены для коммутации цифровых сигналов, но с помощью MS, изготовленных по КМОП технологии, можно коммутировать и аналоговые сигналы.

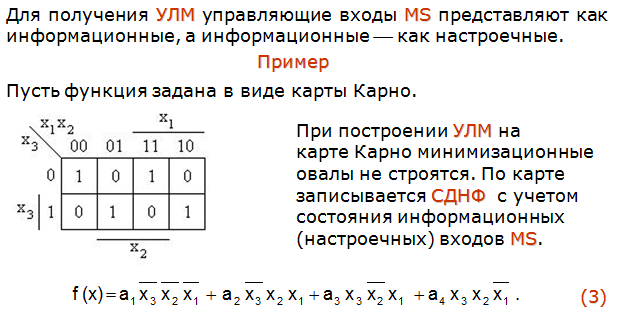

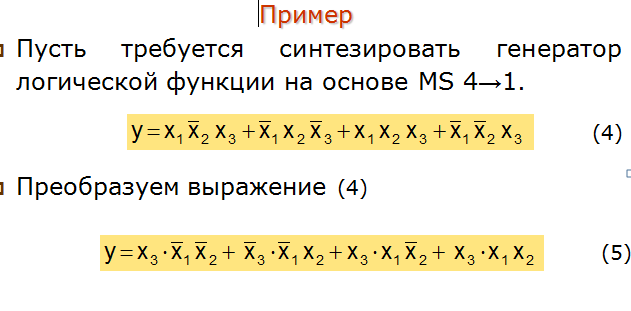

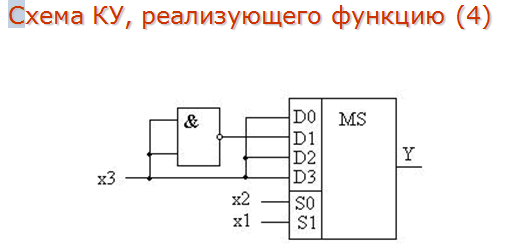

№33Мультиплексор как генератор логических функций.

Универсальные логические модули (УЛМ) на мультиплексорах

Кроме функции коммутации каналов MS позволяют реализовать КУ на n входов (где n —количество управляющих входов) и один выход.

Если КУ, построенное на базе MS, не требует подключения дополнительных элементов логики, оно называется УЛМ.

Например, MS 8®1 (n=3, m=8) позволяет реализовать любую функцию трех переменных.

Сопоставляя (3) с формулой MS, определяем соответствие коэффициентов «аi» информационным входам: D0=а1; D3=а2; D5=а3; D6=а4.

Т.к. слагаемые (3) ¾ конституенты единицы, то D0=D3=D5=D6=1.

Остальные значения настроечных коэффициентов нулевые: D1=D2=D4=D7=0.

На базе MS можно синтезировать КУ, которые могут реализовать функции на большее число переменных, чем количество управляющих (адресных) входов MS.

Сравним схемы КУ на MS 8®1 (слайд 22) и MS 4®1 (слайд 26).

Выводы

Схема на MS 4®1 потребляет меньшую мощность от источника питания.

Схема на MS 8®1 проще синтезируется.

Синтез КУ на MS по заданному выражению

(m>n)*

Пусть требуется синтезировать КУ, реализующее функцию m аргументов на MS с n управляющими входами и 2n информационными входами.

Тогда n младших переменных из набора Х1, Х2, …, Хm следует подать на управляющие входы, а информационные сигналы (настроечные) D0, D1, …, D2n-1 представить функциями остальных (m - n) переменных, как показано на рисунке (слайд 29).

Алгоритм действий при синтезе КУ на MS

Cоставить таблицу истинности КУ;

подать на управляющие входы MS младшие переменные;

представить информационные сигналы функциями остальных переменных и составить карту Карно для каждого информационного сигнала;

минимизировать логические выражения для сигнала на каждом информационном входе;

по логическим выражениям составить схему формирования сигналов, подаваемых на информационные входы MS.

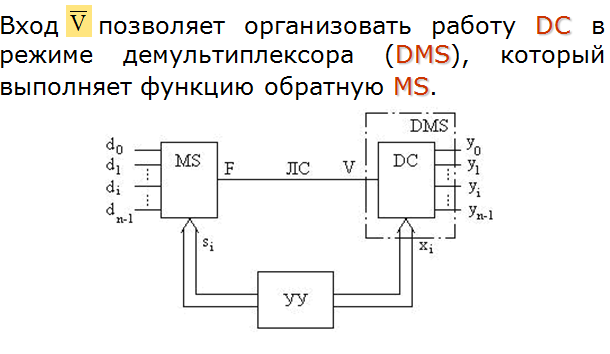

№34Работа дешифратора в режиме демультиплексора.

Устройство управления (УУ) формирует адресные коды для MS и DC.

Если на адресные входы системы поступают коды si и xi, то двоичный сигнал (последовательность прямоугольных импульсов или логических нулей и единиц), присутствующий на входе di, попадает в линию связи (ЛС) и на вход V DC.

Работа схемы

Микросхема DC включается/отключается по закону сигнала di и на выходе yi формируется последовательность, соответствующая входной.

Изменение адресных кодов по заданному алгоритму, позволяет опрашивать входы MS и коммутировать их с соответствующими выходами DC.

Вывод

Описанная система передачи данных от MS к DMS м. б. реализована только в том случае, если сигналы (коды) на адресных входах изменяются синфазно и синхронно

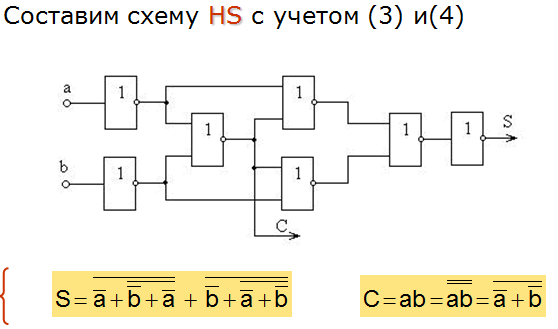

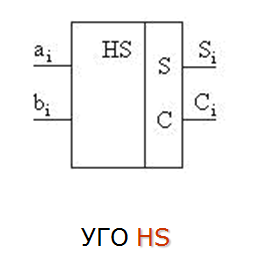

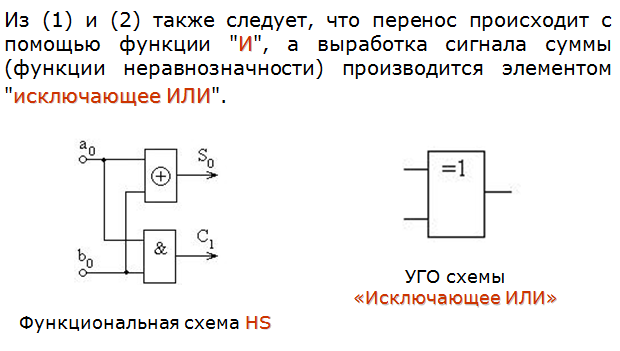

№35Цифровые полусумматор и сумматор.

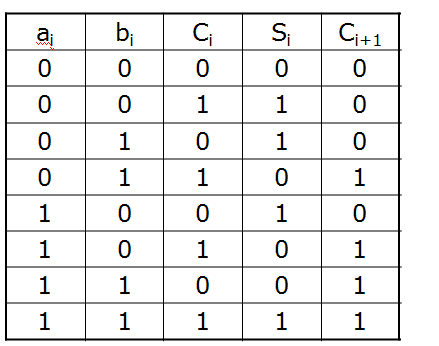

Сумматором или полным сумматором (SM) называется операционный узел ЭВМ, выполняющий операцию арифметического сложения двух чисел. SM, в отличие от HS должен воспринимать 3 входных сигнала: 2 слагаемых и сигнал переноса из предыдущего разряда.

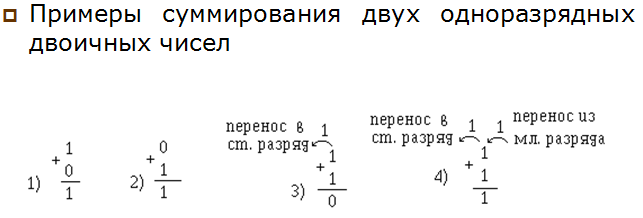

Выводы

Из примеров 1) … 4) видно, что если отсутствует перенос из младшего разряда, то перенос в старший разряд может быть только в том случае, когда оба числа равны единице. Если же имеется перенос из младшего разряда, то перенос в старший разряд будет всегда, кроме одного случая, когда оба слагаемых равны нулю.

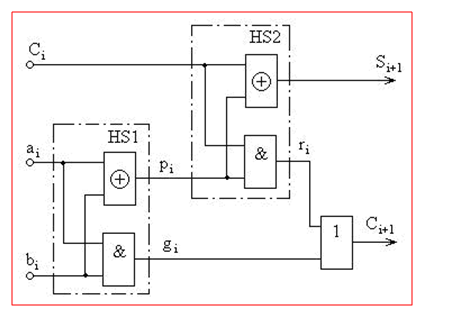

№36Схема полного сумматора.

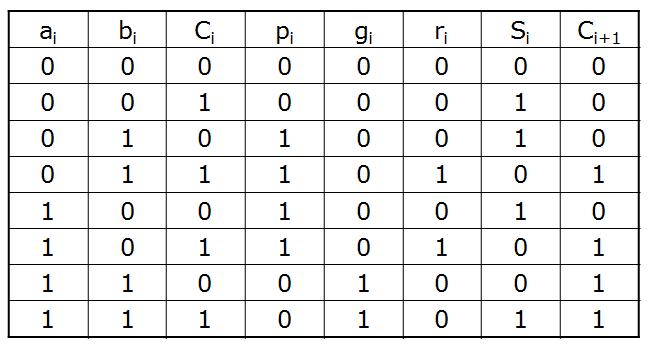

Схема SM м.б. реализована на двух HS, соединенных как указано на рисунке (слайд 12). В этой схеме выделим промежуточные сигналы рi, gi, ri.

Введем эти сигналы в новую таблицу функционирования.

Соответствие работы этой схемы и таблицы проверяется перебором всех возможных вариантов.

№37Многоразрядный сумматор с последовательным переносом