Задания на выполнение лабораторной работы

Задание 1. Исследование шифратора

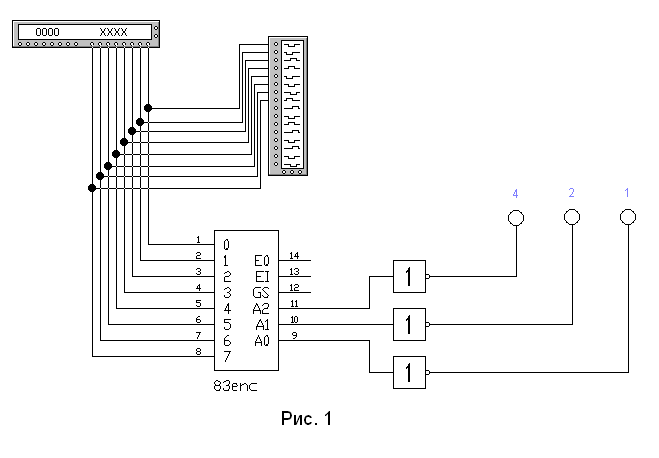

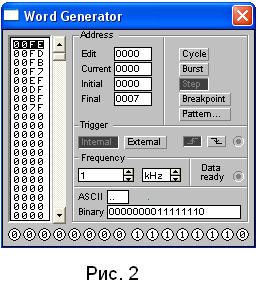

Собрать схему, показанную на рисунке 1. Входные сигналы задать в соответствии с рисунком 2. Исследования проводить в пошаговом режиме. Зарисовать временные диаграммы. Объяснить полученные результаты. По результатам исследования шифратора заполнить таблицу 1.

Табл. 1

Вход |

Показания индикатора |

|||||||||

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

1 |

2 |

4 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

|

|

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

|

|

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

|

|

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

|

|

|

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

|

|

|

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

|

|

|

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

Пояснение:

Задав последовательность сигналов в соответствии с рисунком 2, Вы получите следующее соответствие:

Шестнадцатеричное представление (колонка слов) |

Двоичное представление (графа Binary) |

00FE |

11111110 |

00FD |

11111101 |

00FB |

11111011 |

00F7 |

11110111 |

00EF |

11101111 |

00DF |

11011111 |

00BF |

10111111 |

007F |

01111111 |

Получается, что если мы установим значение 00DF – оно же 11011111, то на выходе генератора младший (1-ый) разряд выдаст логическую единицу, 2-ой, 3-ий, 4-ый, 5-ый, 7-ой, 8-ой разряды также выдадут единицу, а 6-ой разряд выдаст логический ноль.

Следовательно, на входы «0», «1», «2», «3», «4», «6», «7» шифратора поступит логическая единица, а на вход «5» - логический ноль. При такой комбинации сигналов на выходе шифратора будет: на «А0» и «А2» - логический ноль, на «А1» - логическая единица. Проинвертировав сигналы, мы можем наблюдать, что светодиод 1 и светодиод 4 будут «светиться», а светодиод 2 будет «потухшим».

Таким образом, мы на вход «5» подали логический ноль (активный сигнал для шифратора), это соответствует числу 5 в десятичной системе счисления, а получили (проинвертировав, чтобы облегчить восприятие закодированной информации в двоичном коде) активными 1-ый («А0») и 3-ий («А2») разряды, т. е. 101 в двоичной системе счисления. В итоге 5 (десятичн.) равно 101 (двоичн.). Всё верно, шифратор нам преобразовал число 5(D) в 101(B).

Задание 2. Исследование дешифратора

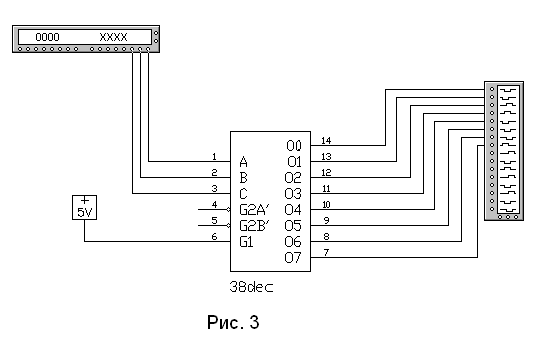

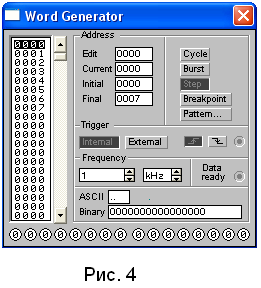

Собрать схему, показанную на рисунке 3. Входные сигналы задать в соответствии с рисунком 4. Исследование целесообразно проводить в пошаговом режиме. Зарисовать временные диаграммы. Объяснить полученные результаты. По результатам исследования дешифратора заполнить таблицу 2.

Табл. 2

Вход |

Выход |

|||||||||

C |

B |

A |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

0 |

0 |

1 |

|

|

|

|

|

|

|

|

0 |

1 |

0 |

|

|

|

|

|

|

|

|

0 |

1 |

1 |

|

|

|

|

|

|

|

|

1 |

0 |

0 |

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

1 |

1 |

1 |

|

|

|

|

|

|

|

|

Пояснение:

Задав последовательность сигналов в соответствии с рисунком 4, Вы получите следующее соответствие:

Шестнадцатеричное представление (колонка слов) |

Двоичное представление (графа Binary) |

0000 |

000 |

0001 |

001 |

0002 |

010 |

0003 |

011 |

0004 |

100 |

0005 |

101 |

0006 |

110 |

0007 |

111 |

Получается, что если мы установим значение 0003 – оно же 011, то на выходе генератора младший (1-ый) разряд выдаст логическую единицу, 2-ой разряд также выдаст единицу, а 3-ий разряд выдаст логический ноль.

Следовательно, на входы «А» и «В» дешифратора поступит логическая единица, а на вход «С» - логический ноль. При такой комбинации сигналов на выходе дешифратора будет: на «0», «1», «2», «4», «5», «6», «7» - логический ноль, на «3» - логическая единица.

Таким образом, мы на входы «А» и «В» подали логическую единицу, а на вход «С» - логический ноль, это соответствует числу 011 в двоичной системе счисления, а получили активным выход «3», т. е. 3 в десятичной системе счисления. В итоге 011 (двоичн.) равно 3 (десятичн.). Всё верно, дешифратор нам преобразовал число 011(B) в 3(D).

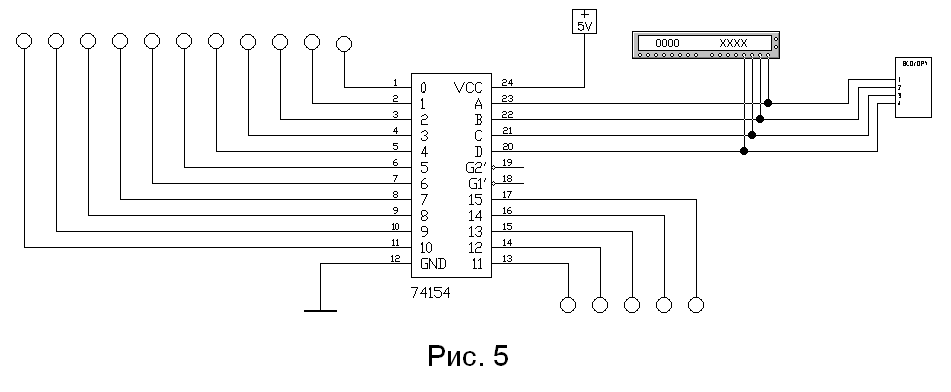

Задание 3. Исследование дешифратора 74154

Собрать схему, показанную на рисунке 5. Входные сигналы (шины A, B, C, D) последовательно изменять от 0 до 15D, представив их в двоичной системе счисления. Исследование целесообразно проводить в пошаговом режиме. По результатам исследования дешифратора 74154 заполнить таблицу 3.

Табл. 3

Вход |

Выход |

||||||||||||||||||

D |

C |

B |

A |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

15 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Пояснение:

Задав последовательность сигналов от 0 до 15D, Вы получите следующее соответствие:

Шестнадцатеричное представление (колонка слов) |

Двоичное представление (графа Binary) |

0000 |

0000 |

0001 |

0001 |

0002 |

0010 |

0003 |

0011 |

0004 |

0100 |

0005 |

0101 |

0006 |

0110 |

0007 |

0111 |

0008 |

1000 |

0009 |

1001 |

000A |

1010 |

000B |

1011 |

000C |

1100 |

000D |

1101 |

000E |

1110 |

000F |

1111 |

Получается, что если мы установим значение 0007 – оно же 0111, то на выходе генератора младший (1-ый) разряд выдаст логическую единицу, 2-ой и 3-ий разряды также выдадут единицу, а 4-ый разряд выдаст логический ноль.

Следовательно, на входы «A», «B» и «C» дешифратора поступит логическая единица, а на вход «D» - логический ноль. При такой комбинации сигналов на выходе дешифратора будет: на «0», «1», «2», «3», «4», «5», «6», «8», «9», «10», «11», «12», «13», «14», «15» - логическая единица, на «7» - логический ноль (активный выходной сигнал дешифратора 74154). Мы будем наблюдать, что светодиод, подключенный к выходу «7» будет «потухшим», в то время как остальные светодиоды будут «светиться».

Таким образом, мы на входы «A», «B» и «C» подали логическую единицу, а на вход «D» - логический ноль, это соответствует числу 0111 в двоичной системе счисления, а получили активным выход «7», т. е. 7 в десятичной системе счисления. В итоге 0111 (двоичн.) равно 7 (десятичн.). Всё верно, дешифратор нам преобразовал число 0111(B) в 7(D).

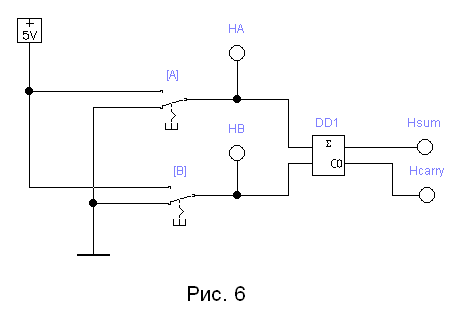

Задание 4. Исследование полусумматора

Собрать схему, показанную на рисунке 6. По результатам исследования полусумматора заполнить таблицу 4.

Табл. 4

A |

B |

Сумма ( ) |

Перенос ( ) |

0 |

0 |

|

|

0 |

1 |

|

|

1 |

0 |

|

|

1 |

1 |

|

|

Пояснение:

Принцип работы полусумматора предельно прост. Так, если на вход «A» подать логический ноль, а на вход «B» - логическую единицу (это соответствует 0(B) и 1(B)), то на выходе « » мы получим логическую единицу, а на выходе « » - логический ноль (т. е. мы получим число 01(B)). Таким образом, мы подали на вход два двоичных одноразрядных числа 0 и 1, а на выходе получили одно двухразрядное двоичное число 01. Проверим результат, выполнив сложение двух двоичных чисел «вручную»: 0 + 1 = 01. Всё верно.

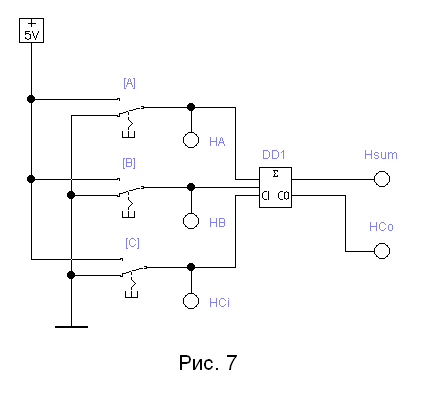

Задание 5. Исследование полного сумматора

Собрать схему, показанную на рисунке 7. По результатам исследования сумматора заполнить таблицу 5.

Табл.

5

Табл.

5

Вход |

Выход |

|||

A |

B |

Перенос ( ) |

Сумма ( ) |

Перенос ( ) |

0 |

0 |

0 |

|

|

0 |

0 |

1 |

|

|

0 |

1 |

0 |

|

|

0 |

1 |

1 |

|

|

1 |

0 |

0 |

|

|

1 |

0 |

1 |

|

|

1 |

1 |

0 |

|

|

1 |

1 |

1 |

|

|

Пояснение:

Принцип работы полного сумматор схож с принципом работы полусумматора. Отличие лишь в том, что в полном сумматоре имеется дополнительный вход – вход переноса младшего разряда. Следовательно, полный сумматор суммирует не два, а три двоичных одноразрядных числа.

Так, если на вход «A» и на вход « » подать логическую единицу, а на вход «B» - логический ноль (это соответствует 1(B), 0(B) и 1(B)), то на выходе « » мы получим логический ноль, а на выходе « » - логическую единицу (т. е. мы получим число 10(B)). Таким образом, мы подали на вход три двоичных одноразрядных числа 1, 0 и 1, а на выходе получили одно двухразрядное двоичное число 10. Проверим результат, выполнив сложение трёх двоичных чисел «вручную»: 1 + 0 + 1 = 10. Всё верно.