- •1.1 Понятие о логических функциях

- •Функции одной и двух переменных

- •2.1Булевы функции одной переменной

- •Булевы функции двух переменных

- •2.3 Понятие базиса и функционально-полного базиса

- •Основные аксиомы и тождества алгебры логики

- •Способы задания Булевых функций

- •3.1 Описательный способ:

- •3.2 Аналитический метод:

- •3.2.1Совершенная дизъюнктивная нормальная форма (сднф)

- •3.2.2 Совершенная конъюнктивная нормальная форма (скнф)

- •3.2.3Таблица истинности и последовательность значений наборов переменных

- •3.2.4 Геометрический способ представления функций алгебры логики (фал) (кубические комплексы)

- •3.2.5 Временные диаграммы

- •3.2.6 Функциональные схемы

- •3.2.7 Взаимные преобразования способов представления фал

- •4. Основные характеристики и параметры логических элементов

- •4.1 Цифровые устройства и их классификация (из инета)

- •4.2 Передаточные характеристики

- •4.3 Входная характеристика

- •4.4 Выходная характеристика

- •4.5 Нагрузочная способность

- •5. Базовые логические элементы

- •5.1 Структура логических элементов

- •5.1.1 Логические устройства диодной логики

- •5.1.2 Простой усилительно-формирующий каскад

- •5.1.3Сложный усилительно-формирующий каскад (двухтактный)

- •5.3 Ттлш-логический элемент

- •6. Синтез комбинационных устройств

- •6.1 Основные этапы неавтоматизированного синтеза комбинационных устройств.

- •6.2 Минимизация цифровых устройств

- •6.2.1 Аналитическая минимизация фал

- •6.2.2 Минимизация фал на основе карт Карно

- •6.2.3 Смысл и применимость методов минимизации при синтезе цифровых устройств.

- •6.3 Приведение фал к заданному базису.(и-не, или-не, и-или-не)

- •Типовые комбинационные устройства

- •7.1 Типовые комбинационные цифровые устройства.

- •Преобразователи кодов

- •Шифраторы (кодеры) и дешифраторы (декодеры)

- •Мультиплексоры и демультиплексоры (Концентраторы)

- •7.5 Сумматоры

- •Компараторы кодов

- •8 Последовательностные устройства

- •8.1 Обобщённая схема последовательностного устройства

- •8.2 Понятие об автоматах Мили и Мура

- •9 Триггеры

- •9.1 Классификация

- •9.2.1 Асинхронный rs-триггер

- •9.2.2 Синхронизируемый уровнем

- •9.2.4 Двухтактный rs-триггер

- •9.3.1 Асинхронный d–триггер

- •9.3.4 Двухтактный d–триггер

- •9.4.1 Асинхронный

- •9.4.2 Синхронизируемый уровнем

- •9.4.3 Синхронизируемый фронтом jk-триггер

- •9.4.4 Двухтактный jk-триггер

7.5 Сумматоры

Сумматор - устройство, выполняющее операции арифметического сложения над двоичными числами. Где-то рассматривались математические операции над двоичными числами, где говорилось о том, что сумма двух нулей есть нуль, сумма нуля и единицы есть единица, сумма двух единиц есть нуль. Одноразрядный цифровой сумматор имеет три входа: два входа слагаемых и вход переноса (от предыдущего сумматора). При этом правила сложения чуток усложняются. Одноразрядный сумматор обозначается так:

Рис.

1 - Одноразрядный цифровой сумматор

Рис.

1 - Одноразрядный цифровой сумматор

Сумматор имеет входы А и В - слагаемые, С - вход переноса, S - выход суммы, Р - выход переноса. Табличка истинности:

Входы |

Выходы |

|||

Слагаемые |

Вход переноса |

Сумма |

Выход переноса |

|

А |

B |

C |

S |

P |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

На выходе S представляется сумма сложения трех переменных - А, В, С. При переполнении сумматора, т. е. когда в результате сложения формируется единица в старшем разряде выходного числа, на выходе переноса Р формируется уровень лог. 1, который подается на вход переноса С следующего сумматора. В принципе, старшим разрядом суммы является выход переноса Р. В целом работу сумматора полностью иллюстрирует таблица. Из таких одноразрядных сумматоров составляются многоразрядные сумматоры (обычно 4-х разрядные), которые бывают последовательного и параллельного действия. Сумматоры последовательного действия обладают более низким быстродействие

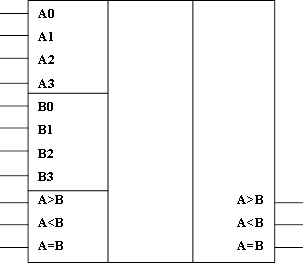

Компараторы кодов

Микросхемы компараторов кодов входных сигналов применяются для сравнения двух кодов и выдачи на выходе сигнала о результатах сравнения. Помимо 8 входов для сравниваемых кодов (2 четырехразрядных кода) компаратор имеет 3 управляемых входа для наращивания разрядности и 3 выхода результирующих сигналов.(рис. 1):

|

|

|

|

Рисунок

1

Рисунок

1

Если

используется одиночная микросхема, то

для ее правильной работы достаточно на

вход подать 1 на ![]() .

(на остальные можно подать либо 0, либо

1).

.

(на остальные можно подать либо 0, либо

1).

Если микросхемы компараторов каскадируются для увеличения числа разрядов сравниваемых кодов, то нужно выходные сигналы микросхемы, обрабатывающие младшие разряды подать на одноименные входы микросхемы, обрабатывающие старшие разряды кода.

Рисунок

2

Рисунок

2

Таблица истинности компаратора:

Входы сравнения |

Входы наращивания |

Выходы |

|||||||||

A3>B3 |

x |

x |

x |

x |

x |

x |

1 |

0 |

0 |

||

A3<B3 |

x |

x |

x |

x |

x |

x |

0 |

1 |

0 |

||

A3=B3 |

A2>B2 |

x |

x |

x |

x |

x |

1 |

0 |

0 |

||

A3=B3 |

A2<B2 |

x |

x |

x |

x |

x |

0 |

1 |

0 |

||

A3=B3 |

A1=B1 |

A1>B1 |

x |

x |

x |

x |

1 |

0 |

0 |

||

A3=B3 |

A1=B1 |

A1<B1 |

x |

x |

x |

x |

0 |

1 |

0 |

||

A3=B3 |

A2=B2 |

A1=B1 |

A0>B2 |

x |

x |

x |

1 |

0 |

0 |

||

A3=B3 |

A2=B2 |

A1=B1 |

A0<B0 |

x |

0 |

x |

0 |

1 |

0 |

||

A3=B3 |

A2=B2 |

A1=B1 |

A0=B0 |

1 |

1 |

0 |

1 |

0 |

0 |

||

A3=B3 |

A2=B2 |

A1=B1 |

A0=B0 |

0 |

1 |

0 |

0 |

1 |

0 |

||

A3=B3 |

A2=B2 |

A1=B1 |

A0=B0 |

x |

x |

1 |

0 |

0 |

1 |

||

- |

- |

- |

- |

1 |

1 |

0 |

0 |

0 |

0 |

||

- |

- |

- |

- |

0 |

0 |

0 |

1 |

1 |

0 |

||

- |

- |

- |

- |

0 |

0 |

0 |

1 |

1 |

0 |

||

Одно из основных применений компараторов состоит из селектирования кодов входных сигналов. В этом случае достаточно иметь информацию о совпадении и не совпадении кодов на входах компаратора, а не соотношение величин.

Интересующий нас код (эталонный) подается на один вход, а изменяющийся код на другой вход, при этом используют только равенство .

|

|

|

|

Рисунок 3 Селектирование 16-разрядных кодов

При применении компараторов нужно учитывать, что при каскадировании задержки микросхем суммируются и объединяемый компаратор будет настолько медленнее, сколько микросхем в нем используется.

Рис.4 Схема объединения компараторов для уменьшения задержки при каскадировании