Добавочные регистры

Четыре регистра системного адреса и четыре регистра управления определяют состояние устройства, влияющее на все задачи в системе. Регистры системного адреса TR, IDTR, ODTR и LDTR содержат адреса четырех специальных сегментов таблицы дескрипторов:

• регистр адреса состояния задачи (TR) указывает на сегмент состояния задачи;

• регистр адреса таблицы дескрипторов прерываний (IDTR) указывает на таблицу дескрипторов прерываний;

• регистр адреса таблицы глобальных дескрипторов (GDTR) указывает на таблицу глобальных дескрипторов;

• регистр адреса таблицы локальных дескрипторов (LDTR) указывает на таблицу локальных дескрипторов.

Регистры CRO — CR3 дополнительно определяют состояние микропроцессора 80386 (рис.2.7):

» регистр CRO содержит слово состояния устройства MSW (рис.2,7); » регистр CRI зарезервирован;

» регистры CR2 и CR3 служат для поддержки постраничной работы микропроцессора 80386. Эти два регистра используются вместе; CR2 содержит полный линейный адрес, вызвавший исключительную ситуацию на последней странице, а CR3 — адрес, указывающий детальную директорию страницы.

Слово состояния устройства

Первые пять разрядов 16-разрядного слова состояния устройства содержат: разряд 0 — разрешение защиты (РЕ), разряд 1 — сопроцессор монитора (МР), разряд 2 — эмуляция сопроцессора (ЕМ), разряд 3 — переключенная задача (TS), разряд 4 расширенный тип процессора (ЕТ) (рис. 2.7):

' разрешение защиты (РЕ) используется для активации защищенного режима в микропроцессоре. Если разряд РЕ сброшен, то микропроцессор работает в реальном режиме; если установлен, то активирован защищенный режим;

• сопроцессор монитора (МР) используется вместе с разрядом TS для определения, была ли вызвана ошибка недоступности сопроцессора по коду WAIT (т.е. TS - 1);

• эмуляция сопроцессора (ЕМ) устанавливается в случае всех кодов команд сопроцессора для выработки ошибки недоступности сопроцессора. Если разряд ЕМ равен 0, то все команды сопроцессора будут им (80287 или 80387) выполняться;

• переключенная задача (TS) всегда автоматически устанавливается при переключении задач. Если TS-1, то код команды сопроцессора вызывает ошибку недоступности сопроцессора;

« расширенный тип процессора (TS) показывает выбранный тип сопроцессора, 80287 или 80387.

Тестовые и отладочные регистры

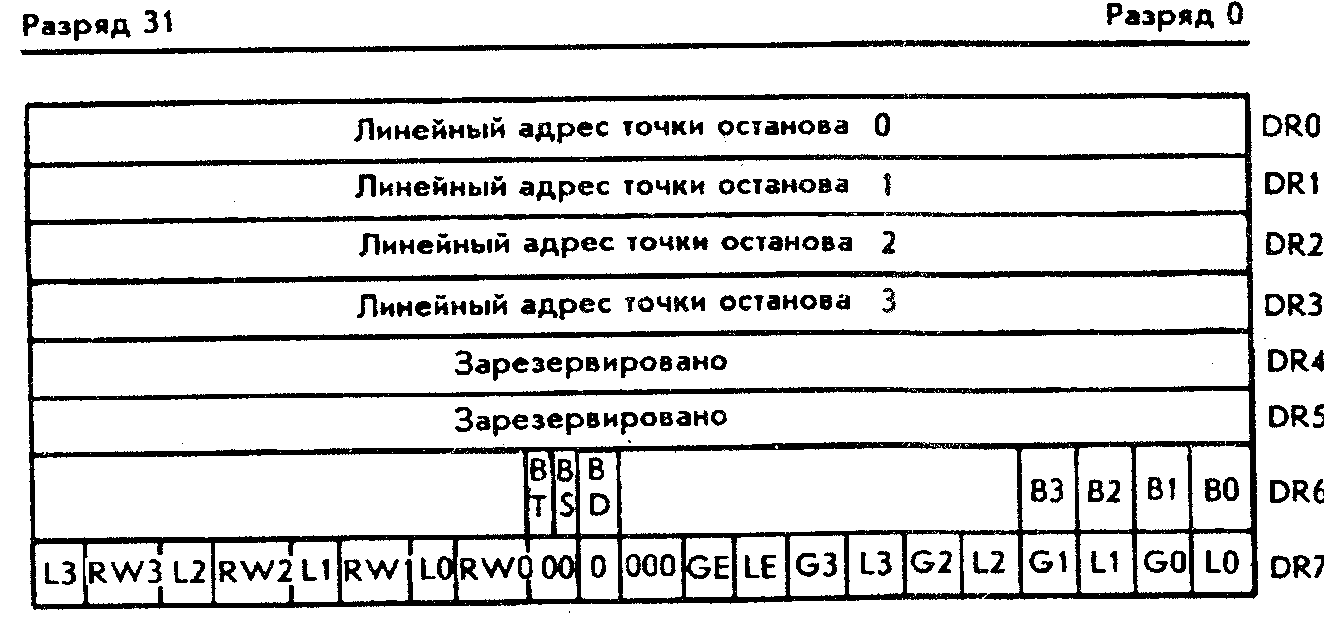

Регистры DRO, DRI, DR2, DR3, DR6, DR7 используются для управления при отладке (рис.2.8). Отладочные регистры 0"Ь4 и DR5 зарезервированы. Эти регистры могут быть задействованы только командой MOV на нулевом уровне привилегии.

Регистры DRO — DR3 содержат адреса, связанные с одним из четырех условий точки останова, определенных значениями разрядов в 'отладочном регистре DR7. Эти четыре регистра содержат линейные адреса, которые или являются физическим адресом, если запрещена постраничная организация, или переводятся микропроцессором 80386 в физический, если постраничная организация разрешена. Когда активизирована разбивка на страницы, регистр DR7 содержит разряды глобального и локального разрешения, определяющие соответствие адресов в 'регистрах DRO — DR3 задачам.

Отладочный регистр DR7 является управляющим: определяющим и по отдельности разрешающим или запрещающим условия отладки. Каждый адресный регистр отладки из DRO — DR3 имеет собственные поля: RWn — двухразрядное поле чтения-записи, Ln — двухразрядное поле длины, Ln и Gn — поля разрешения локальной и глобальной точек останова. Поля RWn интерпретируются следующим образом:

00 — останов только на выполнении команды,

01 — останов только на записи данных,

10 — пока не используется,

11 — останов на чтении или на записи данных, но не на вызове команды. Каждый регистр адреса DRO — DR3 также имеет соответствующее поле длины, определяющее размер единичной пересылки данных. Поле длины интерпретируется следующим образом:

00 — длина 1 байт,

01 — длина 2 байта,

10 — пока не используется,

11 — длина 4 байта.

Когда поле RWn сброшено в 00, соответствующее поле длины Ln также должно быть сброшено в 00.

Каждый регистр адреса также имеет два еще более взаимосвязанных поля: Gn и Ln. Эти поля показывают разрешения глобальной и локальной точек останова соответственно. Разница между ними заключается в том, что разрешение Ln сбрасывается микропроцессором при каждом переключении задачи во избежание нежелательных условий точек останова для новой задачи, в то время как Gn не изменяется при переключении задач.

Отладочный регистр DR6 содержит несколько флагов условий отладки, которые позволяют отладчику определить, какое из условий отладки удовлетворено. Когда выявлена разрешенная исключительная ситуация отладки, устанавливается соо^ает-с7вующий разряд Вп, Поле ВТ отладочного регистра DR6 работает вместе с отладочным разрядом ловушки в TSS. Поле ВТ устанавливается перед вводом программы отладки, если произошло переключение задач и установлен разряд ловушки в TSS. Разряд флага BS работает вместе с разрядом ловушки регистра EFLAGS. Флаг BS устанавливается, когда программа отладки вводится в качестве результата пошагового выполнения. Так как пошаговая ловушка имеет наивысший приоритет перед всеми исключительными ситуациями отладки, то любые другие разряды состояния отладки могут быть установлены, когда установлен разряд BS. Флаг разряда BD предназначен для индикации того, что следующая команда будет производить чтение или запись в один из восьми отладочных регистров. Микропроцессор никогда не сбрасывает разряды флагов в DR6. Нули записываются в DR6 перед попыткой идентифицировать следующую исключительную ситуацию отладки.

Техника адресации

Команда микропроцессора 80386 не только содержит информацию о необходимой операции, но и определяет тип операндов и их местонахождение. Существует девять основных режимов адресации:

• непосредственная; ' регистровая;

• прямая адресация к памяти; ' косвенная регистровая;

• относительная;

• прямая индексная; « относительная индексная с перемещением или без него;

• масштабирование; ' поразрядная.

Непосредственная адресация

По синтаксису команды микропроцессор определяет, какой адресный режим выбран. Например, в командах MOV АН.ОО MOV AL.04

значение операнда находится в самой команде. Здесь ^регистр АН обнуляется (0000), а в регистр AL загружается двоичный код 0100. Микропроцессор 80386 также допускает 32-разрядные операнды. Следующий пример иллюстрирует перемещение значения 32-разрядного операнда-источника в регистр ЕАХ (нуль должен находиться перед любым шестнадцатеричным числом):

MOV ЕАХ, OABCDFFFFH

При непосредственной адресации значения всех операндов при необходимости подвергаются знаковому расширению: значение старшего разряда операнда перемещают в ту же позицию, что и у операнда-приемника. Например, команда

MOV АХ.302

5ерет 10-разрядный двоичный эквивалент числа 302,0100101110, и расширяет его По 16-разрядной величины операнда-приемника, записывая нулевой разряд знака » старший разряд регистра АХ:0000000100101110.

Знаковое расширение применяется также для 8-разрядного операнда-источника и операнда-приемника. Например:

MOV AL,-40 Эта команда расширяет 7 разрядов числа 40, 1101000, до 8 разрядов -40, 11101000.

Непосредственный операнд может быть выражением, преобразуемым в число:

MOV EDX, OFFSET mydata + 50Н

Регистровая адресация

В режиме регистровой адресации значение операнда-источника предварительно запоминается в одном из внутренних регистров микропроцессора 80386. Это значение может составлять 8, 16 или 32 разряда. Микропроцессор определяет размер операнда по имени регистра. Например:

MOV ЕВХ, ЕАХ

означает, что микропроцессор берет 32-разрядное значение операнда-источника (регистр ЕАХ) и перемещает его в 32-разрядный регистр ЕВХ. В этом режиме используются также 8- и 16-разрядные регистры: MOV DS, АХ MOV DL, AL

Из девяти основных режимов адресации непосредственная и регистровая адресации выполняются за наименьшее число машинных циклов. Имея данные в самой команде или данные, уже запомненные во внутреннем регистре, микропроцессор избегает затрат на обращение к внешней памяти или внешним устройствам.

Семь оставшихся режимов адресации требуют большего времени выполнения, так как микропроцессору приходится вычислять адрес операнда по адресу сегмента, смещению сегмента и, возможно, по значению регистра базы или индексного регистра. Полученный таким образом адрес называется исполнительным адресом операнда, или ЕА.

Прямая или косвенная адресация

Сравним режимы прямой и косвенной адресации. В случае прямой адресации значение регистра, переменной, метки, константы или выражения, преобразуемого в константу, могут использоваться для получения исполнительного адреса (смещение относительно базы сегмента). Косвенная адресация включает в себя четыре следующих режима адресации:

косвенная регистровая, относительная, индексная, относительная индексная.

В этом случае косвенный адрес вычисляется из адреса ячейки памяти, указанной регистром базы или индекса, и может, кроме того, включать в себя необязательное перемещение. Для микропроцессора 80386 адресные смещения могут быть байтами, словами, двойными словами или словами тройной длины.

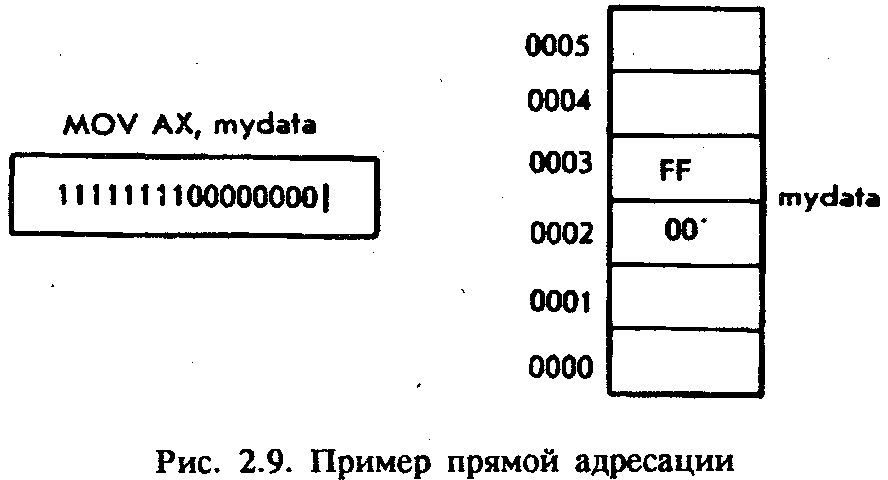

Прямая адресация к памяти

При прямой адресации' к памяти операндом является переменное имя или мет- : ка. Микропроцессор использует значение ячейки памяти, указанной с помощью этого имени или метки, как показано на следующем примере: ; MOV ЕВХ, myans 1 При прямой адресации к памяти сегментное смещение операнда содержится в 1 команде в виде 16-разрядного параметра. Это смещение прибавляется к сдвинутому значению регистра сегмента данных (DS), что дает 20-разрядный исполнительный -(ЕА) или физический адрес. Обычно в качестве операнда при прямой адресации i к памяти выступает метка (рис. 2.9). <

Согласно рисунку команда заставляет микропроцессор загрузить регистр АХ значением ячейки памяти, по адресу связанным с меткой mydata. Заметьте, что микропроцессор запоминает младший и старший байты данных по младшему и старшему адресам памяти соответственно.

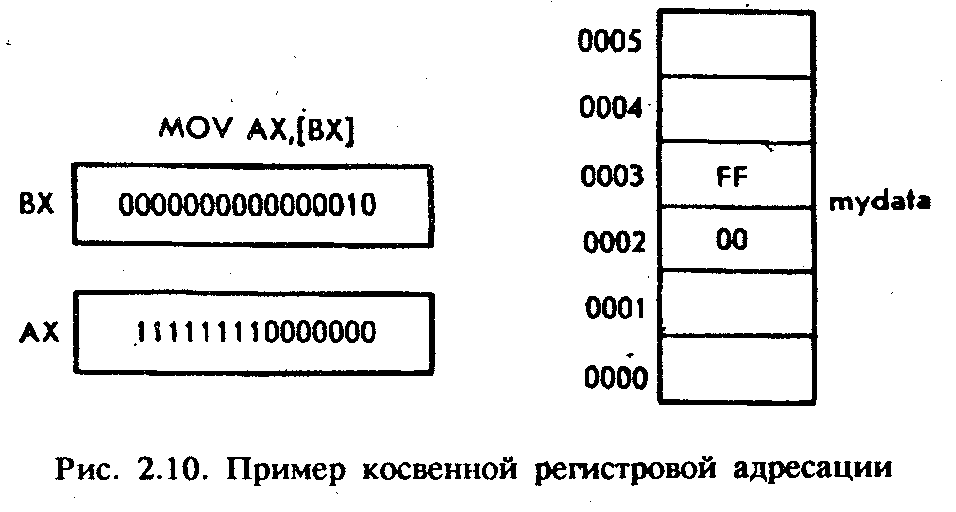

Косвенная регистровая адресация

При косвенной регистровой адресации вместо метки, указывающей адрес операнда-источника, используется значение операнда по адресу смещения, запомненного в специальном регистре. В качестве этого регистра обычно служит регистр индекса источника (SI), регистр индекса приемника (DI), регистр базы (ВХ), а иногда регистр указателя базы (ВР).

Микропроцессор распознает косвенную регистровую адресацию по синтаксису команды. Синтаксис определяется окружающими операнд-источник значками, например квадратными скобками, как показано на рис. 2.10.

В этом примере регистр ВХ должен содержать адрес смещения MYDATA. Адрес смещения может быть загружен оператором OFFSET:

MOV ВХ, OFFSET mydata или командой LEA (загрузить исполнительный адрес): LEA ВХ, mydata.

Косвенная регистровая адресация может служит для ссылок на данные, расположенные в форме таблицы. Этот режим предоставляет пользователю доступ к отдельным значениям увеличением содержимого регистра базы и выборкой ячейки памяти вместо вызова адреса из памяти и выборки операнда-источника.

Относительная адресация

Исполнительный адрес операнда в случае относительной адресации получается суммированием смещения и значения регистра базы 1(Е)ВХ или (Е)ВР] относительно выбранного сегмента. Смещение может быть 8- или 16-разрядным числом

для 16-разрядных команд и 8- или 32-разрядным числом для 32-разрядных команд. В режиме относительной адресации обычно выполняется доступ к комплексным структурам данных, таких как списки. Регистр базы указывает на базу структуры и на частичное поле, выбранное смещением: LEA ЁВХ, mydata; загрузка адреса базы mydata

Изменяя смещение, можно осуществить доступ к различным полям в списке, как показано следующей командой:

MOV ЕВХ, [ЕВХ+4]

Изменяя значение регистра базы, можно осуществить доступ к одним и тем же полям в разных структурах.

Прямая индексная адресация

В режиме прямой индексной адресации адрес смещения операнда вычисляется суммированием смещения и значения индексного регистра [(E)SI или (E)DI] внутри выбранного сегмента. Этот режим часто используется для доступа к элементам статического вектора. Значение смещения определяет начало вектора, а величина, записанная в индексном регистре, определяет конкретный элемент внутри структуры. В отличие от списков, где каждое поле может иметь различные размер и тип данных, элементы вектора имеют одинаковые размер и тип данных. Таким образом, перемещение по вектору происходит с помощью систематического увеличения или уменьшения смещения. Например: MOV ES1.4 MOV AX, ARAYI [ESI]

Необходима аккуратность при выборе значения смещения, соответствующего типу данных элементов вектора. В предыдущем примере в регистр АХ загружались данные из элемента 4 вектора ARAYI: MOV ЕАХ, ARAYI (SI]

В данном примере в 32-разрядный регистр АХ загружаются данные в зависимости от типа данных вектора. Для. 16-разрядных команд индексными могут служить только регистры SI и DI, Команды с 32-разрядными данными могут использовать любой из 32-разрядных регистров общего назначения, кроме ESP^

При работе микропроцессора 80386 по командам с 32-разрядными данными предполагается, что:

• когда для двух 32-разрядных регистров используется косвенный адрес, первый регистр предполагается регистром базы, второй — индексным регистром, если он не был масштабирован (см. масштабирование).,

• когда в косвенном адресе только один регистр определен как 32-разрядный, этот регистр предполагается регистром базы, если он не был масштабирован (cjm. масштабирование),

• когда в косвенном адресе используется масштабированный 32-разрядный регистр, то он предполагается индексным регистром, даже если это единственный заданный 32-разрядный регистр.

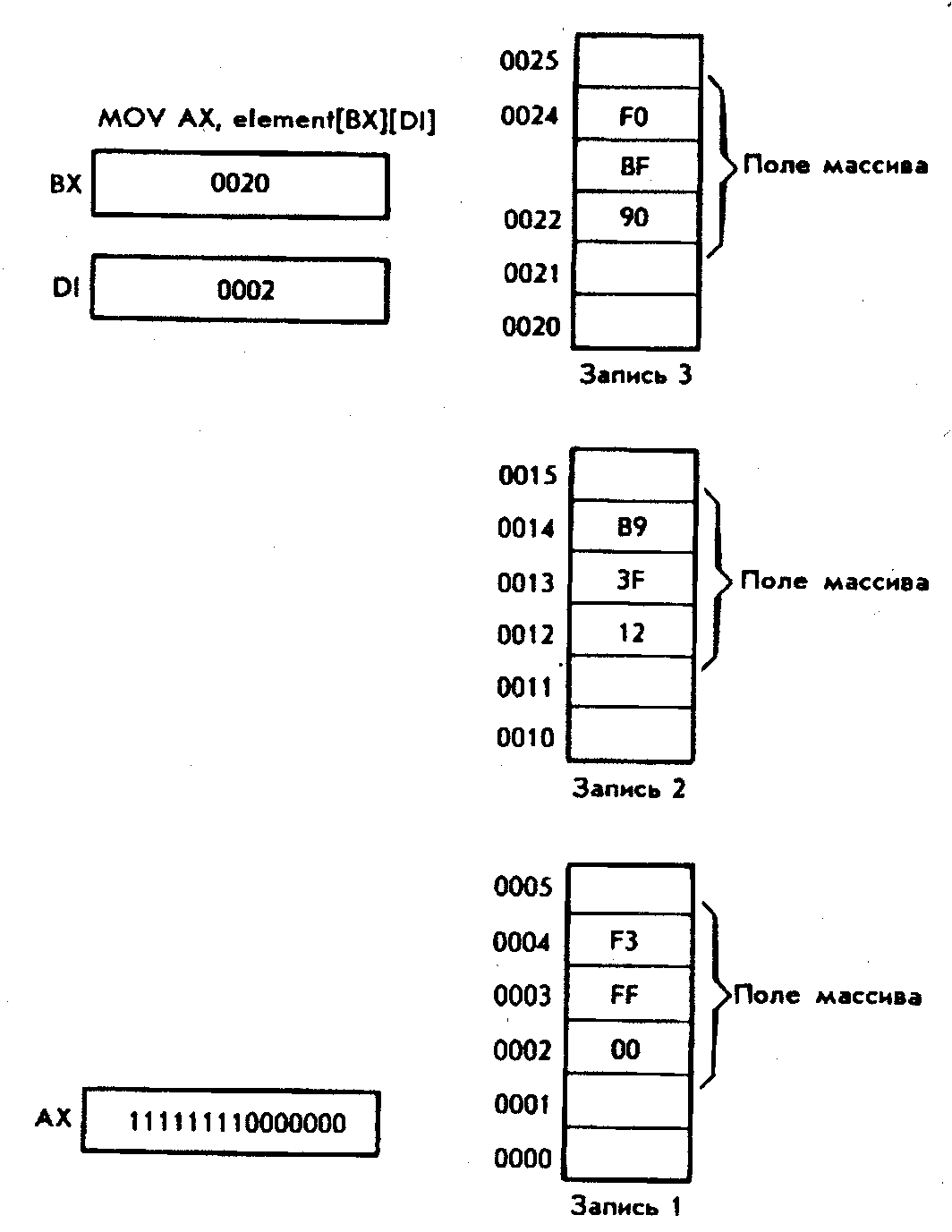

Относительная индексная адресация

При относительной индексной адресации операнд находится в выбранном сегменте и определяется суммой значений регистра базы, индексного регистра и необязательного смещения. Относительная индексная адресация без смещения обычно предназначается для доступа к элементам динамического вектора (вектора, адрес базы которого может меняться во время выполнения программы). Используя смещение, можно осуществить доступ к отдельному элементу вектора как к полю внутри структуры типа списка.

Для доступа к отдельным элементам, регистр базы указывает на базу структуры списка, а смещение (хранящееся в регистре DI) содержит расстояние между началом записи и началом поля вектора. Смещение элемента содержится в переменной элемента при условии, что элемент содержит 02 (рис. 2.11).

В этом примере адрес базы структуры списка 0020 находится в регистре ВХ. Поле вектора для третьей записи имеет смещение 0002 в регистре DI. Третий элемент поля вектора доступен с помощью смещения, содержащегося в инициализируемом значении элемента. Для команд над 16-разрядными операндами в качестве регистров базы могут быть использованы только регистры ВХ и ВР, а в качестве индексных — только SI и DI. Для команд над 32-разрядными операндами любой 32-разрядный регистр общего назначения может служить регистром базы, а любой 32-разрядный регистр общего назначения, за исключением ESP, — индексным регистром. В следующем разделе объясняется, как можно масштабирующий множитель использовать для индексного регистра.

Масштабирование

Масштабирование пригодно только для косвенной адресации 32-разрядных операндов из памяти. Масштабирование производится с помощью умножения величины, указанной индексным регистром, следующим образом: СИНТАКСИС: 32-разрядный регистр ' масштабирующий множитель