- •Лекция 8. Таймеры. Программируемы массив-счетчик pca. Режим широтно-импульсного модулятора

- •Таймеры 0 и 1

- •Параметры настройки таймеров в режиме 0

- •Режим 3: Два 8-битных таймера/счетчика (только для таймера 0)

- •Таймер 2

- •Таймер 3

- •Программируемый массив-счетчик рса

- •Режим переключений по фронту (Edge-triggered Capture Mode)

- •Режим программного счетчика (Software Timer (Compare) Mode)

- •Режим высокоскоростного выхода (High Speed Output Mode)

- •Режим широтно-импульсного модулятора (Pulse Width Modulator Mode)

- •Лекция 9. Источник опорного напряжения. Компараторы.

- •Лекция 10. Аналого-цифровые преобразователи adc

- •Восьмибитные аналого-цифровые преобразователи

- •Лекция 11. Последовательный периферийный интерфейс spi

- •Лекция 12. Шина can-bus

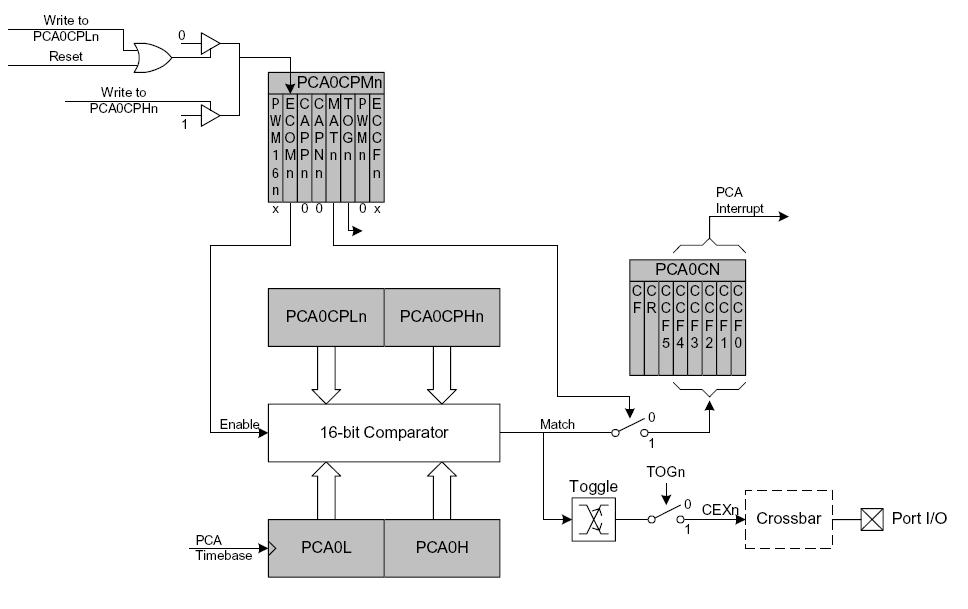

Режим высокоскоростного выхода (High Speed Output Mode)

В этом режиме (рис. 8.8) сравниваются

состояния счетчика РСА

и регистров РСА0СРНп и PCA0CPLn.

В момент совпадения происходит

установка встроенного триггера, сброс

которого происходит

по переполнению младшего байта счетчика

РСА. Режим настраивается

установкой битов TOGn,

MATn

и ЕСОМn

в регистре

РСАОСРМn.

этом режиме (рис. 8.8) сравниваются

состояния счетчика РСА

и регистров РСА0СРНп и PCA0CPLn.

В момент совпадения происходит

установка встроенного триггера, сброс

которого происходит

по переполнению младшего байта счетчика

РСА. Режим настраивается

установкой битов TOGn,

MATn

и ЕСОМn

в регистре

РСАОСРМn.

Рис. 8.8. Режим высокоскоростного выхода

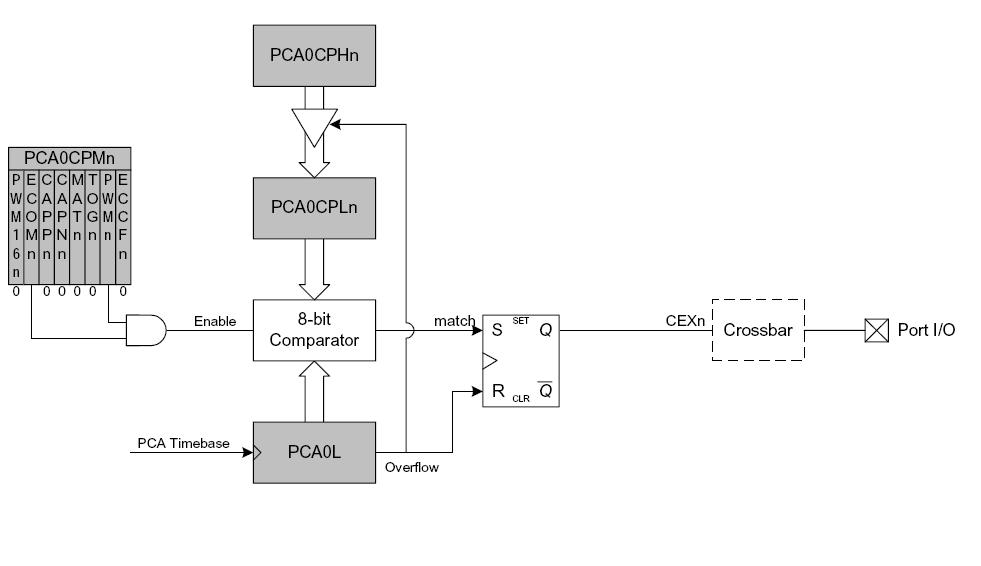

Режим широтно-импульсного модулятора (Pulse Width Modulator Mode)

Ф ункциональная

схема, поясняющая работу в этом режиме,

показана

на рис. 8.9. Все модули могут независимо

использоваться

для формирования PWM

сигналов и вывода их на соответствующие

вывода СЕХп. Очевидно, что выходная

частота зависит от заданного

источника входных импульсов, выбираемых

в узле TimeBase.

Параметры выходного сигнала определяются

настройкой

регистра PCA0CPLn.

Если код младшего байта PCA0L

счетчика

РСА равен величине PCA0CPLn,

соответствующий выход СЕХп устанавливается

в состояние логической единицы. При

переполнении байта PCA0L

выход СЕХп будет сброшен, а его значение

(байта PCA0L)

изменится с 0xFF

на 0x00. Кроме того, значение регистра

PCA0CPLn

будет аппаратно перезагружено из

РСА0СРНn.

ункциональная

схема, поясняющая работу в этом режиме,

показана

на рис. 8.9. Все модули могут независимо

использоваться

для формирования PWM

сигналов и вывода их на соответствующие

вывода СЕХп. Очевидно, что выходная

частота зависит от заданного

источника входных импульсов, выбираемых

в узле TimeBase.

Параметры выходного сигнала определяются

настройкой

регистра PCA0CPLn.

Если код младшего байта PCA0L

счетчика

РСА равен величине PCA0CPLn,

соответствующий выход СЕХп устанавливается

в состояние логической единицы. При

переполнении байта PCA0L

выход СЕХп будет сброшен, а его значение

(байта PCA0L)

изменится с 0xFF

на 0x00. Кроме того, значение регистра

PCA0CPLn

будет аппаратно перезагружено из

РСА0СРНn.

Рис. 8.9. Режим широтно-импульсного модулятора

Как уже отмечалось выше, шестнадцатибитный таймер/счетчик РСА состоит из двух восьмибитных регистров SFRs: PCA0L и РСА0Н. Регистр РСА0Н — старший (MSB), а регистр PCA0L — младший байт (LSB). Чтение регистра PCA0L автоматически защелкивает содержимое регистра РСА0Н для последующего чтения. Чтение этих регистров не нарушает ход текущей операции. Биты CPS1 и CPS0 регистра PCA0MD выбирают режим timebase, как показано в табл. 8.4.

Таблица 8.4

-

CPS1

CPS0

Источники сигналов узла Timebase

0

0

Системная частота, деленная на 12

0

1

Системная частота, деленная на 4

1

0

Переполнение таймера 0

1

1

Задний фронт импульса (перепад из высокого уровня в низкий) на взводе ECI, при этом максимально возможная скорость

Когда таймер/счетчик РСА переполняется, т. е. переходит из состояния 0xFFFF в 0x0000, флаг переполнения счетчика CF (Counter Overflow Flag) в регистре PCA0MD устанавливается в лог. 1 и генерируется соответствующее прерывание CF, если оно разрешено. Установка в 1 бита ECF в регистре PCA0MD разрешает генерацию CF прерывания при установке соответствующего флага. Бит CF не стирается аппаратно (автоматически) и должен быть очищен программно. Конечно, глобальные прерывания PCA0 должны быть разрешены (бит IE. 7 в регистре ЕА и бит EPCA0 в регистре EIE1 должны быть установлены) для генерации прерывания CF. Очистка бита CIDL в регистре PCA0MD разрешает продолжение функционирования РСА при переходе ядра в Idle режим энергосбережения.