- •Лекция 1. Основные характеристики микроконтроллеров фирмы SiLabs (Cygnal)

- •Лекция 2. Устройства визуального отображения информации

- •Система команд

- •Лекция 3. Микроконтроллерное ядро cip-51 фирмы silabs (cygnal)

- •Лекция 4. Подсистема прерываний, сброса, тактовых генераторов

- •Лекция 5. Многофункциональный генератор, подсистема управления питанием

- •Лекция 6. Встроенная память

- •Лекция 7. Программируемые линии (порты) ввода/вывода и коммутатор ресурсов crossbar

Лекция 7. Программируемые линии (порты) ввода/вывода и коммутатор ресурсов crossbar

Микроконтроллеры различных семейств имеют различное количество стандартных байтных портов ввода/вывода (от 1 до 8). Напомним, что стандартный микроконтроллер 8051 имеет четыре порта (Ports 0, 1, 2 и 3). Порты, не имеющие внешних выводов ввиду нехватки физических выводов корпусов, могут быть использованы как регистры общего назначения. Порты ввода/вывода ведут себя так же, как порты стандартного 8051, но имеют дополнительные функциональные возможности.

Каждая линия порта ввода/вывода может быть настроена как нормальная входная или выходная линия, как линия с «третьим» высокоимпедансным состоянием или как линия с «открытым истоком» через соответствующие регистры (Port Configuration Registers) PRTOCF, PRT1CF, PRT2CF, PRT3CF и т. д. Подтяжки уровней Pull-Up, обычно используемые в стандартных 8051 микроконтроллерах, могут быть программно запрещены с целью дополнительного энергосбережения.

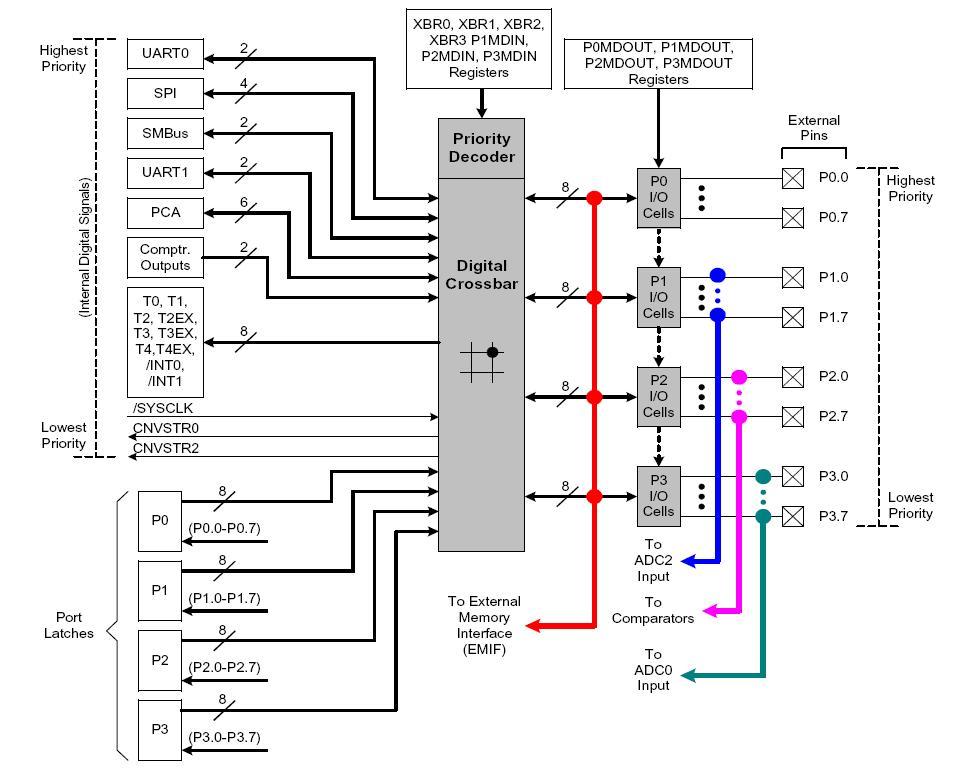

Несомненным достижением архитектуры микроконтроллеров фирмы SiLabs является наличие функционального узла, называемого Crossbar, выполняющего роль программно-управляемого коммутационного узла, переключающего периферийные внутренние ресурсы на линии ввода/вывода портов 0, 1 и 2. Иными словами, узел Crossbar - это коммутатор внутренних ресурсов. Это новшество значительно повышает гибкость разработки микроконтроллерной системы. Внутренние периферийные узлы, такие как таймеры, последовательные интерфейсы, прерывания, входы запуска ADC, выходы компараторов и другие цифровые сигналы, а в некоторых семействах и аналоговые входы ADC, могут быть программно назначены на выводы вышеуказанных портов. Спецификация портов осуществляется путем программирования специальных регистров XBRO, XBR1 и XBR2 и так называемой таблицы приоритетной перекодировки (Priority Decode Table). Рис. 7.1 иллюстрирует функциональное назначение Crossbar (на примере первых двух семейств C8051F04x).

Рисунок 7.1. Функциональное назначение Crossbar

Приоритетный дешифратор коммутатора ресурсов (Priority CrossBar Decoder)

Главной задачей разработчиков коммутатора ресурсов CrossBar являлось создание гибкой и удобной архитектуры, позволяющей проектировщику контроллеров оперативно выбирать и перераспределять богатые внутренние аналоговые и цифровые ресурсы на ограниченное число внешних выводов корпуса. Таблица приоритетного дешифратора коммутатора ресурсов индивидуальна для каждого семейства микроконтроллеров ввиду различного состава внутренней периферии. Однако методика выбора периферии одинакова для всех семейств. На рис. 7.2 в качестве примера показана таблица приоритетов дешифратора коммутатора ресурсов C8051F04x семейства.

Рисунок 7.2. Пример приоритетного дешифратора коммутатора ресурсов

В таблице по вертикали перечислены выводы всех периферийных устройств, которые могут быть выведены на вводы/вывода портов P0 - P2. Выводы периферийных устройств перечислены в порядке убывания приоритета. Например, наивысшим приоритетом обладает интерфейс UART0 с сигналами ТХ0 и RX0, далее SMBus, имеющий сигналы SDA и SCL, затем следует интерфейс SPI, имеющий сигналы SCK, MISO, MOSI и NSS, последовательный порт UART1 с сигналами ТХ1 и RX1 и т. д.

Выбор периферийных устройств осуществляется путем программирования специальных регистров XBR0, XBR1 и XBR2. Эти регистры содержат бит (или биты), определяющие активность каждого из приведенных на рис. 7.2 периферийных устройств. Например, включение в состав или выключение из состава периферийных устройств интерфейсов UART0, SMBus, SPI и UART1 осуществляется установкой или стиранием одного бита (для каждого интерфейса).

Методика определения активной периферии и соотнесение ее к конкретным портам ввода/вывода приведены ниже:

1. Проектировщик в регистрах XBRO, XBR1 и XBR2 устанавливает в лог. 1 биты, отвечающие за активность тех или иных периферийных устройств. Биты неиспользуемых периферийных устройств устанавливаются в состояние лог. 0.

2. Назначение выводов активных периферийных устройств всегда начинается с младших битов порта Р0. Далее при полном заполнении порта Р0 начинается заполнение порта Р1, а если его не хватит, то и Р2. Заполнение происходит в соответствии с приоритетом со сдвигом в сторону свободных младших выводов. Например, если устройство SMBus активно, то его сигналы за-нимают младшие разряды порта Р0: SDA — Р0.0; SCL — Р0.1 Если же устройство SMBus пассивно (выключено), а активно следующее устройство — SPI, то его сигналы занимают младшие разряды: SCK - Р0.0; MISO – Р0.1; MOSI - Р0.2; NSS –Р0.З. Если и устройство SPI пассивно, а активно устройство UART1, то его сигналы займут младшие разряды: ТХ — Р0.0; RX — Р0.1.

3. Следующие активные устройства всегда занимают более младшие свободные выводы портов Р0—Р2. Например, если первым активным устройством был интерфейс SPI и его сигналы заняли младшие разряды: SCK — Р0.0; MISO — Р0.1; MOSI — Р0.2; NSS — Р0.З.

4. Выводы, оставшиеся свободными после назначения активных периферийных устройств могут быть использованы как программируемые вводы/выводы общего назначения.

5. После назначения активных периферийных устройств необходимо разрешить работу (установить активность) CrossBar путем установки бита XBARE в регистре XBR2. Пока CrossBar не активен, все линии портов остаются в режиме ввода вне зависимости от назначений регистров XBRn.

Порты ввода/вывода

Выходные характеристики портов ввода/вывода устанавливаются в регистрах конфигурации портов (Port Configuration Registers): PRT0CF, PRT1CF, PRT2CF и PRT3CF. Каждый вывод может быть назначен как вывод «с открытым истоком» или как трехстабильный вывод. Это требуется даже для линий ввода/ вывода интерфейсов, назначенных в регистрах XBRn. Следует помнить, что только линии SDA и SCL интерфейса SMBus и линия RX в режиме 0 интерфейсов UART0 и UART 1 автоматически устанавливаются как линии «с открытым истоком». Бит WEAKPUD в регистре XBR2 отвечает за «слабую подтяжку» выходного уровня, если этот бит установлен в 0, то «слабая подтяжка» выходов осуществляется для всех линий портов, установленных в режим «с открытым истоком». С другой стороны, этот бит не действует на линии ввода/вывода, установленные как трехстабильные. Кроме того, «слабая подтяжка» выключается для выводов, находящихся в состоянии логического нуля, для исключения бесполезных потерь мощности. На рис. 7.3 показана функциональная схема одной линии порта

Рисунок 7.3. Функциональная схема линии порта

Как видно из схемы, так называемая «слабая подтяжка» (weak) представляет собой слегка приоткрытый полевой транзистор с высоким сопротивлением канала в открытом состоянии.

Микроконтроллеры фирмы SiLabs могут иметь от 1 до 5 однобайтных портов ввода/вывода (в зависимости от типа корпуса), которые могут использоваться для назначения линий ввода/ вывода периферийных встроенных устройств или как порты ввода/вывода общего назначения. Обращение к каждому такому порту осуществляется через соответствующий регистр SFR (Р0, Р1,...), доступный как побайтно, так и побитно. При записи в порт записанное значение защелкивается и выводится на соответствующие выводы. При чтении логические уровни порта могут быть прочитаны независимо от назначений, произведенных в регистрах XBRn. Исключением являются действия с инструкциями, выполняющими «чтение-модификацию-запись» (read-modify-write): ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ и MOV, CLR или SET, при которых адресуется непосредственный бит в порту SFR. При выполнении этих инструкций состояние регистра порта (но не состояние выводов) читается, модифицируется и записывается обратно в регистр.

В некоторых микроконтроллерах, имеющих корпуса с ограниченным количеством выводов, некоторые из портов могут не иметь своих выводов. Например, порты Р2 и РЗ не имеют выводов в микроконтроллерах F001/06/11/16, порты P1, P2 и РЗ не имеют выводов в микроконтроллерах F002/07/12/17. Однако эти порты остаются доступными для ядра CIP-51. В этом случае разработчику следует заботиться самому о корректном написании программы.