- •Устройство сетевого адаптера

- •Принцип работы сетевого адаптера Передача пакета

- •Режим мониторинга

- •Режим приема пакетов длиной менее 64 байт

- •Режим приема пакетов с ошибками

- •Буферная память

- •Протокол arp

- •Порядок преобразования адресов

- •Запросы и ответы протокола arp

- •Продолжение преобразования адресов

1

Устройство сетевого адаптера

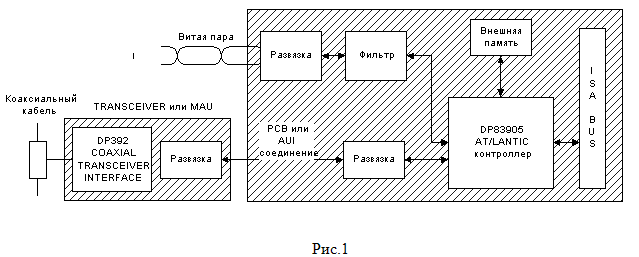

Структурная схема сетевого адаптера прадставлена на Рис.

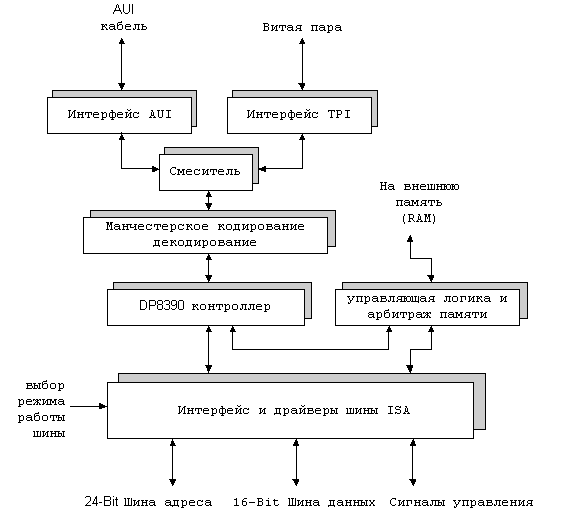

На плате сетевого адаптера расположены: устройства для согласования по волновому сопротивлению с различными типами физических сред, схема формирования и декодирования Манчестерского кода, буферная память

Основным элементом сетевого адаптера является контроллер. С его помощью осуществляется управление обменом между компьютером и внешней сетью Встроенный фильтр позволяет отфильтровывать чужие кадры. Встроенный буфер FIFO служит для временного хранения передаваемых и получаемых пакетов, буферная память образует промежуточный кольцевой буфер. Для обмена информацией с компьютером используется стандартный интерфейс ISA. (PCI).

2

Принцип работы сетевого адаптера Передача пакета

Для передачи пакет должен быть подготовлен в памяти в соответствии с IEEE 802.3 стандартом. Затем необходимо передать контроллеру начальный адрес пакета в памяти (TPSR), и длину пакета (TBCR0, TBCR1) и выставить в единицу TXP (transmit packet) бит командного регистра.

Если во время получения команды передачи не происходит приема пакета, начинается подготовка к передаче пакета. Данные передаются через локальный высокоскоростной DMA канал из буферной памяти в очередь контроллера (FIFO). После первой DMA передачи, если в сети нет несущей, выставляется TXE (transmit enable) сигнал запроса передачи и начинается передача пакета в сеть. После того, как будут переданы преамбула и начальный ограничитель кадра, данные в очереди разбиваются на группы и передаются в сеть. При этом вычисляется контрольная сумма. Если в очереди освобождается определенное число свободных байт (threshold), инициируется новая DMA передача из буферной памяти в очередь. Процесс продолжается до тех пор, пока счетчик переданных байт не достигнет нуля (TBCR0 и TBCR1). После передачи последнего байта данных передаются 4 байта вычисленной контрольной суммы, и передача пакета завершается. Если во время передачи были обнаружены конфликты, передача обрывается, передается jam последовательность (32 единицы, последовательность, сигнализирующая о возникновении помехи), которая используется узлами для подтверждения обнаружения конфликта, и передача пакета откладывается в соответствии с trunceted Binary Exponential Backoff Routine.

После завершения передачи вызывается прерывание, и выставляются PTX (complete packet transmitted) и TXE (packet transmit aborted) биты Interrupt Status регистра, сигнализирующие о результате передачи пакета. Программа обработки прерывания затем читает RSR (Receive Status регистр) и TSR (Transmit Status регистр) для получения детальной информации о результатах передачи.

Если установлен PTX бит, TSR регистр содержит информацию о наличии несущей в момент инициации передачи (DFR). TSR регистр устанавливает, имело ли место потеря несущей в процессе передачи (CRS), правильно ли отработал механизм обнаружения конфликтов (CDH) и возникали ли конфликты (COL). Число конфликтов содержится в NCR регистре. Если конфликты возникали вне 512-битного окна (slot time), OWC (Out of Window Collision) бит TSR регистра устанавливается в единицу.

Если установлен TXE бит ISR регистра, то при передаче либо возникло свыше 16 конфликтов, либо возникла “недогрузка” FIFO очереди контроллера. Если передача была оборвана из-за возникновения свыше 16 конфликтов, устанавливается ABT бит TSR регистра. Если же передача была оборвана в результате того, что отправка данных из очереди в сеть происходила быстрее передачи данных через DMA канал из буферной памяти в очередь, выставляется FU (FIFO Underrun) бит TSR регистра. Это может быть вызвано проблемами с системной полосой частот и указывает на ошибку в проектировании системы.

Прием пакета

Топология, используемая в CSMA/CD сетях позволяет любому узлу принимать любые пакеты, передаваемые по сети. Для определения нужного пакета используются специальные фильтры. Обычно узел интересуют только те пакеты, адрес назначения которых удовлетворяет приемным фильтрам узла. И только эти пакеты перемещаются в память.

После обнаружения несущей в сети (активен CRS сигнал), контроллер ждет последовательности чередующихся нулей и единиц (преамбулы) и двух последовательных единиц (SFD, начальный ограничитель кадра). После обнаружения SFD последовательности входящий поток разбивается на байты и помещается в очередь (FIFO). После получения первых 6 байт, представляющих собой адрес получателя пакета, они пропускаются через приемные фильтры узла и, если они соответствуют им, данные через локальный DMA канал передаются из очереди в буферную память карты. Если адрес получателя не соответствует фильтрам, прием прекращается и очередь сбрасывается. Каждый раз, когда очередь заполняется данными, они передаются через DMA в буферную память и очередь сбрасывается. Этот процесс продолжается до окончания пакета. По окончанию приема вызывается прерывание.

Всякий раз при обнаружении SFD (начальный ограничитель кадра) последовательности запускается CRC генератор. После каждого принятого байта вычисленная контрольная сумма сравнивается с последними принятыми четырьмя байтами. После того, как CRS сигнал сбрасывается, что означает окончание пакета, если вычисленная CRC сумма соответствует последними принятым четырем байтам, пакет считается хорошим и принимается. Если после окончания приема пакета контрольная сумма не совпадает, выставляется бит ошибки контрольной суммы (CRC бит RSR регистра), пакет считается плохим и отклоняется. Если по окончанию пакета CRS сигнал не сбрасывается и контрольная сумма не совпадает, выставляется бит ошибки выравнивания кадра (FAE бит RSR регистра). Ошибки выравнивания кадра возникают только вместе с CRC ошибками.

Проверка адресов

Первый бит, полученный после SFD последовательности, означает, что входящий пакет имеет физический или групповой адрес. Ноль соответствует физическому адресу, то есть уникальному 48-битному адресу каждого узла в сети, программируемому при начальной загрузке (PAR0-PAR5). Единица же означает групповой адрес, означающий, что пакет предназначен более чем одному узлу. Групповые адреса полезны, когда один узел хочет послать пакет одновременно нескольким узлам. Групповая адресация обеспечивает быстрый способ выполнять фильтрацию адресов в реальном времени, используя “on-chip” хэш-таблицу. Алгоритм хеширования, основанный на CRC (Cyclic Redundency Check) алгоритме, используется для отображения группового адреса на 64-битный фильтр групповых адресов (MAF0 – MAF7).

После вычисления CRC для адреса назначения, первые 6 бит полученного значения используются как индекс в фильтре групповых адресов (multicast address filter, MAF). Если соответствующий бит в фильтре равен единице, пакет принимается, иначе – игнорируется.

Широковещательный адрес является частным случаем группового адреса, когда адрес состоит из всех единиц. Широковещательный адрес означает, что пакет предназначен всем уздам сети. Широковещательный адрес также отображается на соответствующий бит MAF фильтра.

Контроллер также имеет возможность принимать все пакеты с любым физическим адресом назначения, передаваемые по сети. Такой режим называется “беспорядочным” и программируется PR0 битом RCR (recieve configuration register) регистра. Для получения всех групповых пакетов достаточно выставить все биты MAF фильтра в единицу.

Особые режимы приема пакетов