- •1. Классификация микропроцессоров различают :

- •3 Просуммировать числа 2, 3, 5, 7. Результат переслать по адресу 500н, используя косвенно – регистровую адресацию через регистр вх.

- •2 Составить программу для вычисления формулы:

- •3 Просуммировать содержимое всех регистров общего назначения. Результат переслать в область памяти, по адресу 300н, используя косвенно – регистровую адресацию через регистр di.

Билет 1

1. Классификация микропроцессоров различают :

1. Однокристальные микропроцессоры получаются при реализации всех аппаратных средств процессора в виде одной БИС или СБИС (сверхбольшой интегральной схемы).

2. Для получения многокристального микропроцессора необходимо провести разбиение его логической структуры на функционально законченные части и реализовать их в виде БИС (СБИС).

3. Многокристальные секционные микропроцессоры получаются в том случае, когда в виде БИС реализуются части (секции) логической структуры процессора при функциональном разбиении ее вертикальными плоскостями.

По назначению: универсальные и специализированные.

По виду обрабатываемых входных сигналов : цифровые и аналоговые.

По характеру временной организации работы микропроцессоры делят на синхронные и асинхронные.

По организации структуры микропроцессорных систем : микроЭВМ одно- и многомагистральные.

По количеству выполняемых программ : одно- и многопрограммные микропроцессоры.

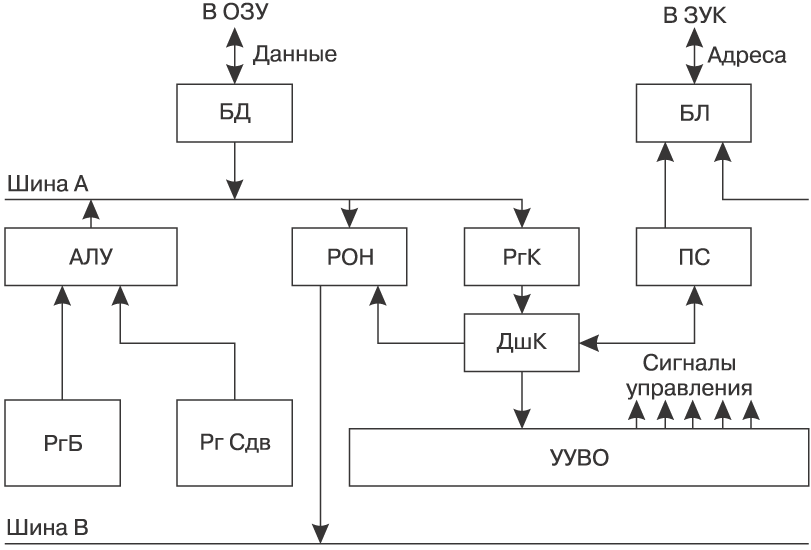

Структура микропроцессоров

РОН – регистры общего назначения; РгБ – буферный регистр; РгСдв – сдвиговый регистр; АЛУ – арифметико-логическое устройство; УУВО – устройство управления выполнением операций; ДшК – дешифратор команд; РгК – регистр команд; ПС – программный счетчик; БД – буфер данных; БА – буфер адреса; ОЗУ – оперативное запоминающее устройство; ЗУК – запоминающее устройство команд.

Основные характеристики микроконтроллеров

При классификации микроконтроллеров используются признаки микропроцессорного ядра и признаки, относящиеся к другим элементам архитектуры: память, порты и т.д. По признакам микропроцессорного ядра микроконтроллеры и собственно микропроцессоры могут быть разделены на следующие основные группы:

-

CISC (Complete Instruction Set Computing - вычисления с полным набором команд) RISC (Reduce Instruction Set Computing - вычисления с сокращённым набором команд.

-

с архитектурой фон Неймана – память программ и память данных находятся в едином пространстве адресов и нет никаких признаков, указывающих на тип информации в ячейке памяти, кроме контекста программы;

-

с архитектурой Гарвардской лаборатории – память программ и память данных разделены, имеют свои адресные пространства и способы доступа к ним;

-

с фиксированной разрядностью и фиксированным списком команд (однокристальные);

-

с наращиваемой разрядностью (секционные) и микропрограммным управлением, позволяющим разработчику создавать собственные машинные команды, дополняющие начальный список;

-

с преобладающей регистровой архитектурой и развитой системой регистровой адресации;

2 составить программу

х + 2х х> 20

15

IN

WR 30

SUB #20

JS M1

RD 30

MUL #2

ADD 30

DIV #15

OUT

M1: HLT

-

Переслать числа 1, 3, 7, в область памяти, начиная с адреса 100Н, используя регистрово – косвенную адресацию DI.

MOV AX,1

MOV BX,3

MOV CX,7

MOV DI,100H

MOV [DI],AX

INC DI

MOV [DI],BX

INC DI

MOV [DI],CX

HLT

-

Описать D - триггер на VHDL

library IEEE;

use IEEE.std_logic_1164.all;

entity dff is

port (data, clk : in std_logic;

q :out std_logic);

end dff;

architecture behav of dff is

begin

process (clk) begin

if (clk'event and clk = '1') then

q <= data;

end if;

end process;

end behav;

Билет 2

1 Система команд микропроцессора. Микропроцессоры с RISC- и CISC-архитектурой

Система команд микропроцессора:

Команды передачи данных (перепись), копирующие информацию из одного места в другое.

Арифметические операции, к которым в основном относят операции сложения и вычитания. Умножение и деление обычно реализуется с помощью специальных программ.

Логические операции, позволяющие компьютеру производить анализ получаемой информации. Простейшими примерами команд рассматриваемой группы могут служить сравнение, а также известные логические операции и, или, не.

Сдвиги двоичного кода влево и вправо. В некоторых случаях сдвиги используются для реализации умножения и деления.

Команды ввода и вывода информации для обмена с внешними устройствами. В некоторых ЭВМ внешние устройства являются специальными служебными адресами памяти, поэтому ввод и вывод осуществляется с помощью команд переписи.

Команды управления, реализующие нелинейные алгоритмы. Сюда относят условный и безусловный переходы, а также команды обращения к подпрограмме (переход с возвратом).

CISC-процессоры выполняют большой набор команд с развитыми возможностями адресации, давая разработчику возможность выбрать наиболее подходящую команду для выполнения необходимой операции. В применении к 8-разрядным МК процессор с CISC-архитектурой может иметь однобайтовый, двухбайтовый и трехбайтовый (редко четырехбайтовый) формат команд. При этом система команд, как правило, неортогональна, то есть не все команды могут использовать любой из способов адресации применительно к любому из регистров процессора. Выборка команды на исполнение осуществляется побайтно в течение нескольких циклов работы МК. Время выполнения команды может составлять от 1 до 12 циклов.

В процессорах с RISC-архитектурой набор исполняемых команд сокращен до минимума. Для реализации более сложных операций приходится комбинировать команды. При этом все команды имеют формат фиксированной длины (например, 12, 14 или 16 бит), выборка команды из памяти и ее исполнение осуществляется за один цикл (такт) синхронизации. Система команд RISC-процессора предполагает возможность равноправного использования всех регистров процессора. Это обеспечивает дополнительную гибкость при выполнении ряда операций.

2 Составить программу для вычисления формулы:

Х – 645 х < = 8

5х + 3

IN

WR 30

SUB #8

JS M1

RD 30

SUB #645

WR 31

RD 30

MUL #5

ADD #3

WR 32

RD 31

DIV 32

OUT

M1: HLT

3 Просуммировать последовательность из 4–х однобайтовых чисел, расположенных в области памяти, начиная с адреса 100Н. Результат поместить в аккумулятор.

MOV AX,1

MOV BX,2

MOV CX,3

MOV DX,4

MOV [DI], 100H

MOV [DI],AX

INC DI

MOV [DI],BX

INC DI

MOV [DI],CX

INC DI

MOV [DI],DX

MOV AX ,[DI]

DEC DI

ADD AX,[DI]

DEC DI

ADD AX,[DI]

DEC DI

ADD AX,[DI]

HLT

4 Описать RS - триггер на VHDL

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY srlatch IS

PORT(sn, rn : IN STD_LOGIC

q: OUT STD_LOGIC);

END ENTITY;

ARCHITECTURE s OF srlatch IS

SIGNAL q_internal : STD_LOGIC;

SIGNAL nq_internal : STD_LOGIC;

BEGIN

q_internal <= sn nand nq_internal;

nq_internal <= rn nand q_internal;

q <= q_internal;

END ARCHITECTURE;

Билет 3

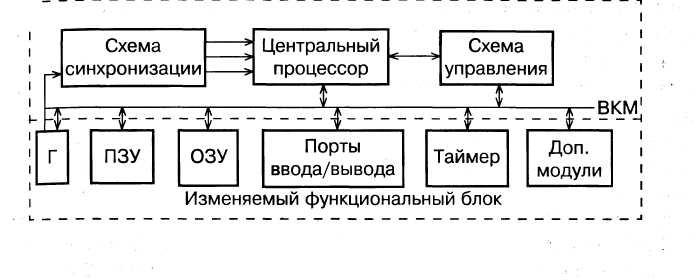

1 Модульная организация микроконтроллеров. Минимизация энергопотребления в системах микроконтроллеров

Структура модульного МК приведена на рисунке

Процессорное ядро включает в себя:

- центральный процессор;

- внутреннюю контроллерную магистраль (ВКМ) в составе шин адреса, данных и управления;

- схему синхронизации МК;

- схему управления режимами работы МК, включая поддержку режимов пониженного энергопотребления, начального запуска (сброса)

2 Составить программу для вычисления формулы:

Х + 245 х < 16

6х – 7

IN

WR 30

SUB #16

JS M1

RD 30

ADD #245

WR 31

RD 30

MUL #6

SUB #7

WR 32

RD 31

DIV 32

OUT

M1: HLT