- •Карты программированного контроля

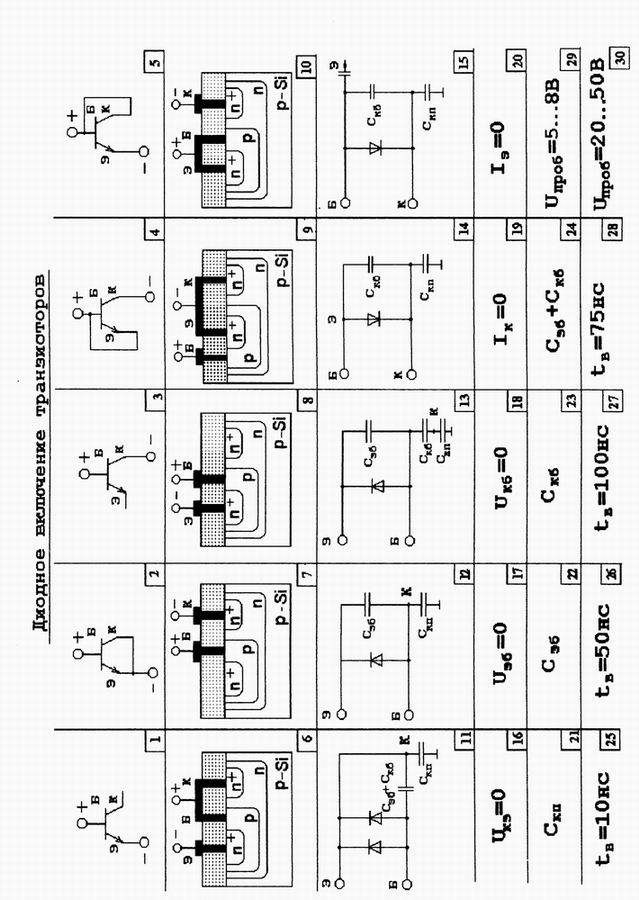

- •Изоляция элементов

- •Биполярный транзистор

- •Диоды полупроводниковых микросхем

- •Схемотехника интегральных логических элементов

- •Логические элементы на мдп-транзисторах

- •Классификация триггеров

- •Тактируемый триггер (rst-триггер)

- •Триггер со счётным входом (т–триггер)

- •Триггер задержки (d-триггер)

- •Универсальный jk-триггер

- •Триггер Шмитта

- •Оптоэлектронные приборы 1 Оптоэлектронные приборы 2

- •Виды оптоэлектронных индикаторов

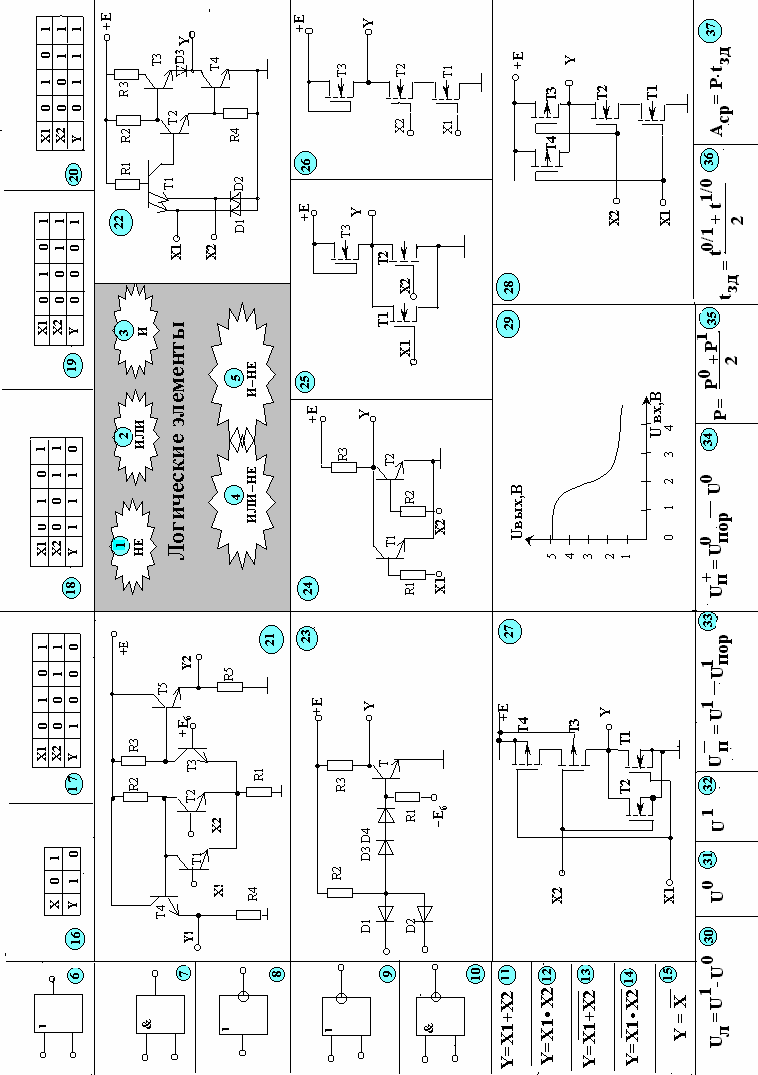

Схемотехника интегральных логических элементов

Схема РТЛ (транзисторная логика с резистивной связью) – рис. 24.

Схема

ДТЛ (диодно-транзисторной логики)

показана на рис. 23. Если на оба входа

подан высокий положительный потенциал

(X1

= X2

= 1), то входные

диоды будут закрыты, ток от плюса

источника питания потечет через Д3

и Д4

в базу транзистора. Транзистор переходит

в режим насыщения; при этом напряжение

коллектора уменьшается до величины

остаточного напряжения, т.е. Y

= 0.Если хотя

бы на одном входе низкий уровень

(например, X1

= 0), то входные

диоды открыты и ток течет от плюса

источника в коллектор предшествующей

схемы. Поскольку напряжение на открытом

диоде падает

![]() В,

на базе транзистора с учетом диодов Д3

и Д4

будет отрицательный потенциал. Транзистор

закрыт, напряжение коллектора почти

равно напряжению питания Е,

т.е. Y =

1. Таким образом, схема ДТЛ выполняет

логическую операцию И–НЕ.

Размах логического сигнала

В,

на базе транзистора с учетом диодов Д3

и Д4

будет отрицательный потенциал. Транзистор

закрыт, напряжение коллектора почти

равно напряжению питания Е,

т.е. Y =

1. Таким образом, схема ДТЛ выполняет

логическую операцию И–НЕ.

Размах логического сигнала

![]() и практически не зависит от нагрузки,

т.к. ток нагрузки втекает в коллектор

через диоды последующей схемы. Нагрузочная

способность ДТЛ n=10,

время задержки

и практически не зависит от нагрузки,

т.к. ток нагрузки втекает в коллектор

через диоды последующей схемы. Нагрузочная

способность ДТЛ n=10,

время задержки

![]() нс.

Недостаток – много диодов, которые

занимают большую площадь на подложке.

нс.

Недостаток – много диодов, которые

занимают большую площадь на подложке.

ТТЛ (транзисторно-транзисторная логика). Схема ТТЛ со сложным инвертором показана на рис.22.

В

качестве входных диодов используются

эмиттерные переходы, а роль диода

смещения выполняет коллекторный переход

многоэмиттерного транзистора.

Многоэмиттерный транзистор занимает

гораздо меньшую площадь, чем соответствующее

количество диодов в схеме ДТЛ. Нагрузочная

способность n

10, время задержки

![]() нс.

нс.

Эмиттерно–связанная

логика (ЭСЛ).

Принципиальная схема показана на рис.21.

Транзистор Т3

совместно с любым из входных транзисторов

образуют переключатель тока. Схема

переключателя тока аналогична схеме

дифференциального усилителя, но на базу

Т3

подано постоянное напряжение смещения

![]() ,

при котором Т3

открыт и находится в активном режиме.

Если на базе Т1

(или Т2)

напряжение

,

при котором Т3

открыт и находится в активном режиме.

Если на базе Т1

(или Т2)

напряжение

![]() ,

ток, текущий через R1,

распределяется поровну между Т1

и Т3.

Если же напряжение на базе входного

транзистора немного (на 0,1...0,15 В) выше

или ниже

,

ток, текущий через R1,

распределяется поровну между Т1

и Т3.

Если же напряжение на базе входного

транзистора немного (на 0,1...0,15 В) выше

или ниже

![]() ,

весь ток переключается соответственно

в Т1

(Т2)

или в

,

весь ток переключается соответственно

в Т1

(Т2)

или в

Т3.

Эмиттерные повторители на транзисторах

Т4

и Т5

обеспечивают согласование входных и

выходных уровней последующего и

предыдущего логических элементов. Схемы

ЭСЛ обеспечивают малое время задержки

Т3.

Эмиттерные повторители на транзисторах

Т4

и Т5

обеспечивают согласование входных и

выходных уровней последующего и

предыдущего логических элементов. Схемы

ЭСЛ обеспечивают малое время задержки

![]() нс.

Как видно из схемы, на одном из выходов

выполняется логическая операция ИЛИ,

а на другом – ИЛИ–НЕ.

нс.

Как видно из схемы, на одном из выходов

выполняется логическая операция ИЛИ,

а на другом – ИЛИ–НЕ.

Логические элементы на мдп-транзисторах

Ключ на МДП–транзисторах можно выполнить с резистивной нагрузкой (как R3 в схеме 24), но технологически целесообразнее применять так называемую динамическую нагрузку - Т3 на схемах 25 и 26.

При последовательном соединении нескольких активных транзисторов получим логический элемент И–НЕ (рис. 26). Параллельное соединение активных транзисторов позволяет выполнить логическую операцию ИЛИ–НЕ (рис. 25). Наиболее часто используют логические схемы на МДП–транзисторах с индуцированным n-каналом.

В ИМС на КМДП-транзисторах (рис. 27 и 28) на каждый вход используется пара транзисторов с различной проводимостью канала, при этом затворы p-канального и n-канального транзисторов соединяются вместе. Особенность схем КМДП – весьма малая потребляемая мощность – является большим достоинством по сравнению с ранее рассмотренными логическими элементами.

Для выполнения операции И–НЕ используется схема рис. 28, в которой несколько нижних n-канальных транзисторов соединяются последовательно, а такое же число верхних р-канальных – параллельно.

Элемент ИЛИ–НЕ получается при параллельном соединении нижних и последовательном верхних транзисторов (рис. 27). В этом можно убедиться, рассматривая все возможные комбинации входных логических сигналов.

Описание к КПК «Триггеры»