Arhitektura_EVM

.docx

1.1943-первая ЭВМ коллектива фон Неймана.

Всего комплекс включал 17468 ламп, 7200 кремниевых диодов, 1500 реле, 70000 резисторов и 10000 конденсаторов. Потребляемая мощность — 140 кВт. Вычислительная мощность — 300 операций умножения или 5000 операций сложения в секунду. Вес — 30 тонн. Вычисления производились в десятичной системе.

2. Идея делить машины на поколения вызвана к жизни тем, что за время короткой истории своего развития компьютерная техника проделала большую эволюцию, как в смысле элементной базы (лампы, транзисторы, микросхемы и др.), так и в смысле изменения её структуры, появления новых возможностей, расширения областей применения и характера использования. Этот прогресс показан в данной таблице:

|

П О К О Л Е Н И Я Э В М |

ХАРАКТЕРИСТИКИ |

|||

|

|

1 |

2 |

3 |

4 |

|

Годы применения |

1946-1958 |

1958-1964 |

1964-1972 |

1972 - настоящее время |

|

Основной элемент |

Эл.лампа |

Транзистор |

ИС |

БИС |

|

Быстродействие (операций в секунду) |

2—3 тыс |

20—30 тыс |

|

5,5 млн |

|

Носитель информации |

Перфокарта, Перфолента |

Магнитная Лента |

Диск |

Гибкий и лазерный диск |

|

Размеры ЭВМ |

Большие |

Значительно меньше |

Мини-ЭВМ |

микроЭВМ |

3.Первая в СССР ЭВМ (МЭСМ) создана в 1951году под руководством Лебедева.Она имела универсальное арифметическое устройство. Выполняла 50 арифметических или логических операций в секунду. Ее потребляемая мощность составляла 25кВТ.

4.Там все своими словами.

5.характеристики ЭВМ (быстродействие и производительность, показатели надежности, достоверности, точности, емкость оперативной и внешней памяти, габаритные размеры, стоимость технических и программных средств, особенности эксплуатации т.д.

6. Системная магистраль - это среда передачи сигналов управления, адресов, данных, к которой параллельно и одновременно может подключаться несколько компонентов вычислительной системы. Физически системная магистраль представляет собой параллельные проводники на материнской плате, которые называются линиями. Но это еще и алгоритмы, по которым передаются сигналы, правила интерпретации сигналов, дисциплины обслуживания запросов, специальные микросхемы, обеспечивающие эту работу.

7. Способы представления информации в ЭВМ, кодирование и преобразование кодов в значительной степени зависят от принципа действия устройств, в которых эта информация формируется, накапливается, обрабатывается и отображается.

Для кодирования символьной или текстовой информации применяются различные системы: при вводе информации с клавиатуры кодирование происходит при нажатии клавиши, на которой изображен требуемый символ, при этом в клавиатуре вырабатывается так называемый scan-код, представляющий собой двоичное число, равное порядковому номеру клавиши.

8.

9. Необходимость в указании положения запятой отпадает, если место запятой в разрядной сетки машины заранее фиксировано раз и навсегда. Такая форма представления чисел называется представлением с фиксированной запятой (точкой).

10.Плавающая запятая — форма представления действительных чисел, в которой число хранится в форме мантиссы и показателя степени. Мантисса используется для записи цифр числа, а степень – для указания положения запятой..При этом число с плавающей запятой имеет фиксированную относительную точность и изменяющуюся абсолютную.

11. Трехадресная система команд.

Двухадресная система команд

Одноадресная система команд

12.1. Принцип двоичного кодирования.

Для представления данных и команд используется двоичная система счисления(цифры 0 и 1)

2.Принцип однородности памяти.

Как программы (команды), так и относящиеся к программам данные хранятся в одной и той же памяти (и кодируются в одной и той же системе счисления — чаще всего двоичной). Над командами можно выполнять такие же действия, как и над данными.

3.Принцип адресуемости памяти.

Структурно основная память состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка; память внутренняя.

4.Принцип последовательного программного управления.

Все команды располагаются в памяти и выполняются последовательно, одна после завершения другой, в последовательности, определяемой программой.

5.Принцип жесткости архитектуры.

Неизменяемость в процессе работы топологии, архитектур

13.Формат одноадресной команды

14. CISC (complex instruction set computer) — концепция проектирования процессоров, которая характеризуется следующим набором свойств:

нефиксированное значение длины команды;

арифметические действия кодируются в одной команде;

небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Недостатки CISC архитектуры:

высокая стоимость аппаратной части;

сложности с распараллеливанием вычислений.

Методика построения системы комманд CISC комплементарна (противоположна, имеется в виду) другой методике - RISC. Различие этих концепций состоит в методах программирования, а не в реальной архитектуре процессора. Практически все современные процессоры эмулируют наборы команд как RISC так и CISC типа.

15. RISC— компьютер с упрощённым набором команд — архитектура процессора, в которой быстродействие увеличивается за счёт упрощения команд, чтобы их декодирование было проще, а время выполнения — короче. Первые RISC-процессоры даже не имели команд умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание команд между несколькими исполнительными блоками).Также эти процессоры не патентировались из-за чего получили большойскачак в развитии.

16.MISC- Процессор работующий с минимальным набором длинных команд.Увелечение разрядности процессоров привело к идее укладки нескольких команд в одно слово размером 128 бит. Оперируя одним словом процессор получил возможность обрабатывать сразу несколько команд.

17.VLIW-процессор работующий с системой команд сверхбольшой разрядности .Идея технологии VLIW закл. в том что создается специальный компилятор планирования который перед выполнением прикладной программы проводит ее анализ и по множеству ветвей последовательности операций определяет группу команд которые могут выполняться параллельно. Каждая такая группа образует одну сверхдлинную команду.

18. В описании сложных систем используют несколько форм описания (языков) функций и структуры — иерархию функций и структуры. Иерархический подход к описанию сложных систем предполагает, что на высшем уровне иерархии система рассматривается как один элемент, имеющий входы и выходы для связи с внешней средой. В этом случае функция не может быть задана подробно и представляется как отображение состояний входов на со- стояние выходов системы.

19.

20. Иерархия запоминающих устройств

21. 1. Информационная емкость (в дальнейшем просто емкость).Емкость памяти может быть равна 1 биту (одна триггерная схема), однако может достигать значения и 1012 бит. В вычислительных машинах емкость ЗУ часто выражается в количестве байтов

2. Время выборки.

Время выборки — это временной интервал, определяемый от момента выдачи запроса передачи из памяти до момента появления требуемой информации на выходе ЗУ.

3. Цикл обращения (цикл памяти).

Цикл обращения — это минимально допустимый интервал времени между двумя последовательными обращениями к ЗУ.

4. Стоимость 1 бита.

Стоимость 1 бита определяется отношением стоимости ЗУ к ее информационной емкости. Она существенно зависит от типа памяти и ее емкости.

5. Возможность изменения информации.

Данное качество характеризует тип памяти; в триггерной схеме изменение информации осуществляется довольно просто, однако информацию, хранимую в постоянном ЗУ, изменить нельзя.

6. Способ выборки информации.

По способу выборки информации различают устройства памяти: с произвольной (непосредственной) и последовательной выборкой. В памяти с произвольной выборкой время выборки, а следовательно, и цикл обращения не зависят от адреса

(места расположения) информации.

7. Сохранение информации при отключении напряжения питания.

23.

1.внутрение ЗУ. Предназначены для хранения данных непосредственно необходимых во время выполнения программы.

2.внешние ЗУ Предназначены для хранения больших объемов данных на сменных(гибкие, компакт – диски и др.) и фиксированных носителях (жесткие диски).

24. СВЕРХОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

быстродействующее запоминающее устройство, предназнач. для объединения ф-ций неск. регистров процессора, а также для временного хранения промежуточных результатов, часто используемых данных, констант и коротких подпрограмм. С. з. у. используется при существ. различии в скоростях работы процессора и оперативного запоминающего устройства, обеспечивает немедленное представление в распоряжение процессора тех блоков информации, к-рые подлежат обработке в данный момент.

Оперативная память, оперативное запоминающее устройство (= ОЗУ), (англ. RAM = random access memory) − быстродействующее запоминающее устройство произвольного доступа, предназначенное для временного хранения данных в компьютере. Данные в ОЗУ сохраняются до выключения питания.

По техническому исполнению оперативная память в современных компьютерах бывает следующих видов:

статическое ОЗУ — на основе триггерных ячеек;

динамическое ОЗУ — на основе конденсаторов.

25. Внешние запоминающие устройства. Эти устройства обеспечивают хранение больших массивов информации. Они относительно недороги, но обладают значительно меньшим быстродействием, чем устройства внутренней памяти ЭВМ. Наиболее широкое распространение получили ВЗУ на магнитных носителях (лентах и дисках).

БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, предназначено для промежуточного хранения информации при обмене ею между устройствами ЭВМ, работающими с разными скоростями.

26. Постоянное запоминающее устройство (ПЗУ) — энергонезависимая память, используется для хранения массива неизменяемых данных.

С параллельным доступом (parallel mode или random access): такое ПЗУ может быть доступно в системе в адресном пространстве ОЗУ. Например, К573РФ5;

С последовательным доступом: такие ПЗУ часто используются для однократной загрузки констант или прошивки в процессор или ПЛИС, используются для хранения настроек каналов телевизора, и др

27. SISD (Single Instruction Stream/Single Data Stream) — одиночный поток команд и одиночный поток данных.

MISD (Multiple Instruction Stream/Single Data Stream) — множественный поток команд и одиночный поток данных.

SIMD (Single Instruction Stream/Multiple Data Stream) — одиночный поток команд и множественный поток данных

MIMD (Multiple Instruction Stream/Multiple Data Stream) — множественный поток команд и множественный поток данных.

28.

29. Микросхемы ОЗУ на биполярных транзисторах. Биполярные триггерные микросхемы обладают значительным быстродействием , потреблют больше энергии чем микросчемы типа МДП

30. Схемы, в которых в качестве запоминающей ячейки используется параллельный регистр называются статическим оперативным запоминающим устройством - статическим ОЗУ

В микросхемах ОЗУ присутствуют две операции: операция записи и операция чтения. Для записи и чтения информации можно использовать различные шины данных (как это делается в сигнальных процессорах), но чаще используется одна и та же шина данных. Это позволяет экономить внешние выводы микросхем, подключаемых к этой шине и легко осуществлять коммутацию сигналов между различными устройствами.

31.

Горизонтальные шины матрицы – адресные

Вертикальные-разрядные, с них снимаются восьмиразрядные двоичные числа, записанные в ПЗУ. Если к примеру с выхода дешифратора возбуждается адреснаяшина ША2 то логичное происходит с ней через диоды на резр шине ШР2 ШР6 ШР7 ШР8 сообщая число 11100010.

32.

+ И ип.

R1 R2

И выход

33. Масочные ПЗУ изображаются на принципиальных схемах как показано на рисунке 5. Адреса ячеек памяти в этой микросхеме подаются на выводы A0 ... A9. Микросхема выбирается сигналом CS. При помощи этого сигнала можно наращивать объем ПЗУ (пример использования сигнала CS приведён при обсуждении ОЗУ). Чтение микросхемы производится сигналом RD.

34.

Программируемые ПЗУ оказались очень

удобны при мелкосерийном и среднесерийном

производстве. Однако при разработке

радиоэлектронных устройств часто

приходится менять записываемую в ПЗУ

программу. ППЗУ при этом невозможно

использовать повторно, поэтому раз

записанное ПЗУ при ошибочной или

промежуточной программе приходится

выкидывать, что естественно повышает

стоимость разработки аппаратуры. Для

устранения этого недостатка был

разработан еще один вид ПЗУ, который

мог бы стираться и программироваться

заново.

35.Микропроцессор-функционально законченное устройство обработки ин-фы, управляемое хранимой в памяти программой.

В состав МП входят: АЛУ, Устройство управ, Блок Внутренних Регистров.

36.

37.Регистр общего назначения – число которое може изменяться от 4 до 160 в значительной мере определяет вычислительные возможности МП. Их основная функция – хранение операндов.

-

Регистр-аккомулятор-обычно называется просто аккомулятор. Предназначен для временного хранения операнда или промежуточного результата арифметических или логических операций, производимых АЛУ.

-

Буферный регистр адреса- служит для приема и хранения адресной части исполняемой работы.

-

Буферный регистр данных-используется для временного хранения выбранного из памяти слова перед выдачей его во внешнюю шину данных. Его разрядность определяется количеством байтов информационного слова.

-

Регистр команд-принимает и хранит код очередной команды, адрес которой находится в счетчике команд.По сигналу ХХ в него передается из регистра хранимая там информация.

-

Регистры стека делятся на стек и указатель стека. Название «стек» происходит от английского слова stack, что в дословном переводе означает штабель (дров), кипа (бумаг) и др. В МП стек представляет собой набор регистров, хранящих адреса команд возврата при обращении к подпрограммам или состояния внутренних регистров при обработке прерываний. Этот набор организован таким образом, что слово адреса или данных выбирается по принципу: «вошедший последним – выходит первым». При записи в стек очередного слова все находящиеся в нем слова сдвигаются на один регистр вниз. После выборки слова из стека оставшиеся слова сдвигаются на один регистр вверх. Стек может быть выполнен не только на внутренних регистрах МП, составляя его часть, но и находиться в ОЗУ, занимая там выделенную для него зону. В последнем случае стек получается более глубоким, емким, однако для обращения к нему необходим специальный регистр - указатель стека.

-

Указатель стека хранит адреса последней занятой ячейки стека, которую называют вершиной. Содержащееся в указателе число указывает, где находится вершина стека. Когда в стек записывается очередное слово, то число в указателе стека соответственно увеличивается. Извлечение слова из стека сопровождается, наоборот, уменьшением числа, заполняющего указатель стека. Кроме такой процедуры, предусматривается возможность считывания без разрушения содержимого любой ячейки стека при неизменном числе, хранимом в указателе стека.

-

Регистр признаков представляет собой набор триггеров – флажков. В зависимости от результатов операций, выполняемых АЛУ, каждый триггер устанавливается в состояние 0 или 1. Флажковые биты, определяющие содержимое регистра, индицируют условные признаки: нулевого результата, знака результата, переполнения и т. п. Эта информация, характеризующая состояние процессора, важна для выбора дальнейшего пути вычислений.

38.Структура МП i8086

39. Арифме́тико-логи́ческое устро́йство (АЛУ)— блок процессора, который под управлением устройства управления (УУ) служит для выполнения арифметических и логических преобразований над данными, представляемыми в виде машинных слов, называемыми операндами.

Арифметическо-логическое устройство в зависимости от выполнения функций можно разделить на две части: микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд); операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд)

40. По способу представления чисел различают АЛУ:

для чисел с фиксированной точкой;

для чисел с плавающей точкой;

для десятичных чисел.

41. Центральное устройство управления (ЦУУ) включает дешифратор команд, блок управления и блок прерываний.

Дешифратор команд дешифрирует (декодирует) команды, которые поступают из блока предварительной выборки.

Блок управления (БУ) формирует последовательности управляющих сигналов, которые поступают на все блоки процессора, обеспечивающие выполнение текущей команды и переход к выполнению следующей.

Блок прерывания обеспечивает реакцию ЭВМ на запросы прерываний от различных источников (устройств) внутри и вне ЦП.

42. Кэш-память - очень быстрое запоминающее устройство небольшого объема, которое используется при обмене данными между процессором и оперативной памятью для компенсации разницы в скорости обработки информации процессором и несколько менее быстродействующей оперативной памятью.

Кэш-памятью управляет специальный контроллер, который, анализируя выполняемую программу, пытается предвидеть, какие данные и команды вероятнее всего понадобятся в ближайшее время процессору, и подкачивает их в кэш-память.

43.Параметры и функциональные характеристики КЭШ-памяти:

1)Объем КэШа

2)Метод отображения:

-прямой

-ассоцативный

-аккумулированой-ассоциативной

3)Алгоритм Замены:

-LRU-заменяется строка к которой дольше всего не обращался процессор

-LFU-заменяется реже всего использовавшеяся строка

-FIFO-заменяется строка к которой дольше всего не обращался процессор

44. Интерфейс – совокупность стандартизованных аппаратных и программных средств, обеспечивающих обмен информации между устройствами. В основе построения интерфейсов лежит унификация и стандартизация (использование единых способов кодирования данных, форматов данных, использование единых разъемов и т.п.). Наличие интерфейсов позволяет унифицировать передачу данных между устройствами независимо от их особенностей.

Классификация:

Способ соеденения компонентов (магистральный, радиальный, комбинированный итд)

Способ передачи информациипараллельный последовательный, параллельно-последовательный)

Принцип обмена информацией(синхронный,асинхронный).

Режим передачи инфы(односторонняя двусторонняя, поочередная).

Классы интерфейса:

1)Системные интерфейсы ЭВМ

2)интерфейсы перефирийного оборудования

3)программно-управляемых модульных систем и приборов

4)Интерфейсы сетей передачи данных

45.

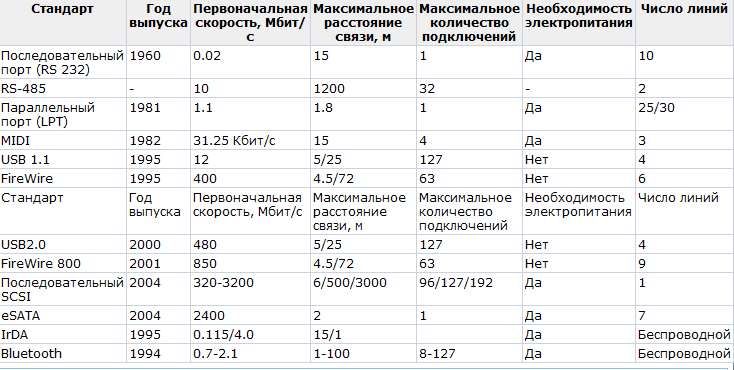

46. Принтеры, модемы и другое периферийное оборудование подключается к компьютеру через стандартизированные интерфейсы, иногда называемые портами. В зависимости от способа передачи информации (параллельного или последовательного) между сопрягаемыми устройствами различают параллельные и последовательные интерфейсы.

47. Ячейки ОЗУ и РОН содержат по шесть десятичных разрядов. Данные в модели представляются в формате целые десятичные числа, изменяющиеся в диапазоне минус 99 999…+99 999, содержащие знак и 5 десятичных цифр. Под знак отводится старшая десятичная цифра, причём «плюс» кодируется «0», а «минус» - любой другой цифрой (привычно – «1»).

Если результат арифметической операции выходит за пределы указанного диапазона, то формируется флаг переполнения OV = 1. Результатом операции деления является целая часть частного. Деление на ноль вызывает переполнение.

48. Система команд учебной ЭВМ содержит около 50 команд, большинство которых является безадресными или одноадресными. Только две команды являются двухадресными: MOV Ri, Rj - команда пересылки из регистра в регистр и JRNZ Ri,ADR - организация цикла. Все форматы команд приведены на рисунке

Два старших разряда (0 и 1) всех форматов отводится под код операции, разряд 2 определяет тип адресации, три младших разряда (3, 4 и 5) могут использоваться для задания адреса операнда в памяти, непосредственного операнда (в диапазоне 0..999), адреса передачи управления или двух адресов РОН. В случаях, когда требуется использовать непосредственный операнд в диапазоне минус 99999 .. +99999, используется формат 4, занимающий две ячейки памяти. Символ «Х» означает безразличное значение разряда в данном формате.

При описании форматов команд используются следующие сокращения:

COP – код операции;

TA – тип адресации;

ADR – адрес операнда (прямой, косвенный или относительный – в зависимости от типа адресации) или трёхразрядный непосредственный операнд;

R, R1, R2 – номер (адрес) регистра общего назначения (R0 – R9);

ADC – адрес перехода в командах передачи управления;

X – значение разряда безразлично.

49.

|

КОД ТА |

ТИП АДРЕСАЦИИ |

ИСПОЛНИТЕЛЬНЫЕ АДРЕСА |

|

0 |

Прямая(регистровая) |

ADR(R) |

|

1 |

Непосредственная |

- |

|

2 |

Косвенная |

ОЗУ(ADR) [3:5] |

|

3 |

Относительная |

ADR+RB |

|

4 |

Косвенно-регистровая |

POH(R) [3:5] |

|

5 |

Индексная с постинкрементном |

POH(R)[3:5] R=R+1 |

|

6 |

Индексная с прединкриментом |

R=R-L, POH(R) [3:5] |

50.

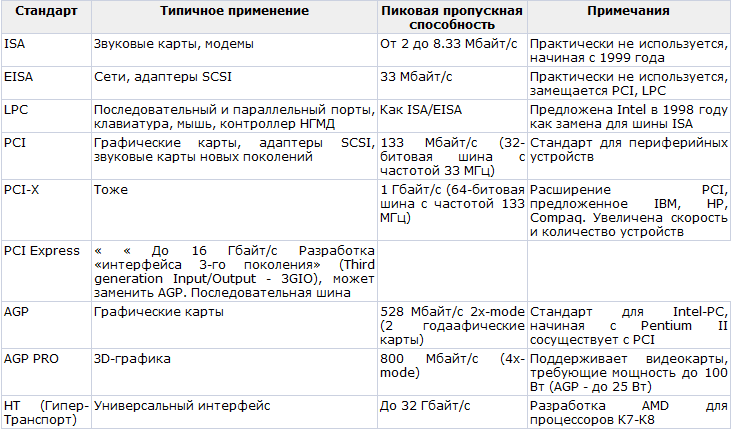

Cеверный мост обеспечивает обмен информацией между процессором и оперативной памятью по системной шине. В процессоре используется внутреннее умножение частоты, поэтому частота процессора в несколько раз больше, чем частота системной шины. В современных компьютерах частота процессора может превышать частоту системной шины в 10 раз (например, частота процессора 1 ГГц, а частота шины - 100 МГц). К северному мосту подключается шина PCI (Peripherial Component Interconnect bus - шина взаимодействия периферийных устройств), которая обеспечивает обмен информацией с контроллерами периферийных устройств. Частота контроллеров меньше частоты системной шины, например, если частота системной шины составляет 100 МГц, то частота шины PCI обычно в три раза меньше - 33 МГц. Контроллеры периферийных устройств (звуковая плата, сетевая плата, SCSI-контроллер, внутренний модем) устанавливаются в слоты расширения системной платы.

По мере увеличения разрешающей способности монитора и глубины цвета требования к быстродействию шины, связывающей видеоплату с процессором и оперативной памятью, возрастают. В настоящее время для подключения видеоплаты обычно используется специальная шина AGP (Accelerated Graphic Port - ускоренный графический порт), соединенная с северным мостом и имеющая частоту, в несколько раз большую, чем шина PCI.