- •Организация памяти вс

- •Иерархическая структура памяти

- •Емкость (объем)

- •Организация внутренней памяти вс

- •Архитектура оперативной памяти

- •Адресная память

- •Ассоциативные запоминающие устройства

- •Стековые запоминающие устройства

- •Увеличение объема внутренней памяти

- •Логическая организация памяти

- •Вычисление физического адреса памяти

- •Сегментная структура памяти

- •Согласование оперативной памяти с процессором по быстродействию

- •Конвейеризация (опережающая выборка команд из памяти).

- •Организация банков (модулей) памяти.

- •Использование буферной (сверхоперативной) памяти.

- •Структура кэш-памяти

- •Технологии флэш-памяти

- •Где нужна память…

- •И будет флэш…

Сегментная структура памяти

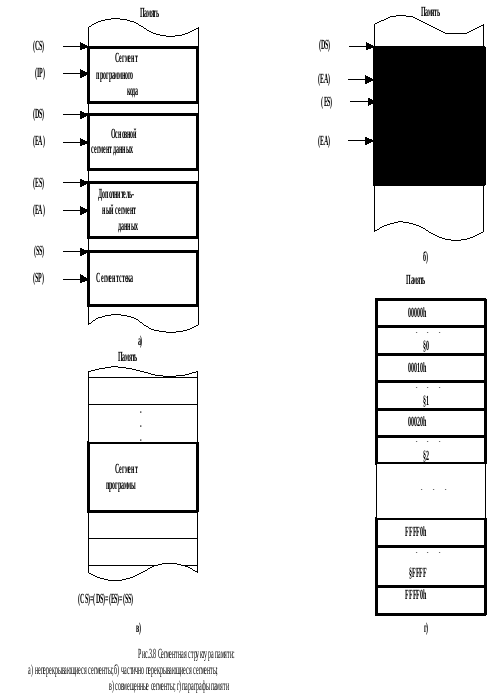

В соответствии с принципом вычисления физического адреса физические сегменты могут располагаться в памяти различным образом. Они могут быть неперекрывающимися, а также частично или полностью накладываться друг на друга. Различные варианты сегментных структур памяти приведены на рис.3.8.

Общее количество неперекрывающихся сегментов равно 16. Начало сегмента определяется содержимым соответствующего сегментного регистра. Поэтому всего в памяти может располагаться 216 сегментов.

При этом начальные адреса сегментов всегда кратны 16, так как заканчиваются 16-ричным нулем. Отсюда следует, что соседние сегменты отстоят друг от друга на 16 байтов.

Область памяти объемом в 16 байтов с начальным адресом, кратным 16, называется параграфом. Параграф характеризуется номером, значение которого равно содержимому сегментного регистра.

В частном случае при (CS)=(DS)=(ES)=(SS)=0 все сегменты совмещены в один сегмент программы объемом 64 кбайт. При этом организация памяти в МПС на базе i8086/8088 идентична организации памяти в МПС на базе МП i8080.

При неизменном содержимом сегментных регистров обеспечивается доcтуп не более чем к 256 кбайт памяти. Для доступа к полному адресному пространству необходимо изменять содержимое сегментных регистров.

Основным достоинством сегментной организации памяти является возможность свободного перемещения программы по всему объему адресного пространства, что необходимо для эффективного использования памяти в сложных системах. Для перемещения программы достаточно изменить лишь содержимое сегментных регистров CS, DS, ES, SS. Чтобы быть позиционно-независимой, программа не должна модифицировать своих сегментных регистров.

Недостатком сегментной организации памяти является сложность манипуляции физическими адресами при необходимости их программной обработки.

Конкретный физический адрес может быть получен из множества логических адресов, то есть из множества комбинаций segment:offset.

-

Согласование оперативной памяти с процессором по быстродействию

Быстродействие процессоров постоянно растет за счет совершенствования технологии их производства и разработки новых схемотехнических решений, в то время как быстродействие оперативной памяти растет, но со значительно меньшими темпами.

Это объясняется тем, что в первую очередь обеспечивается увеличение емкости оперативной памяти, чем быстродействие. При этом возникает задача согласования временных характеристик процессоров и памяти.

Для выполнения указанной задачи используется ряд методов.

-

Конвейеризация (опережающая выборка команд из памяти).

Позволяет наряду с выполнением текущей команды производить с помощью счетчика команд адресацию следующей команды, ее выборку из памяти и помещение в очередь (конвейер) подлежащих исполнению команд.

-

Организация банков (модулей) памяти.

В этом случае память разделяется на ряд независимых банков (разрядность одного банка – 1 байт, общее число банков зависит от разрядности шины данных), которые позволяют считывать информацию параллельно (одновременно). Длинные команды могут располагаться в нескольких банках и для их выборки активируются все банки. Если команда хранится в одной ячейке памяти одного банка, то происходит выборка нескольких команд из всех банков.