- •Курс лекций

- •Наноэлектронные приборы

- •Кремниевые мдп транзисторы

- •High-k технология metal gate.

- •Кни мдп транзисторы.

- •Транзисторы с двойным затвором.

- •Полевые транзисторы с затвором Шоттки.

- •Гетеротранзисторы

- •Немт-транзисторы.

- •Modfet-транзисторы.

- •Резонансно-туннельные транзисторы.

- •Гетероструктурный транзистор на квантовых точках.

- •Транзисторы на основе одноэлектронного туннелирования.

- •Кремниевый одноэлектронный транзистор с двумя затворами.

- •Квантово-точечный кни транзистор.

- •Одноэлектронные транзисторы на основе гетероструктур.

- •Транзисторы на основе туннельных переходов мдм

- •Приборы на основе цепочек коллоидных частиц золота.

- •Молекулярный одноэлектронный транзистор.

- •Одноэлектронный механический транзистор.

- •Баллистические транзисторы

- •Интерференционные транзисторы

- •Полевые транзисторы на отраженных электронах.

- •Нанотранзисторы на основе углеродных нанотрубок

- •Транзисторы на горячих электронах.

- •Спин чувствительные приборы.

- •Энергонезависимая память на гигантском магнитосопротивлении.

- •Спин вентильный транзистор.

- •Оптоэлектронные приборы

- •Лазеры с квантовыми ямами и точками.

- •Оптические модуляторы.

High-k технология metal gate.

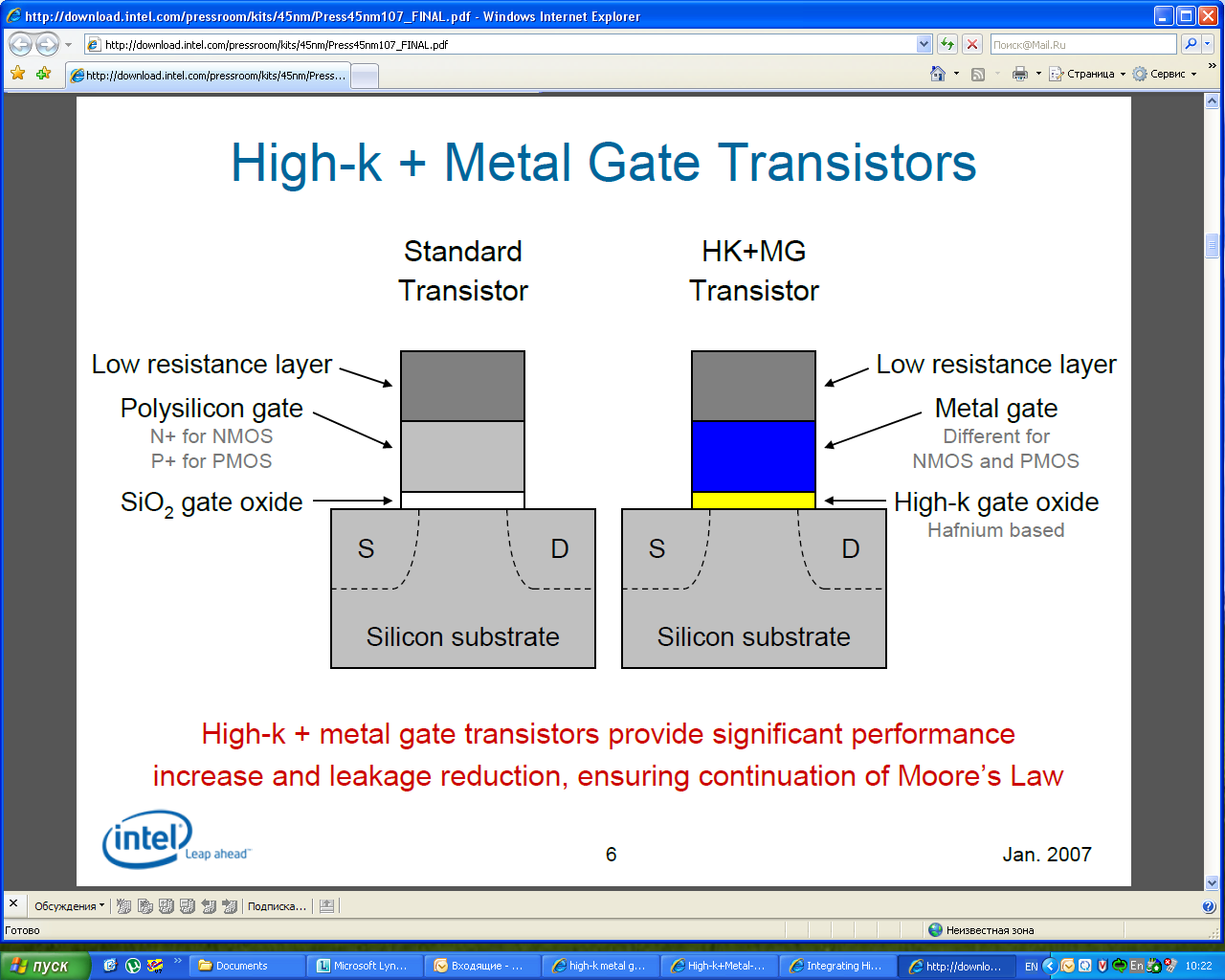

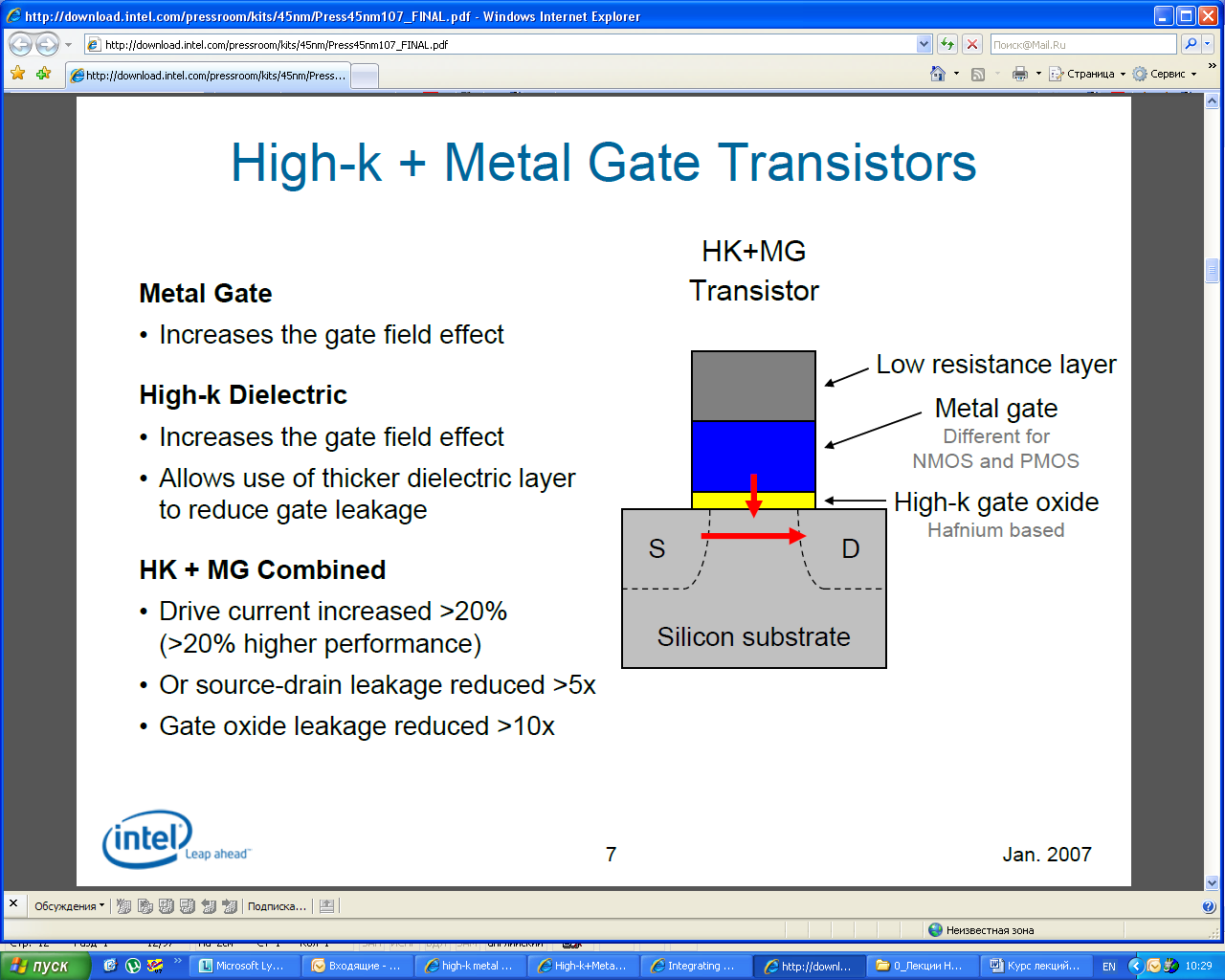

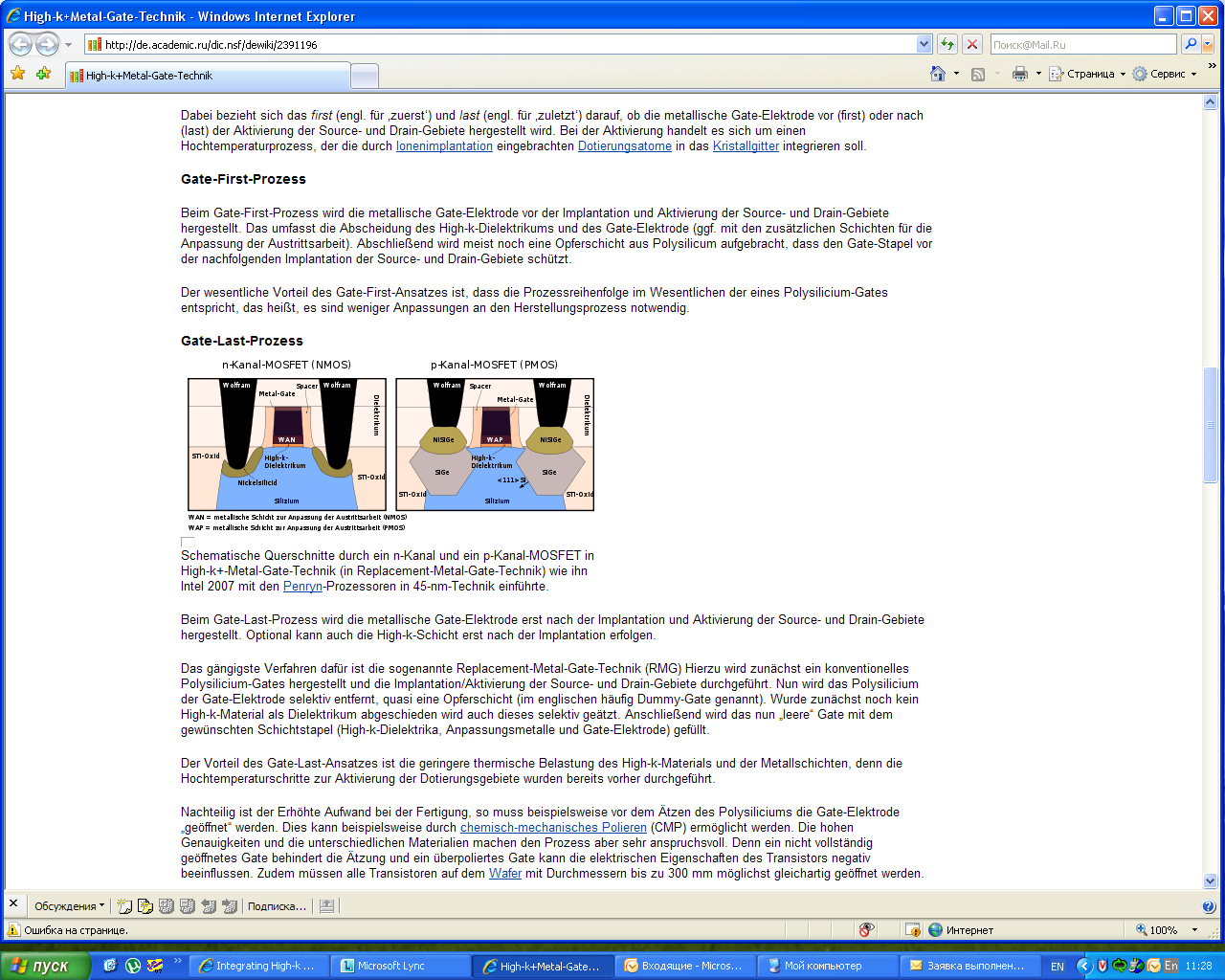

Так для транзисторов 45 нм разрешения и ниже (32 нм, 28 нм) предложено взамен SiO2 использовать в качестве подзатворного диэлектрика диэлектрик по High-K технологии. Это диэлектрики совместимые с кремнием по механическим напряжениям и поверхностным состояниям, допускающие нанесение на поверхность подложек, выдерживающие последующие термические обработки и позволяющие реализовать современную литографическую гравировку высокого разрешения. При этом пленки моноатомных слоев должны быть термически стабильными и сохранять целостность, иметь минимальные токи утечки и не ухудшать подвижность носителей заряда в прилегающем полупроводнике. К таким диэлектрикам сегодня можно отнести двуокись гафния и двуокись циркония (HfO2, ZrO2). Их можно испарять методами магнетронного и электронно- лучевого распыления.

Относительная диэлектрическая постоянная у HfO2 составляет 25, а у ZrO2 - 20, тогда как у SiO2– 3,8. Более высокая диэлектрическая проницаемость этих диэлектриков позволяет обеспечивать приемлемую крутизну МОП транзисторов при более толстых подзатворных диэлектриках. При этом снижаются паразитные туннельные токи и токи утечки между затвором и другими областями транзистора. Для улучшения химического согласования с этими окислами в качестве материала затвора предлагают использовать HfSi и ZrSi, соответственно (силициды гафния и циркония).

Например, для транзистора с затвором длиной 30 нм и с подзатворным HfO2 толщиной 3 нм получена крутизна транзистора такая же, как и при использовании SiO2 толщиной 1,2 нм. При этом токи утечки затвора снизились почти на два порядка (более чем в 10 раз).

Допматериал. Формула порогового напряжения.

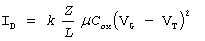

Вольтамперная характеристика идеального МДП транзистора, полученная в приближении плавного канала при учете только дрейфовой составляющей тока и ряде других предположений может быть записана в виде:

![]()

где Z - ширина канала, L - длина канала, - подвижность носителей заряда (м2/В*с), Cox - емкость подзатворного диэлектрика(Ф/м2), VG - напряжение на затворе, VD - напряжение на стоке, VT - пороговое напряжение.

Пороговое напряжение VT соответствует началу сильной инверсии (s=2o) т.е. формированию инверсионного канала и открытию транзистора. Наличие захваченного заряда в диэлектрике Qox и на поверхностных состояниях Qss, а также контактной разности потенциалов ms, приводит к сдвигу порогового напряжения:

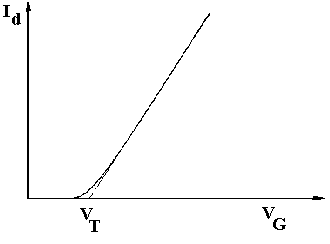

В линейной области, когда справедлива формула (1) передаточная ВАХ ID(VG) также линейна и величина VT может быть найдена экстраполяцией графика к оси абсцисс (рис.1).

Рис 1. Передаточная ВАХ в линейной области

В области насыщения (в условиях отсечки канала) передаточная ВАХ МДП транзистора ID(VG) имеет квадратичную форму:

(3)

(3)

↑↑↑ Конец. Формула порогового напряжения

Кни мдп транзисторы.

Эти транзисторы имеют основание, полностью или частично обедненное носителями. Вследствие обеднения подложки зарядами электрическое поле в инверсионном слое прибора существенно меньше, чем в обычных приборах с сильнолегированной областью канала. На практике будем рассчитывать и анализировать распределение электрического поля под затвором МОП структуры и соответствующий изгиб энергетических зон.

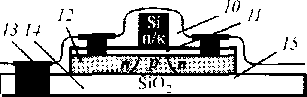

Интересные результаты получены в Институте физики полупроводников СО РАН. По технологии DeleCut были изготовлены транзисторные КНИ-структуры, представленные на рис. 3.3.

Контакт к затвору располагается сбоку от канала, как и контакт к базовой области. Для того чтобы область стока и

истока не смыкались в результате отжигов, необходимо создать сильное легирование базы и достаточно слабое

легирование истока и стока.

На рис. 3.4 даны сток-затворные характеристики п- и p-канальных транзисторов с частичным обеднением для толщин слоя кремния 500 нм (1) и 20 нм (2). Пороговое напряжение лежит в пределах 0,5 В - 0,7 В. Токи насыщения транзисторов составляют для n-канального транзистора 220 мкА/мкм, для р-канального — 90 мкА/мкм, токи утечки не превышают 10-9 А/мкм.

К недостаткам этого типа транзисторов отнесем, прежде всего, высокий уровень легирования базы (~1018 см-3), что резко снижает подвижность носителей заряда. Кроме того, короткий канал трудно управляется напряжением на затворе.

Рис. 3.3. Структура КНИ МОП-транзистора:

1 — поликремневый затвор; 2 - алюминиевый контакт; 3, 12 — рекристаллизованный кремниевый островок; 4 — база; 5 — контактное окно; 6 — металлизация; 7 — исток/база; 8 — сток; 9, 13 — контакт к подложке; 10 — пиролитический оксид; 11 — подзатворный оксид; 14 - подложка; 15 - захороненный оксид.

\

Рис. 3.4. Сток-затворные характеристики n- и p- ка- пальпых КНИ-транзисторов с толщиной слоя кремния 1-500 нм и 2 – 20 нм: Ic— ток стока; Uз — напряжение на затворе.

Допматериал. Сравнение технологий/

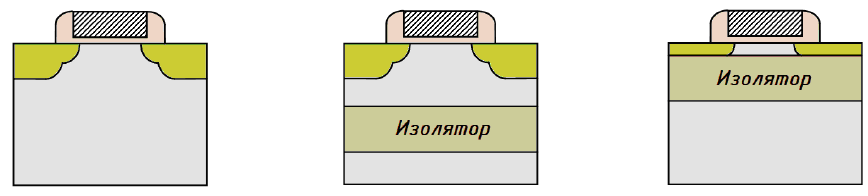

Основной альтернативой транзисторам на монолитной подложке является КНИ

(кремний на изоляторе (SOI)) КМОП технологии. Существует множество вариантов

реализации КНИ, технология давно и хорошо отлажена. Выделяют два типа МОП

транзисторов: выполненным по технологиям частично или полностью обеднённого КНИ

(Partially depleted SOI / Fully depleted SOI) (рис. 5).

Преимущества КНИ КМОП над обычной КМОП технологий в более компактной

топологии, следовательно, меньших ёмкостях сток-исток, однако в случае с частично

обеднённым КНИ появляются эффекты «плавающего тела».

Транзистор на цельной подложке имеет утечку тока из канала, когда в нём полем

затвора формируется инверсионный слой. Подложка (даже если она заземлена)

вытягивает часть носителей заряда в обеднённый слой. Уменьшить утечки можно

технологией КНИ, в данном случае — частично обеднённой. Тут изолятор отсекает

подложку, но остаточный слой под каналом («плавающее тело») всё ещё приводит к

утечкам. Эта технология широко используется из-за относительной дешевизны. Лучшее

— полностью обеднённый КНИ. Тут исток, сток и область канала истончаются так, что

плавающему телу не остаётся места. Проблема утечки решается, но с 10-процентным

увеличением цены чипа, поэтому её не используют широко.

Транзисторы с двумя и более затворами. Применение нескольких затворов позволяет

уменьшить короткоканальные эффекты, улучшает подпороговую крутизну, но не решает

проблем с рассеиваемой динамической мощностью и повторяемостью ТП. По результатам

компьютерного моделирования с ростом количества затворов улучшается DIBL-эффект и

эффект короткого канала (спад порогового напряжения), особенно, для транзисторов с

коротким каналом. В четверном затворе («затвор со всех сторон», Gate all around (GAA))

появляются некоторые побочные эффекты, такие как резкое увеличение числа зарядов в

углах канала, что приводит к усложнению контроля работы транзистора. Производство

такого транзистора также сопряжено с рядом технологических трудностей.

При использовании узкого канала разница в

характеристиках между двойным и тройным затворами

невелика. В тройном затворе также появляются

паразитные «угловые эффекты», поэтому в этой работе

будет разработан транзистор с затвором-«плавником»

(FinFET), относящийся к классу транзисторов с

двойным затвором (рис. 6). За счёт вертикального

размещения каналов их может быть несколько для

увеличения площади между затвором и каналами.

Конец. Допматериал. Сравнение технологий.

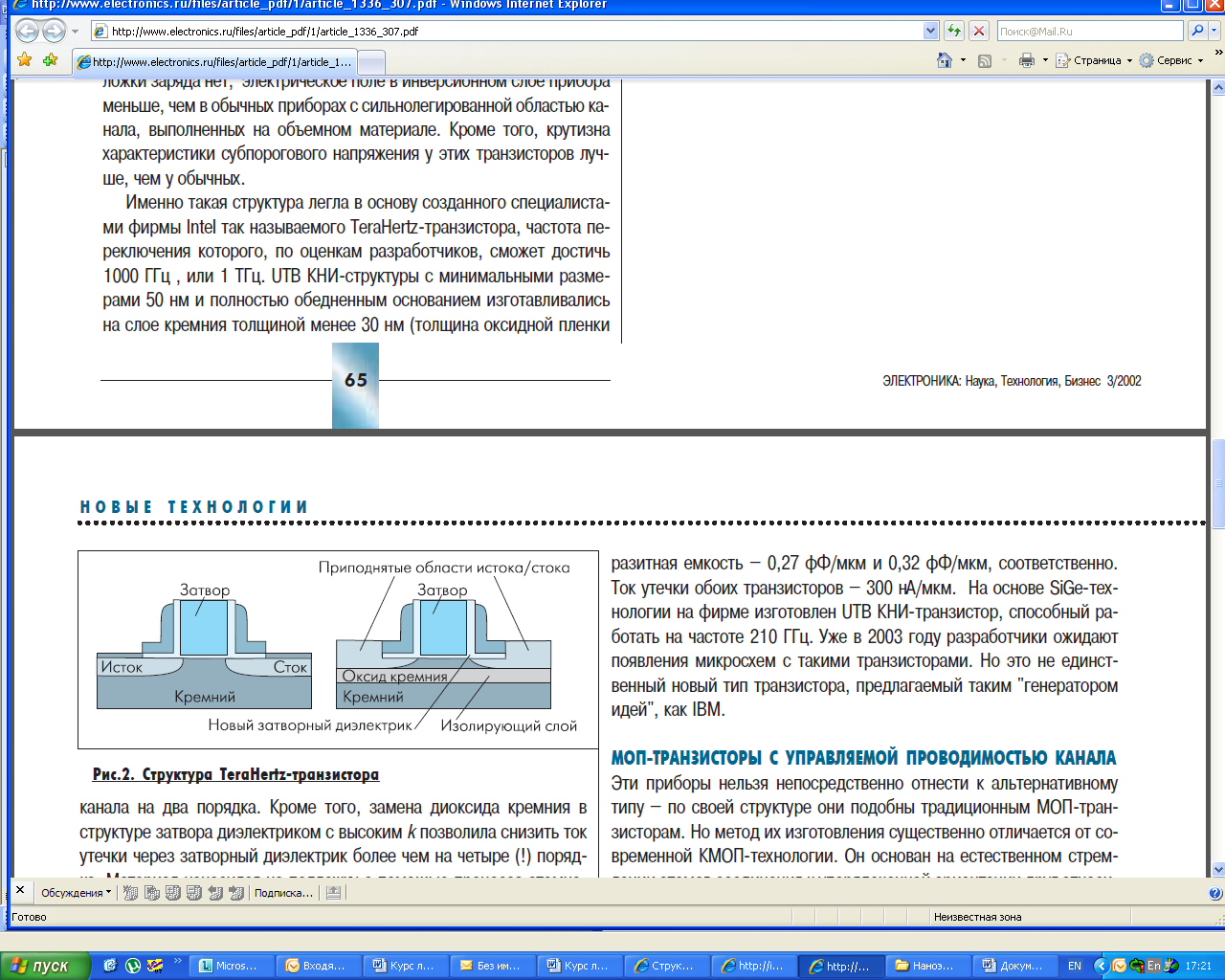

TeraHertz транзисторы. Структуры с ультратонким основанием изготавливались по различным технологиям, по одной из них фирма Intel создала транзистор TeraHertz. Этот транзистор имел полностью обедненное основание на слое кремния толщиной 30 нм. Для TeraHertz -транзисторов характерна низкая емкость перехода, высокая стойкость к облучению, кроме того, они обладают высоким быстродействием и низкой потребляемой мощностью. При напряжении 1,3 В рабочий ток p-канального транзистора, например, равен 650 мкА/мкм, а ток утечки всего 9 нА/мкм. Приборы с тонкой подложкой имеют значительное паразитное сопротивление, чтобы его снизить, области истока-стока приподнимались. Совершенствование конструкции транзисторов происходило в следующей последовательности.

Полевой транзистор на цельной подложке, на частично обедненном КНИ, и на полностью обедненном КНИ.

Рис.3.2 Структура КНИ-транзистора (а) и TeraHertz транзистора (б).

Формирование слоя оксида под всей структурой транзистора позволяет снизить токи утечки на два—четыре порядка в зависимости от типа диэлектрика, при этом толщина подзатворной пленки составляет 3 атомных слоя (8 нм). На рис. 3.2 представлена структура обычного и TеrаНеrtz-транзисторов. TeraHertz-транзисторы превосходят КМОП-приборы и позволяют создать на их основе микропроцессоры с топологическими нормами 20 нм, быстродействием до 20 ГГц и рабочим напряжением 1 В. В чипе микропроцессора будет находиться от 109 до 1012 ТеrаHertz-транзисторов.

Основным недостатком КНИ-структур с частичным обеднением подложки является эффект плавающей квази- нейтральной подложки. Фирме IBM удалось на основе SiGe- технологии создать структуры с минимальной технологической нормой 35 нм.