file1

.pdf81

5.4 Умовне позначення мікросхем пам’яті

Умовне позначення мікросхем пам’яті складається з трьох полів: основного – де знаходиться інформація про функціональне призначення мікросхеми й двох доповнювальних, в яких розміщується інформація про функціональне призначення кожного виводу й тип сигналів на входах даних. При необхідності, доповнювальні поля можуть розділюватись на групи однакових, по функціональні ознаці, виводів – адресні, керувальні, інформаційні. Розміри кожного з полів встановлюються відповідно до ДСТУ на зображення інтегральних мікросхем.

В залежності від функціонального призначення, в основному полі, можливі такі позначення:

–ROM – загальне позначення постійного запам’ятовувального пристрою, без уточнювання до якого типу відноситься. Якщо необхідно точно вказати використовуваний тип пристрою, то загальне позначення може доповнюватись

PROM – постійний запам’ятовувальний пристрій програмований маскою;

EPROM – репрограмований ПЗП з електричним записом і ультрафіолетовим стиранням;

EEPROM – репрограмований ПЗП з електричним записом і електричним стиранням.

–RAM – умовне позначення оперативного запам’ятовувального пристрою статичного типу;

–RAMD – умовне позначення оперативного запам’ятовувального пристрою динамічного типу;

–CAM – умовне позначення асоціативного запам’ятовувального

пристрою.

У лівому доповнювальному полі розміщується інформація про функціональне призначення входів, а у правому – виходів мікросхеми. Для різних типів ЗП виводи мають різне функціональне призначення, але в цілому,

єпевний набір, з якого можливо вибирати необхідні:

А0 –АN – адресні входи, номер розряду адреси показано у вигляді індексу; DI0 – DIM – входи даних. Для багаторозрядних ОЗП номер розряду

вхідного сигналу подається у вигляді індексу;

DO0 – DOM – виходи даних. Для багаторозрядних ЗП номер розряду вхідного сигналу подається у вигляді індексу;

DIO0 – DIOМ – входи/виходи даних. Виводи, функції яких об’єднано і вибір необхідної визначається сигналами керування;

C (CLK) – вхід синхронізації. Призначено для прийому сигналу синхронізації від генератора тактових імпульсів

CAS – строб адреси стовпця;

RAS – строб адреси рядка;

EO – сигнал дозволу виходу;

82

ER (Enable Read) – сигнал дозволу стирання (обнулення вмісту ОЗП); RD (Read) – сигнал дозволу зчитування;

WR (Write) – сигнал дозволу запису;

W/R – сигнал керування процесом запису/читання; REF (refresh) – сигнал зовнішньої регенерації;

CS – сигнал вибору мікросхеми;

XACK – вхід сигналу кінця циклу запису/читання. Указує на закінчення циклу взаємодії динамічної пам’яті з центральним процесором. Формується контролером динамічної пам’яті;

SACK – вхід сигналу кінця циклу запису/читання. Указує на закінчення циклу взаємодії динамічної пам’яті з центральним процесором. Формується контролером динамічної пам’яті;

UРК – вхід напруги програмування;

UCC – вивід для подання напруги живлення;

GND – загальна лінія (цифрова «земля»).

Виводи UРК, UCC і GND на принципових схемах дозволяється не показувати.

В залежності від режиму роботи й можливостей формувати різні сигнали, виходи мікросхеми можуть перебувати у трьох станах – стан формування логічного 0, стан формування логічної 1 і у високоімпедансному стані (z-стані). Високоімпедансний стан відповідає стану виходу, який відключено від лінії. Крім того, в залежності від схемотехнічних особливостей вихідних каскадів мікросхем, виходи можуть бути: по-перше – з відкритим колектором (відкритим стіком) – це вихідний каскад на біполярному або МОН-транзисторі

уякого немає резистора у колі колектора або у колі стіку; по-друге – з відкритим емітером – це каскад на біполярному транзисторі у якого відсутній резистор у колі емітера. Для забезпечення правильної роботи таки схем необхідно передбачити підключення резистора необхідної величини. Наявність

умікросхеми таких особливостей позначають спеціальними знаками:

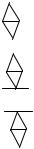

–вихід з трьома станами;

–вихід з відкритим колектором;

–вихід з відкритим емітером.

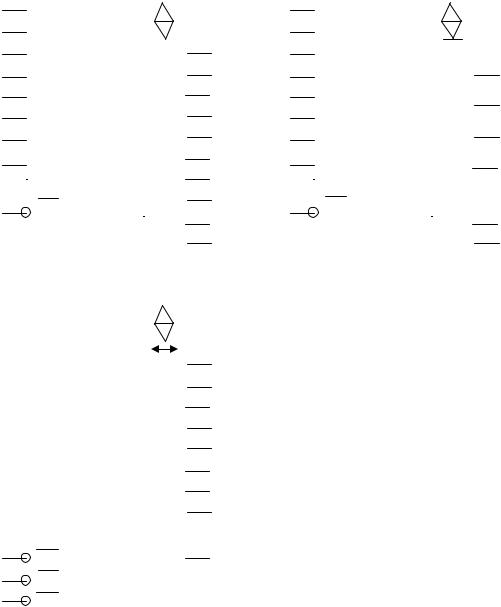

Приклади зображення мікросхем ПЗП різних типів подано на рис. 5.9 На рис. 5.9 а зображена мікросхема ПЗП програмована матрицею,

ємністю 256 байт, з виходами, що можуть набувати три стани. Сигнал вибору мікросхеми CS має активний рівень, що дорівнює логічному 0. Тому для зчитування вмісту комірки необхідно подати код адреси і сигнал логічного 0 на вхід CS); на рис. 5.9 б показана мікросхема РПЗП програмована однократно з організацією 256 × 4. Вихідні каскади якої побудовано за схемою з відкритим колектором. Керування зчитуванням відбувається як у попередньому випадку.

83

Сигнал логічної 1 на вході CS переводить мікросхему у режим збереження інформації; на рис. 5.9 в показана мікросхема РПЗП з електричним стиранням. Виводи мікросхеми двоспрямовані. Вибір режиму роботи відбувається у відповідності з табл. 5.1

|

A0 |

|

|

|

|

|

|

|

|

|

|

|

ROM |

|

|

|

|

|

|

|

A1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DO0 |

|

|

|

|

A2 |

|

|

|

|

|

|

|

|

|

A3 |

|

|

|

|

|

DO1 |

|

|

|

A4 |

|

|

|

|

|

DO2 |

|

|

|

A5 |

|

|

|

|

|

DO3 |

|

|

|

A6 |

|

|

|

|

|

DO4 |

|

|

|

A7 |

|

|

|

|

|

DO5 |

|

|

|

|

|

|

|

|

|

DO6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

|

|

|

|

|

DO7 |

|

|

|

|

|

|

|

|

UCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

|

|

|

|

|

a) |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

A0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EPROM |

|

|

|

|

|||

|

A1 |

|

|

|

|

|

|||

|

|

|

|

|

|

||||

|

A2 |

|

|

|

|

|

DIO0 |

|

|

|

|

|

|

|

|

|

|

||

|

A3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIO1 |

|

|

|

|

A4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIO2 |

|

|

|

|

|

|

|

|

|

|

|

||

|

A5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIO3 |

|

|

|

|

|

|

|

|

|

|

|

||

|

A6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIO4 |

|

|

|

|

A7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIO5 |

|

|

|

|

A8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIO6 |

|

|

|

|

A9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DIO7 |

|

|

|

|

A10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OE |

|

|

|

|

|

UPR |

|

|

|

CS |

|

|

|

|

|

GND |

|

|

|

PR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

в) |

|

|

|||

A0 |

|

|

|

|

|

PROM |

|

|

|

A1 |

|

|

|

|

|

|

|

|

|

A2 |

|

|

|

DO0 |

A3 |

|

|

|

|

A4 |

|

|

|

DO1 |

A5 |

|

|

|

|

|

|

|

|

|

A6 |

|

|

|

DO2 |

A7 |

|

|

|

DO3 |

CS |

|

|

|

|

|

|

|

UCC |

|

|

|

|

|

|

|

|

|

|

GND |

|

|

б) |

||

Рисунок 5.9 – Умовні графічні позначення мікросхем ПЗП

84

Таблиця 5.1 – Таблиця роботи мікросхеми РПЗП

|

Назва сигналу, значення сигналу |

|

Режим роботи |

||

CS |

EO |

A0 –A10 |

DIO0–DIO7 |

UPR |

Зберігання |

1 |

X |

X |

Z |

Ucc |

|

1 |

0 |

X |

0 |

UPR |

Стирання |

1 |

1 |

A |

D0 – D7 |

UPR |

Програмування |

0 |

0 |

A |

D0 – D7 |

Ucc |

Зчитування |

В таблиці буквами позначено: Х індиферентний стан, А – десятирозрядний код адреси, Ucc – напруга живлення, UPR – напруга переривання.

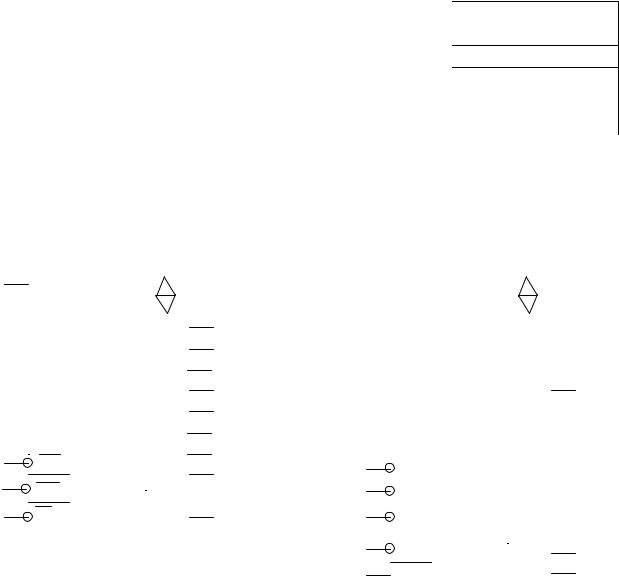

Приклади умовних графічних зображень ОЗП показано на рис. 5.10

|

|

A0 |

|

|

|

|

|

|

|

|

|

|

A0 |

|

|

|

|

|||||

|

|

RAM |

|

|

|

RAMD |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

A1 |

|

|

|

|

|

|

|

|

|

A1 |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

A2 |

|

|

|

DIO0 |

|

|

|

|

|

|

A2 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

A3 |

|

|

|

DIO1 |

|

|

|

|

|

|

A3 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

A4 |

|

|

|

DIO2 |

|

|

|

|

|

|

A4 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

A5 |

|

|

|

DIO3 |

|

|

|

|

|

|

A5 |

|

|

|

DO |

|||||

|

|

|

|

|

|

|||||||||||||||||

|

|

A6 |

|

|

|

DIO4 |

|

|

|

|

|

|

A6 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

A7 |

|

|

|

DIO5 |

|

|

|

|

|

|

A7 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

DIO6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

RAS |

|

|

|

|

|||||||||

|

|

|

|

|

DIO7 |

|

|

|

|

|

|

|

|

|||||||||

|

|

OE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAS |

|

|

|

|

|

|

|

|||

|

|

|

|

UCC |

|

|

|

|

||||||||||||||

|

|

W/R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

GND |

|

|

|

|

|

|

CS |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

W/R |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UCC |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

DI |

|

|

|

|

GND |

||||

|

|

|

|

|

а) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б) |

|||||

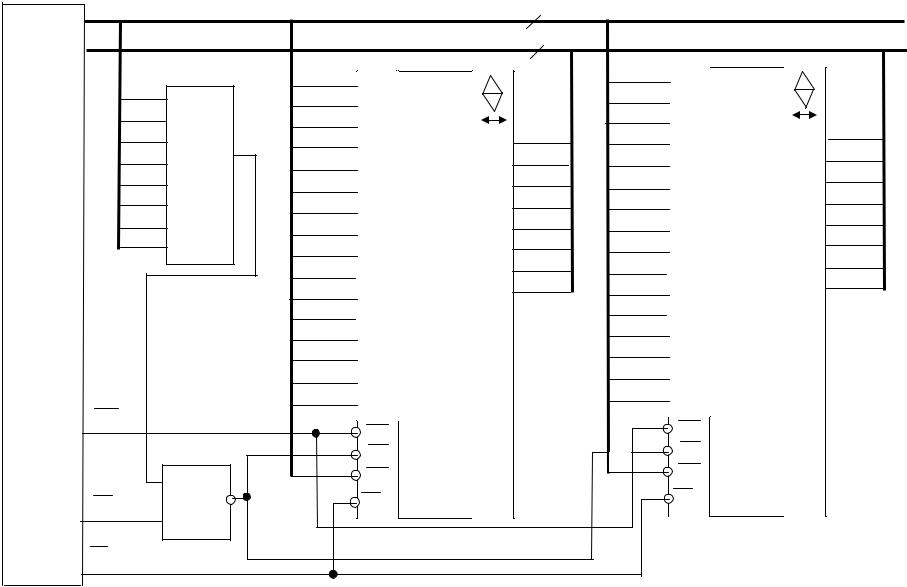

Рисунок 5.10 – Приклади умовних графічних позначень мікросхем ОЗП

На рис. 5.10 а зображено умовне графічне позначення мікросхеми ОЗП статичного типу з організацією 256 × 8. Керування режимом роботи здійснюється сигналами OE, CS, W/R відповідно до табл. 5.2.

На рис. 5.10 б зображена ОЗП динамічного типу з організацією 64К × 1, так як її 8 входів даних адресують масив пам’яті 256 × 256 ЕП. Керування режимами роботи такої мікросхеми відбувається відповідно до табл. 5.3.

|

|

|

|

|

|

|

|

|

|

|

85 |

Таблиця 5.2 – Таблиця істинності мікросхеми ОЗП |

|

|

|

||||||||

|

|

Назва сигналу, значення сигналу |

|

|

Режим |

||||||

CS |

OE |

|

|

W/R |

A0–A7 |

DIO0–DIO7 |

роботи |

||||

1 |

|

X |

|

|

X |

|

X |

|

Z |

Зберігання |

|

0 |

|

X |

|

|

0 |

|

A |

0 |

Запис 0 |

||

0 |

|

X |

|

|

0 |

|

A |

1 |

Запис 1 |

||

0 |

|

1 |

|

|

1 |

|

A |

|

Z |

Зчитування |

|

|

|

|

|

|

|

|

|

|

|

|

без видачі |

0 |

|

0 |

|

|

1 |

|

A |

|

D0–D7 |

Зчитування |

|

Таблиця 5.3 – Таблиця істинності мікросхеми ОЗП динамічного типу |

|||||||||||

|

|

Назва сигналу, значення сигналу |

|

|

Режим |

||||||

RAS |

|

CAS |

W/R |

|

A |

|

DI |

|

DO |

роботи |

|

1 |

|

1 |

|

X |

|

X |

|

X |

|

Z |

Зберігання |

1 |

|

0 |

|

X |

|

X |

|

X |

|

Z |

Зберігання |

0 |

|

1 |

|

X |

|

A |

|

X |

|

Z |

Регенерація |

0 |

|

0 |

0 |

|

A |

|

0 |

|

Z |

Запис 0 |

|

0 |

|

0 |

0 |

|

A |

|

1 |

|

Z |

Запис 1 |

|

0 |

|

0 |

1 |

|

A |

|

X |

|

D |

Зчитування |

|

Контрольні запитання:

1 Які умовні позначення використовуються для позначення типу вихідних ліній у ВІС?

2 Які виводи ВІС пам’яті призначено для прийому даних і як їх можливо організувати?

3 У яких трьох станах можуть находитися виводи вводу/виведення даних до ВІС пам’яті?

5.5Побудування модуля запам’ятовувального пристрою МПС з заданою організацією

Задача побудови модуля (блоку) ЗП в залежності від завдання і початкових умов може вирішуватися у різний спосіб. Умови задачі також можуть мати свої відзнаки в залежності від конкретних умов функціонування цього блоку.

Технічне завдання на розробку модуля ЗП повинно вміщувати:

• технічні характеристики МПС? для якої буде розроблюватися модуль: потрібна інформаційна ємність, розрядність та типи сигналів шини адреси та шини даних, розподіл адресного простору, наявність сигналів керування і їх рівні, довжина ліній проходження сигналів, інформаційна організація модуля пам’яті, наявність блоків живлення – рівні напруг та величини електричних струмів, що вони забезпечують тощо;

86

•часові характеристики сигналів керування: тривалість імпульсів керування, часові затримки між ними, співвідношення між перепадами цих сигналів;

•часові характеристики сигналів, які формуються блоком, що розроблюється, їх співвідношення з внутрішніми і зовнішніми сигналами в МПС ;

•електричні характеристики сигналів, на виході блоку ЗП: рівні напруги, навантажувальна спроможність виходів блоку.

Головна задача, що при цьому вирішується – забезпечення необхідної інформаційної ємності і забезпечення розрядності сигналів даних. Вирішення цієї задачі, в залежності від наявності мікросхем пам’яті може бути двох видів:

–в номенклатурі мікросхем пам’яті існує ВІС, яка відповідає завданню на інформаційну організацію модуля і забезпечує відповідні часові характеристики. В цьому випадку мікросхема встановлюється у МПС і виконується узгодження рівней сигналів керування або їх формування в разі необхідності. На цьому побудування модуля пам’яті вважається закінченим.

–в номенклатурі мікросхем пам’яті не існує ВІС, яка відповідає завданню на організацію модуля. В цьому випадку необхідно з наявних типів ВІС побудувати схему, що буде відповідати завданню. Ця задача має два варіанти: по-перше – у наявності є мікросхеми, що мають необхідну інформаційну ємність, але мають меншу розрядність даних, по-друге у наявності можуть бути ВІС, які мають меншу інформаційну ємність, ніж задано, але забезпечують розрядність шини даних.

Побудування модулів пам’яті ПЗП і ОЗП відбувається аналогічно. Різниця між ними полягає лише у необхідності забезпечення і формування специфічних, для кожного з них, сигналів керування.

Розглянемо приклад побудування ПЗП для використання у МПС, яка має 24-розрядну шину адреси, 8-розрядну шину даних і на шині керування якої формуються сигнали:

o |

OE |

– з активним рівнем логічного 0, окремо для блоку ПЗП; |

|

o |

W |

/ |

R – сигнал керування процесом запису/зчитування, активний |

рівень логічного 0 має сигнал W;

інформаційна організація модуля, що розроблюється становить 115К × 8, в модулі пам’яті необхідно використовувати мікросхему РПЗП-УФ типу АМ27С512, що має організацію 64К × 8. Початкова адреса комірки пам’яті для модуля – 000000В.

По-перше, визначимо кількість мікросхем для забезпечення необхідної організації

N = 11564KK××88 =1,7968 ≈ 2

Якщо у результаті отримано дробове число, то його необхідно заокруглювати обов’язково до більшого цілого числа. По-друге, визначимо останню адресу комірки пам’яті модуля. Дві ВІС модуля повинні працювати по-черзі, обробляючи кожен по 64К інформації. У сумі обидві ВІС можуть

87

обробити 128К інформації, що буде відповідати 217 = 131072D адресам. Якщо подати це число у шістнадцятковій системі числення, то отримаємо число 1FFFFH, яке й буде останньою адресою модуля. Це число більше ніж задане – 115К, це означає, що останні комірки пам’яті модуля ніколи використовуватись не будуть.

ВІС, яку необхідно використовувати має такі виводи: шістнадцять адресних входів – A0 – A15; вісім виходів даних – DO0 – DO7; входи керування –

OE , CS і CE . Таким чином, необхідно з’єднати 2 ВІС з шинами МПС і між собою так, щоб забезпечити черегування їх роботи в залежності від встановлення адреси.

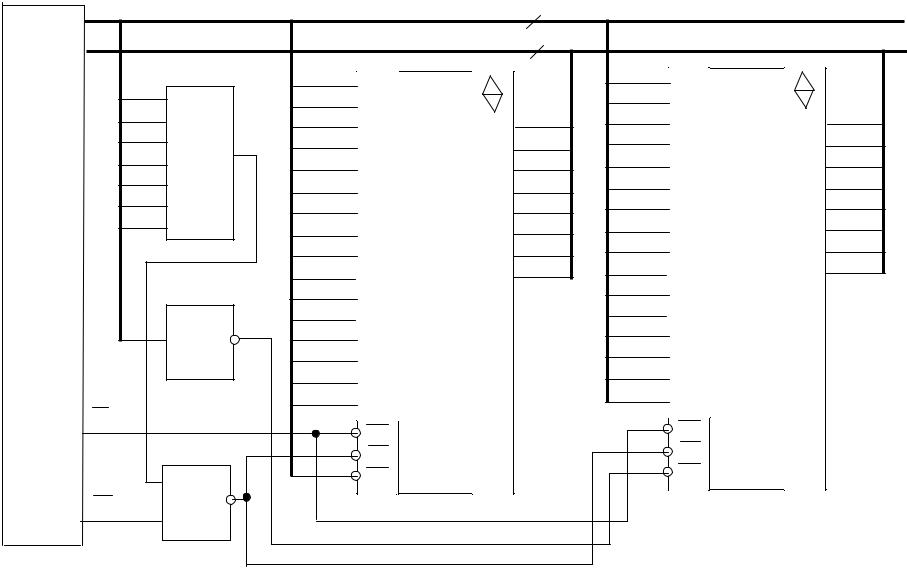

Схема блоку приведена на рис. 5.11.

Таблиця істинності мікросхеми АМ27С512 приведена у табл. 5.4

Таблиця 5.4 – Таблиця істинності мікросхеми АМ27С512

|

Назва сигналу, значення сигналу |

|

Режим роботи |

||

CE |

OE |

CS |

A0–A15 |

DO |

|

1 |

X |

X |

X |

z |

Не активна |

0 |

1 |

X |

X |

z |

Не активна |

0 |

0 |

1 |

X |

z |

Не активна |

0 |

1 |

0 |

X |

z |

Зберігання |

0 |

0 |

0 |

A |

D |

Читання |

Робота кожної з мікросхем відбувається відповідно до цієї таблиці за сигналами керування, що надходять від МПС. Робота модуля відбувається в діапазоні адрес, який був визначений раніше. Якщо МПС формує адресу більшу ніж 01FFFFН, то на виході 7-входового елементу АБО (елемент DD1) формується сигнал логічної 1, який з’явиться на виході 2-входового елементу АБО (елемент DD2) і переведе обидві мікросхеми ВІС до неактивного стану.

Вибір однієї з двох мікросхем ПЗП відбувається сигналом A16 (лінія 17 адресної шини). Якщо на цій лінії є сигнал логічного 0 адреси в діапазоні 000000Н – 00FFFFН), то дозволяється робота мікросхеми DD4 на вхід СЕ якої надходить сигнал логічного 0. Якщо діапазон адрес, що виставлено на шину адреси становить 010000Н – 01FFFFН, то дозволяється зчитування з мікросхеми DD5 на вхід СЕ якої надходить сигнал логічного 0 з виходу інвертора . (елемент

DD3). Зчитування інформації відбувається сигналом W / R , що надходить на входи ОЕ обох мікросхем.

Розглянемо приклад побудування ПЗП для використання у МПС, яка має 24-розрядну шину адреси, 8-розрядну шину даних і на шині керування якої формуються сигнали:

o OE – з активним рівнем логічного 0, окремо для блоку ПЗП;

o W / R – сигнал керування процесом запису/зчитування, активний рівень логічного 0 має сигнал W;

88

|

|

|

|

|

|

24 |

|

|

|

|

|

|

|

МПС |

|

|

|

|

|

8 |

|

|

|

|

|

|

|

18 |

DD1 |

1 |

10 |

A0 |

|

DD4 |

1 |

10 |

A0 |

|

DD5 |

||

1 |

2 |

9 |

EPROM |

|

|

2 |

9 |

A1 |

EPROM |

|

|

||

19 |

A1 |

11 |

1 |

8 |

11 |

1 |

|||||||

|

|

3 |

8 |

|

|

3 |

A2 |

|

|||||

20 |

|

4 |

7 |

A2 |

DO0 12 2 |

4 |

7 |

A3 |

DO0 12 2 |

||||

21 |

|

5 |

6 |

A3 |

DO1 13 3 |

5 |

6 |

A4 |

DO1 13 3 |

||||

22 |

|

6 |

5 |

A4 |

DO2 15 4 |

6 |

5 |

A5 |

DO2 15 4 |

||||

23 |

|

7 |

4 |

A5 |

DO3 16 5 |

7 |

4 |

A6 |

DO3 16 5 |

||||

24 |

|

8 |

3 |

A6 |

DO4 |

17 |

6 |

8 |

3 |

A7 |

DO4 |

17 |

6 |

|

|

9 |

25 |

A7 |

DO5 |

18 |

7 |

9 |

25 |

DO5 |

18 |

7 |

|

|

|

10 |

24 |

A8 |

DO6 |

19 |

8 |

10 |

24 |

A8 |

DO6 |

19 |

8 |

|

DD2 |

11 |

21 |

A9 |

DO7 |

|

|

11 |

21 |

A9 |

DO7 |

|

|

|

A10 |

|

|

|

12 |

23 |

A10 |

|

|

|

|||

|

1 |

12 |

23 |

A11 |

|

|

|

A11 |

|

|

|

||

17 |

|

|

|

13 |

2 |

|

|

|

|||||

|

13 |

2 |

A12 |

|

|

|

A12 |

|

|

|

|||

|

|

|

|

|

14 |

26 |

|

|

|

||||

|

|

14 |

26 |

A13 |

|

|

|

A13 |

|

|

|

||

|

|

|

|

|

15 |

27 |

|

|

|

||||

|

|

15 |

27 |

A14 |

|

|

|

A14 |

|

|

|

||

|

|

|

|

|

16 |

1 |

|

|

|

||||

|

|

16 |

1 |

A15 |

|

|

|

A15 |

|

|

|

||

W/R |

|

|

|

|

|

20 |

|

|

|

||||

|

|

20 |

OE |

|

|

|

|

OE |

|

|

|

||

|

DD3 |

|

22 |

|

|

|

|

22 |

|

|

|

||

|

17 |

14 |

CS |

|

|

|

|

14 |

CS |

|

|

|

|

|

1 |

|

|

|

|

CE |

|

|

|

||||

|

|

|

CE |

|

|

|

|

|

|

|

|

||

CS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 5.11 – Модуль ПЗП з організацією 128К × 8 |

|

|

|

||||||||

89

інформаційна організація модуля, що розроблюється становить 64К × 16, але розрядність шини даних становить 16 розрядів (слово). В модулі пам’яті необхідно використовувати мікросхему ОПЗП статичного типу АМ21С512, що має організацію 64К × 8. Початкова адреса комірки пам’яті для модуля –

000000В.

Визначимо кількість мікросхем для забезпечення необхідної організації

= 115K ×16 = ≈ N 1,7968 2

64K ×8

Якщо у результаті отримано дробове число, то його необхідно заокруглювати обов’язково до більшого цілого числа.

Визначимо останню адресу комірки пам’яті модуля. Так як, інформаційна ємність модуля складає 64К, то остання адреса буде 00FFFFH/

ВІС, яку необхідно використовувати має такі виводи: шістнадцять адресних входів – A0 – A15; вісім входів/виходів даних – DІO0 – DІO7; входи

керування – OE , CS , CE і W / R .

Для збільшення кількості розрядів шини даних слід з’єднати мікросхеми таким чином, щоб забезпечити їх одночасну роботі з однаковими адресами.

Схема блоку приведена на рис. 5.12.

Робота мікросхем ОЗП відбувається згідно таблиці істинності табл. 5.5 відповідно сигналів керування, що надходять від МПС. Обидві мікросхеми працюють одночасно (паралельно сигналів адрес і сигналів керування).

Таблиця 5.5 – Таблиця істинності мікросхеми ОЗП типу АМ21С512

|

Назва сигналу, значення сигналу |

|

Режим роботи |

|||

CE |

OE |

CS |

W/R |

A0–A15 |

DІO0–DІO8 |

Неактивний стан |

1 |

1 |

1 |

X |

X |

z |

|

1 |

1 |

0 |

X |

X |

z |

Неактивний стан |

0 |

1 |

0 |

X |

X |

z |

Зберігання |

0 |

0 |

0 |

1 |

А |

DІ |

Запис вхідних даних |

0 |

0 |

0 |

0 |

А |

DO |

Зчитування даних |

Контрольні запитання:

1 Які головні задачі вирішуються при побудуванні пристроїв ЗП? 2 Як відбувається нарощування інформаційної ємності ЗП?

3 Яким чином проводиться збільшення кількості розрядів виводів введення/виведення даних?

90

|

|

|

|

|

24 |

|

|

|

|

|

|

МПС |

|

|

|

|

16 |

|

|

|

|

|

|

17 |

DD1 |

1 |

12 |

A0 |

DD3 |

1 |

12 |

A0 |

RAM |

DD4 |

|

1 |

2 |

11 |

|

||||||||

18 |

2 |

11 |

A1 |

RAM |

|

3 |

10 |

A1 |

|

|

|

19 |

|

3 |

10 |

A2 |

13 |

1 |

A2 |

DIO0 |

13 9 |

||

|

4 |

9 |

4 |

9 |

A3 |

||||||

20 |

|

5 |

8 |

A3 |

DIO0 14 |

2 |

5 |

8 |

DIO1 |

14 10 |

|

21 |

|

6 |

7 |

A4 |

DIO1 15 |

3 |

6 |

7 |

A4 |

DIO2 |

15 11 |

22 |

|

7 |

6 |

A5 |

DIO2 17 |

4 |

7 |

6 |

A5 |

DIO3 |

17 12 |

23 |

|

8 |

5 |

A6 |

DIO3 18 |

5 |

8 |

5 |

A6 |

DIO4 |

18 13 |

24 |

|

9 |

27 |

A7 |

DIO4 19 |

6 |

9 |

27 |

A7 |

DIO5 |

19 `4 |

|

|

10 |

26 |

A8 |

DIO5 20 |

7 |

10 |

26 |

A8 |

DIO6 |

20 15 |

|

|

11 |

23 |

A9 |

DIO6 21 |

8 |

11 |

23 |

A9 |

DIO7 |

21 16 |

|

|

A10 |

DIO7 |

|

12 |

25 |

A10 |

|

|||

|

|

12 |

25 |

A11 |

|

|

A11 |

|

|

||

|

|

|

|

13 |

4 |

|

|

||||

|

|

13 |

4 |

A12 |

|

|

A12 |

|

|

||

|

|

|

|

14 |

28 |

|

|

||||

|

|

14 |

28 |

A13 |

|

|

A13 |

|

|

||

|

|

|

|

15 |

29 |

|

|

||||

|

|

15 |

29 |

A14 |

|

|

A14 |

|

|

||

|

|

|

|

16 |

3 |

|

|

||||

|

|

16 |

3 |

A15 |

|

|

A15 |

|

|

||

OE |

|

|

|

|

24 |

|

|

||||

|

|

24 |

OE |

|

|

|

OE |

|

|

||

|

DD2 |

|

16 |

CS |

|

|

|

16 |

CS |

|

|

|

1 |

17 |

22 |

CE |

|

|

17 |

22 |

CE |

|

|

CS |

|

|

31 |

W/R |

|

|

|

31 |

W/R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

W/R |

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 5.12 — Модуль ОЗП з організацією 64К × 16 |

|

|

|||||||