file1

.pdf

|

|

|

|

Q1 |

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

Q1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

~ |

|

~ |

|

|

~ |

|

~ |

|

|

|

Q3 |

|

|

|

|

|

~ |

|

|

|

~ |

|

|

|

~ |

|

|

~ |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

~ |

|

0 |

|

|

~ |

|

~ |

|

|

|

|

Q3 |

|

~ |

|

|

|

0 |

|

|

|

~ |

|

|

~ |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Q0 |

|

0 |

|

~ |

|

|

~ |

|

0 |

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

~ |

|

|

|

~ |

|

|

1 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

~ |

|

1 |

|

|

1 |

|

~ |

|

|

|

|

Q3 |

|

~ |

|

|

0 |

|

|

|

1 |

|

|

~ |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

||||||||||

|

|

Q |

|

|

|

|

|

|

|

|

|

|

Q |

|

|

Q2 |

||||||||||||||||||||||||||

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

2 |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

а) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

б) |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

Q1 |

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|

|

|

|

|

Q1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

~ |

|

~ |

|

|

~ |

|

~ |

|

|

|

Q3 |

|

~ |

|

|

|

~ |

|

~ |

|

~ |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

~ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

~ |

|

|

|

|

||||||||||

|

|

|

~ |

|

0 |

|

|

|

|

|

|

~~ |

|

|

|

|

|

|

|

|

|

|

|

~ |

|

|

|

0 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

~ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

~ |

|

|

|

~ |

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

~ |

|

~ |

|

|

1 |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

~ |

|

0 |

|

|

0 |

|

~ |

|

|

|

|

Q3 |

|

~ |

|

|

|

0 |

|

0 |

|

~ |

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

Q2 |

||||||||||

|

|

|

|

|

Q2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|||||||||||||||||

|

|

|

|

|

|

в) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

г) |

|

|

|

|

|||||

|

|

|

Q1 |

|

|

|

|

|

Q1 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

|

|

|

~ |

|

|

~ |

|

|

|

~ |

|

~ |

||

Q0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

~ |

|

|

0 |

|

|

|

~ |

|

~ |

Q3 |

||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

0 |

|

|

~ |

|

|

|

~ |

|

0 |

||

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

~ |

|

|

0 |

|

|

|

1 |

|

~ |

Q3 |

|||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

|

Q2 |

|

||

|

|

Q2 |

|

|

|||||||||

|

|

|

|

|

|

д) |

|

|

|

|

|||

51

Q3

Q3

Q3

Q3

Q3

Q3

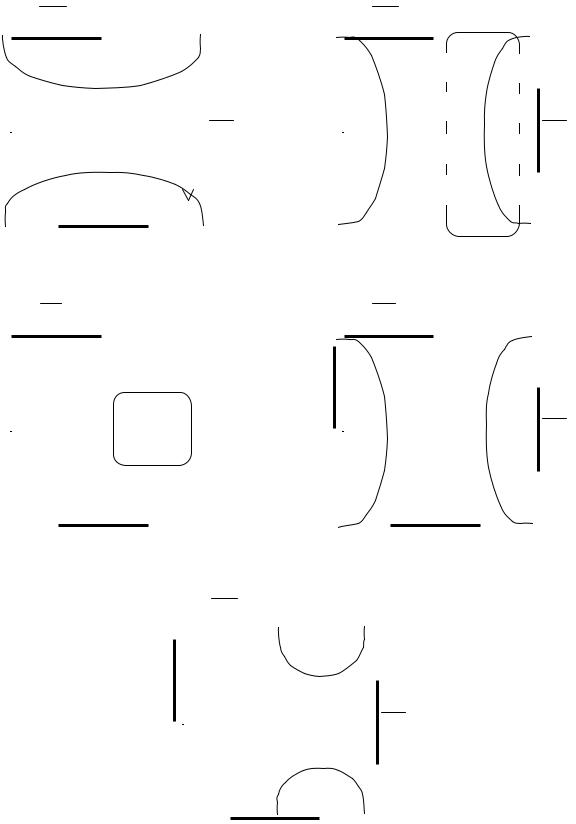

Рисунок 3.10 – Діаграми Вейча для мінімізації логічних функцій, які описують роботу пристроя КС 2

52

На рис. 3.10 б показана діаграма Вейча для мінімізації логічної функції y0, y6 . Видно, що значення цієї функції у МДНФ становить

y0 = y6 = Q2 Q1

Аналогічно виконуємо мінімізацію інших функцій. На рис 3.10 в показана діаграма Вейча для логічної функції y3, на рис. 3.10 г – для функції y5 і на рис.3.10 д – для функції y8 . Ці функції у МДНФ матимуть значення:

y3 = Q3 Q1

y5 = Q2

y8 = Q3 Q1

По отриманим значенням будуємо схему пристрою КС 2. Схема зображена на рис. 3.11. Нумерація проводів у шині зберігається такою як і на рис. 3.8.

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|||

|

|

1 |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

у0 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

у1 |

||||

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

7 |

|

|

|

|

|

|

|

|

|

у2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

3 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

& |

|

|

|

|

|

у3 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

8 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

у4 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|||||||||||||

|

|

5 |

|

|

|

|

|

|

|

|

у5 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

|

|

|

|

|

|

|

у6 |

||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

у7 |

|||||

|

|

7 |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

& |

|

|

|

|

|

у8 |

|||||||

|

|

3 |

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 3.11 – Схема пристрою КС 2 цифрового автомату

Контрольні запитання:

1 Побудувати схему з’єднання 4-х розрядного регістру станів (ЗП) з входами дешифратору станів ініціального частково визначеного ЦА, який працює за алгоритмом, що наведено у таблиці переходів

|

|

|

|

|

53 |

|

|

|

|

|

|

|

|

Стани ЦА, |

Побітне значення |

Перехід |

|

|||

алфавіту станів ЦА |

|

|||||

Q |

|

|

|

|

|

|

Q3 |

Q2 |

Q1 |

Q0 |

|

|

|

|

|

|

||||

Нульовий |

0 |

0 |

0 |

0 |

0 → 3 |

|

|

|

|

|

1 |

3 → 8 |

|

3 |

0 |

0 |

1 |

|

||

|

|

|

|

0 |

8 → 5 |

|

8 |

1 |

0 |

0 |

|

||

|

|

|

|

1 |

5 → 12 |

|

5 |

0 |

1 |

0 |

|

||

|

|

|

|

0 |

12 → 0 |

|

12 |

1 |

1 |

0 |

|

||

2 Побудувати схему пристрою КС2 відповідно наступної таблиці виходів

|

Побітне значення |

Вихід- |

|

|

Побітне значення алфавіту |

|

|

|||||||||

Стани |

алфавіту станів |

ний |

|

|

|

|

||||||||||

|

|

|

вихідних сигналів |

|

|

|||||||||||

ЦА, Z |

|

ЦА |

|

алфавіт |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

Q2 |

Q1 |

Q0 |

|

y8 |

y7 |

|

y6 |

y5 |

y4 |

y3 |

y2 |

|

y1 |

y0 |

Z0 |

0 |

0 |

0 |

0 |

Y0 |

0 |

0 |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

Z1 |

0 |

0 |

1 |

1 |

Y1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

Z2 |

1 |

0 |

0 |

0 |

Y2 |

0 |

0 |

|

1 |

1 |

0 |

1 |

0 |

|

0 |

1 |

Z3 |

0 |

1 |

0 |

1 |

Y3 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

1 |

0 |

Z4 |

1 |

1 |

0 |

0 |

Y4 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

|

0 |

1 |

54

4 ТИПОВІ ПРИСТРОЇ ОБЧИСЛЮВАЛЬНИХ СИСТЕМ (Для самостійного вивчення)

До типових пристроїв мікропроцесорних систем можна віднести такі пристрої: двійкові суматори, цифрові компаратори, арифметико-логічний пристрій, запам’ятовувальні пристрої, пристрої введення/виведення інформації, таймери, програмовні логічні інтегральні схеми (ПЛІС) тощо.

4.1 Суматори

Суматор – це вузол обчислювальної системи, що виконує арифметичне додавання кодів двійкових чисел. Суматор будується з комбінаційних схем, які виконують додавання двох однорозрядних двійкових чисел a i b, формують однорозрядний сигнал їх суми – S і сигнал перенесення в наступний старший розряд – C. Такі пристрої називають напівсуматорами і вони є елементною базою для побудови повних суматорів.

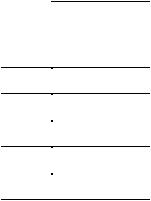

Умовне графічне позначення такої схеми показано на рис. 4.1.

a SM S

b C

Рисунок 4.1 – Умовне графічне позначення комбінаційного напівсуматора

Схема повного однорозрядного суматора буде відрізнятися тим, що одним з вхідних сигналів, додатково до операндів a i b, буде значення вхідного перенесення, яке буде додаватися до результату. Алгоритм роботи повного однорозрядного суматора можливо описати за допомогою таблиці істинності – табл.4.1.

Таблиця 4.1 – Таблиця істинності однорозрядного суматора

Вхідне |

Додаток |

Додаток |

Вихідне |

Сума |

перенесення |

перенесення |

|||

c |

a |

b |

C |

S |

|

|

|

||

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

55

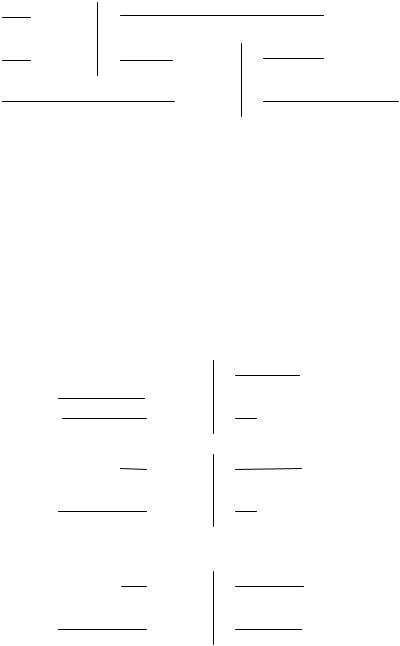

За даними цієї таблиці можливо виконати синтез схеми повного суматора. Після чого буде видно, що ця схема є поєднанням схем двох напівсуматорів. Схему повного суматора показано на рис. 4.2.

a |

|

|

|

|

|

|

|

С1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a |

SM |

С |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сі |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

С2 |

|

|

|

|

|

|

|

b |

|

|

|

|

|

|

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

b |

|

|

S |

|

|

|

|

|

|

a |

SM |

С |

|

|

|

|

|

|

|

|

|

||

с |

|

|

|

|

|

|

|

|

|

|

|

b |

|

|

S |

|

|

|

|

|

|

|

|

Sі |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 4.2 – Схема повного однорозрядного суматора

У цій схемі формуються два проміжні перенесення і одна проміжна сума, яки далі приймають участь у формуванні результату Вихідне перенесення формується як результат виконання логічної функції АБО сигналів двох проміжних перенесень.

Багаторозрядні суматори будуються як схеми паралельного з’єднання повних однорозрядних суматорів з послідовними лініями міжрозрядних перенесень. Приклад схеми такого суматора показано на рис. 4.3.

с0 |

|

|

|

|

c |

SM |

S |

|

S0 |

|

|

|

|

|

|||||

a0 |

|

|

|

|

a |

|

|

|

|

b0 |

|

|

|

|

b |

|

C |

|

S1 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

c |

SM |

S |

||

|

|

|

|

|

|||||

a1 |

|

|

|

|

a |

|

C |

|

|

|

|

|

|

|

|

|

|||

b1 |

|

|

|

|

b |

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

... |

|

|

|

|

... |

... |

|

|

|

|

Sn |

|||

|

|

|

|

|

|

|

|

||

an |

|

|

|

|

c |

SM |

S |

|

|

|

|

|

|

|

|||||

|

|

|

|

a |

|

|

|

Сn |

|

|

|

|

|

|

|

|

|||

bn |

|

|

|

|

b |

|

C |

|

|

Рисунок 4.3 – Схема n-розрядного комбінаційного паралельного суматора

Комбінаційний суматор можливо також використовувати для виконання операції віднімання чисел зі знаками, для чого операнди, що надходять на схему повинні подаватися у доповнювальному коді.

Важливою рисою комбінаційного паралельного суматора є затримка у колах формування перенесень. За характером розповсюдження перенесення суматори розділяють на три класи: суматори з порозрядним паралельним перенесенням, з паралельним перенесенням і з груповим перенесенням.

56

Паралельні суматори будуються за схемою, що показана на рис. 4.3, і характеризуються послідовним розповсюдженням сигналу перенесення від розряду до розряду, по ступені формуванням результату. Затримка формування суми, при наявності перенесень буде дорівнювати

Tпер =τ n,

де τ – затримка сигналу у одному розряді суматора; n – кількість розрядів. Видно, що ця величина швидко зростатиме із збільшенням кількості розрядів.

Таким чином, такий тип суматора характеризуються простотою схеми формування перенесення, але має низьку швидкодію.

Для усунення цього недоліку, можливо використовувати схему суматора

зпаралельним перенесенням. В такому суматорі додавання виконується як порозрядна операція і вхідне перенесення для кожного старшого розряду формується незалежно від формування перенесення у попередньому молодшому розряді. Для всіх розрядів сигнали перенесення також формуються паралельно. Формування сигналів перенесення відбувається в результаті формування і обробки додаткових двох сигналів: розповсюдження перенесення

(CRP – Carry Propagation) і генерування перенесення (Carry Generation).

Затримка отримання суми в такому суматорі складається із однакових значень затримки перенесення для всіх розрядів, які не залежать від кількості розрядів. Слід сказати, що апаратні затримки в такій схемі швидко зростають, відповідно до збільшення кількості розрядів, тому, в чистому вигляді, такий тип суматора майже не використовується. Для невеликої кількості розрядів (до 8) промисловість випускає спеціальні мікросхеми – схеми прискореного перенесення.

Для прискорення формування сигналів перенесення у суматорах з великою кількістю розрядів використовується принцип групового перенесення, відповідно до якого розрядна сітка розбивається на декілька груп з однаковою кількістю розрядів у кожній. Кожна група являє собою суматор, всередині котрого перенесення може формуватися як послідовно так і паралельно, а перенесення із групи в групу відбувається по тракту міжгрупового перенесення. Тракт міжгрупового перенесення також будується як паралельний або послідовний. Тракт паралельного перенесення будується таким чином, що міжгрупові перенесення формуються паралельно, по значенням розповсюдження перенесення і генерування перенесення між групами. У тракті послідовного перенесення сигнал перенесення з виходу молодшого розряду надходить на вхід перенесення наступної старшої.

Використання паралельного перенесення всередині групи з паралельним перенесенням між групами дозволяє будувати найбільш швидкодіючі суматори

зрозрядністю 24 – 64 біти. Загалом, вибір схеми суматора і формування перенесення в кожному випадку виконується по результатам аналізу апаратних витрат і забезпеченню необхідної швидкодії.

Суматори є елементною базою для побудови цифрових компараторів і арифметико-логічних пристроїв.

57

Контрольні запитання:

1Яке призначення схеми суматора?

2Які умови формування сигналів на виходах однорозрядного суматора?

3В чому полягає причина низької швидкодії паралельного суматора?

4Якими способами можливо підвищити швидкодію суматора?

4.2 Цифрові компаратори

Цифровим компаратором називають функціональний вузол обчислювальної техніки, який порівнює два багаторозрядних числа A i B між собою і результат порівняння подає у вигляді сигналів співвідношення між ними A = B, A < B, A > B.

Для порівняння сигналів використовується суматор, який виконує операцію віднімання (алгебраїчного додавання) вхідних чисел і по цих результатах формуються сигнали, що показують співвідношення між ними. Для виконання операції віднімання одне з вхідних чисел представляється у доповнювальному коді і подається на відповідні входи суматора, тому до складу цифрового компаратора входить схема, яка формує доповнювальний код одного з операндів. По результатах виконання операції A – B можливо зробити такі висновки:

якщо результат дорівнює 0, то це є ознакою того, що значення A i B співпадають;

якщо результат не дорівнює 0, а вихідне переповнення дорівнює 1, то

A < B;

якщо вихідне переповнення дорівнює 0, то це є ознакою A > B. Сигнали, що показують співвідношення між вхідними числами

формується за допомогою логічних схем. Функціональна схема цифрового компаратора для чотирьохрозрядних чисел приведена на рис. 4.4

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A = B |

||

|

|

|

|

|

|

|

a0 |

SM |

S0 |

|

|

1 |

|

|

|

1 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

a1 |

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

a2 |

|

S2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A > B |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

a3 |

|

S3 |

|

|

|

|

|

|

|

& |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Формувач |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

B |

|

|

|

|

b1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

доповнювального |

|

|

|

b2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A < B |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|||||

|

|

|

коду |

|

|

|

b3 |

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рисунок 4.4 – Функціональна схема чотирьохрозрядного цифрового компаратора

Умовне графічне позначення компаратора, який показано на рис. 4.4 наведено на рис. 4.5.

a0 = = a1

a2 a3 b0 b1 b2 b3

A=B

A>B

A<B

58

A=B

A>B

A<B

Рисунок 4.5 – Умовне графічне позначення чотирьохрозрядного цифрового компаратора

Для нарощування розрядності вхідних даних цифрові компаратори дозволяється каскадувати, для чого набір вхідних сигналів компаратора доповнюють вихідними сигналами попереднього каскаду A = B, A < B, A > B (рис. 4.5). Формування остаточного результату порівняння відбувається з урахуванням цих сигналів.

Контрольні запитання:

1 Як виконується порівняння двох двійкових чисел у цифровому компараторі?

2 На підставі якої ознаки приймається рішення, що A = B?

3 На підставі яких ознак приймається рішення, що A > B?

4 За допомогою яких сигналів проводиться порівняння багаторозрядних двійкових чисел?

4.3 Арифметико-логічний пристрій

Арифметико-логічні пристрої (АЛП) широко використовуються для побудування арифметичних вузлів, зокрема, АЛП є обов’язковою складовою частиною будь-якого процесору. АЛП використовується для виконання арифметичних і логічних операцій з даними, які до нього надходять і являють собою числа або будь-який інший вид інформації. Кількість розрядів у даних над якими виконується операція звичайно співпадає з кількістю розрядів у основних регістрах МПС. АЛП випускають як окремі мікросхеми або вони є невід’ємною складовою мікросхеми центрального процесора.

Операції, які виконуються в АЛП можливо розділити на такі групи:

арифметичні операції над двійковими числами з фіксованою комою;

арифметичні операції над двійковим числами з плавучою комою;

операції десяткової арифметики;

59

операції індексної арифметики (для модифікації адрес команд);

логічні операції з операндами, які є логічними змінними;

спеціальні арифметичні операції;

операції над алфавітно-цифровими полями.

До арифметичних операцій відносяться додавання, віднімання, множення і ділення двійкових і двійково-десяткових чисел, операції з рядками даних. До групи логічних операцій входять логічні операції диз’юнкція (логічне АБО), кон’юнкція (логічне ТА), виключне АБО, інверсія, логічні зсуви, порівняння кодів між собою тощо. До групи спеціальних арифметичних операцій входять операції нормалізації даних, арифметичні зсуви тощо.

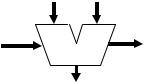

Арифметичні операції у АЛП виконуються за допомогою багаторозрядного суматора, а логічні – відповідними логічними схемами. В залежності від характеру використання цих пристроїв АЛП розділюються на блочні і багатофункціональні. В блочних АЛП для виконання різних типів операцій використовуються окремі блоки. Це дає змогу підвищити швидкодію, але збільшує апаратні витрати. В багатофункціональних АЛП для виконання операцій різних типів використовуються одні й ті ж пристрої, які комутуються по-різному, в залежності від виконуваної операції. Вибір операції і необхідних блоків здійснюється за допомогою сигналів керування, якими кодується операція , яку необхідно виконати. Крім результату АЛП формує набір спеціальних сигналів – ознаки результату (прапорці). Умовне позначення АЛП на схемах подано на рис. 4.6.

|

Операнд А Операнд В |

||

Код |

|

Ознаки |

|

|

результату |

||

операції |

|||

|

|||

Результат

Рисунок 4.6 – Умовне графічне позначення АЛП

Так як, двійковий суматор, який використовується в АЛП для виконання арифметичних операції, є комбінаційним пристроєм, то для одночасного подання двох операндів на його входи необхідно мати запам’ятовувальні пристрої для тимчасового зберігання операндів і результату.

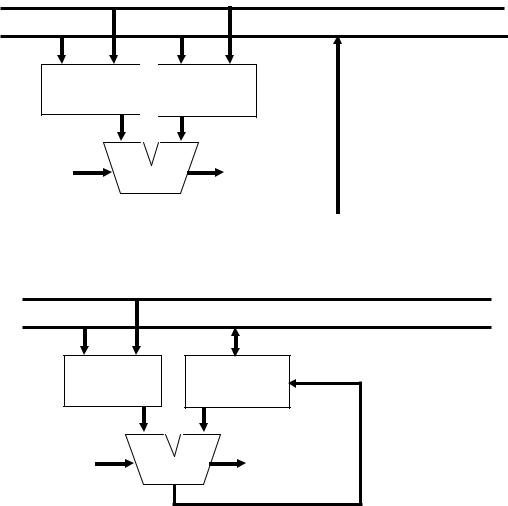

До АЛП операнди можуть надходити з двох регістрів загального призначення (РПЗ) або із регістра і комірки пам’яті, а результат надходить до регістру або до комірки пам’яті, які визначені як приймач результату. Така система має назву двохадресної тому, МПС повинна подати адреси обох операндів. Схему організації двохадресної системи показано на рис. 4.7а.

В інших МПС один з операндів до початку виконання команди обов’язково зберігається у акумуляторі, а після закінчення результат записується на місці операнду, який безповоротно втрачається. Така система

60

має назву одноадресної, так як необхідно адресувати лише один операнд. Схему організації одноадресної системи показано на рис. 4.7б.

Шина адреси

Шина даних

Операнд А

Операнд В

Операнд В

|

|

|

Ознаки |

|

Код |

||||

операції |

|

|

результату |

|

|

|

|

||

|

|

|

|

|

|

|

|

а) |

|

Шина адреси

Шина даних

Операнд А |

Акумулятор |

|

результат |

Код |

Ознаки |

операції |

результату |

|

б) |

Рисунок 4.7 – Схема організації двохадресного (а) і одноадресного (б) АЛП

До важливої характерної ознаки АЛП відноситься формування ним ознак результату (прапорців) – тобто деяких властивостей результату, які можуть вплинути на подальше виконання програми. Ознаки результату формуються після отримання результату і записуються у спеціальний регістр – регістр ознак результату (або інші назви цього регістру – регістр прапорців, регістр стану), де вони зберігаються до формування результату наступної операції. Слід сказати, що ознаки результату формують лише команди арифметичних і логічних операцій. Регістр ознак, в залежності від типу мікропроцесора, може мати різну кількість розрядів, які відповідають властивостям результату і зберігають інформацію про стан деяких апаратних або програмних компонентів процесора. Формат регістру ознак для відповідної мікросхеми може бути таким, як показано на рис. 4.8.