Metod_labs_v5

.pdf

М І Н І С Т Е Р С Т В О О С В І Т И Т А Н А У К И У К Р А Ї Н И

НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ “ЛЬВІВСЬКА ПОЛІТЕХНІКА”

Кафедра ЕОМ

ОСНОВИ ПРОЕКТУВАННЯ ЦИФРОВИХ ЗАСОБІВ НА ПЛІС

МЕТОДИЧНІ ВКАЗІВКИ

до виконання лабораторних робіт з курсу: “Основи проектування цифрових засобів на ПЛІС”

для студентів базового напряму 6.050102 - “Комп’ютерна інженерія”

Затверджено

на засіданні кафедри ”Електронних обчислювальних машин”

Протокол № ___ від ____________ року

Львів – 2013

Основи проектування цифрових засобів на ПЛІС: Методичні вказівки до виконання лабораторних робіт з курсу “Основи проектування цифрових засобів на ПЛІС” для студентів базового напряму 6.050102 - “Комп’ютерна інженерія” / Укладачі: Мельник А.О., Сало А.М., Грос В.В.– Львів: Національний університет “Львівська політехніка”, 2013, ___ с.

Укладачі |

Мельник А.О., професор, завідувач кафедри ЕОМ |

|

Сало А.М., к.т.н., доцент |

|

Грос В.В., асистент |

Рецензенти |

|

Відповідальний за випуск:

ЛАБОРАТОРНА РОБОТА №1

САПР XILINX WEBPACK. ПРОЕКТУВАННЯ НАЙПРОСТІШИХ ВУЗЛІВ.

Мета роботи: засвоєння навичок роботи у середовищі Xilinx WebPack, навчитись створювати проекти в САПР Xilinx WebPack.

Завдання: В САПР WebPack імплементувати в ПЛІС Virtex-IV запропонований базовий проект «ФАЛ» та проект згідно варіанту. Імплементування верифікувати. Скласти звіт з виконання лабораторних досліджень та захистити його.

Зауваження: Обов'язкова умова - назви проектів, вкладених файлів, створених елементів і всіх зв'язків на схемах, на екранах і у звітах з лабораторних робіт повинні починатися з ініціалів студентів, які ці завдання виконували!

ТЕОРЕТИЧНІ ВІДОМОСТІ

Вступ

Головним напрямком розвитку сучасної мікроелектроніки є створення однокристальних систем (SOC - System On Chip). Такі системи значно підвищують надійність, знижують енергоспоживання та вартість складних електронних приладів. Основними досягненнями в цій галузі є три типи одно кристальних систем: мікроконтролери, спеціалізовані надвеликі інтегральні схеми (НВІС) та програмовані логічні інтегральні схеми (ПЛІС).

Фірма Xilinx, одна із провідних світових виробників ПЛІС, надає розробникам широкий спектр кристалів з різною технологією виробництва, ступенем інтеграції, архітектурою, швидкодією, споживаною потужністю й напругою живлення, що випускають у різних типах корпусів в декількох варіантах виконання, в тому числі промислове, військове й радіаційно стійке . Переваги ПЛІС у порівнянні з «непрограмованою логікою»:

–висока швидкодія;

–можливість перепрограмування безпосередньо в системі;

–високий ступінь інтеграції, що дозволяє розмістити цифровий пристрій в одному кристалі й тим самим знизити час і витрати на трасування й виробництво друкованих плат;

–скорочення циклу розробки й виробництва;

–наявність потужних інструментальних САПР, що дозволяють усунути можливі помилки в процесі проектування пристроїв;

–порівняно низька вартість (у перерахуванні на один логічний вентиль);

–можливість подальшої реалізації проектів ПЛІС для серійного виробництва у вигляді замовлених НВІС, що дозволяє значно знизити їхню

вартість. У виданні розглянуто повний цикл розробки дискретних пристроїв на ПЛІС фірми Xilinx у вільно розповсюджуваному пакеті Webpack.

Основні характеристики пакета WebPACK

Програмні засоби WebPACK ISE являють собою систему наскрізного проектування, що реалізує всі етапи створення цифрового пристрою на базі ПЛІС, в тому числі: розробка проекту, синтез, моделювання, трасування й завантаження в кристал. Відмінні риси пакета:

–підтримка різних методів опису проектованих пристроїв;

–можливість використання проектів, підготовлених в інших системах проектування, у тому числі в середовищі пакета Altera MAX+PlusII;

–наявність схемотехнічного редактора з набором великих бібліотек;

–інтелектуальні засоби створення HDL (Hardware Description Language)-

описів для мов опису апаратури VHDL, Verilog й ABEL HDL;

–високоефективні засоби синтезу HDL-проектів;

–розвинені засоби верифікації проекту, що дозволяють скоротити повний час розробки пристроїв;

–автоматичні засоби трасування проекту в різних сімействах ПЛІС Xilinx з урахуванням оптимізації по різних параметрах;

–засоби програмування кристалів сімейств ПЛІС Xilinx, виконаних за технологією CPLD й FPGA, що підтримують кілька типів завантажувальних кабелів JTAG-інтерфейсу;

–зручний інтерфейс користувача і наявність у кожному модулі пакета довідкової системи;

–наявність інтегрованого з пакетом САПР набору інструментів й утиліт інших фірм: утиліти генерації тестових сигналів HDL Bencher, програми моделювання ModelSim XE Starter і редактору діаграм станів StateCAD.

ПОРЯДОК ВИКОНАННЯ РОБОТИ

1 Запуск менеджера проектів Project Manager

1.1 Виконати File->New Project…

З’явиться вікно New Project Wizard (рис. 1.1).

Необхідно:

1)задати ім’я свого проекту (Name);

2)встановити робочий каталог (Working Directory:);

3)задати тип проекту – Top-level source type: Schematic;

4)натиснути клавішу “Next”.

Зверніть увагу! Назва проекту повинна починатися з ініціалів студента, який цей проект створює!

Рис. 1.1 Створення проекту GVV_lab1 з розташуванням в D:\HOME\KI- 4\GVV\GVV_LAB1

Далі згідно рис. 1.2 необхідно визначити серію ПЛІС, тип мікросхеми у серії, швидкодію мікросхеми, мову апаратного програмування та симулятор.

Рис. 1.2 Вибір цільової ПЛІС та симулятора

Рис. 1.3 – Автоматично згенероване резюме проекту GVV_lab1

Рис. 1.4 – Вікно навігатора проектів WebPack з новим проектом GVV_lab1

2. Схемна реалізація ФАЛ виду a&b v c&d v e&f.

2.1. Для створення нового модуля вихідного опису проекту треба виконати Project-> New Source… У діалоговій панелі, що відкрилася, необхідно вибрати тип нового модуля, задати його ім'я й указати місце розташування файлу на диску.

Рис. 2.1 Створення нового модуля вихідного опису проекту

2.2 Відкрити бібліотеку елементів клавішою  . На екрані з’явиться вікно бібліотеки сімейства мікросхем обраної серії згрупованих по категоріях.

. На екрані з’явиться вікно бібліотеки сімейства мікросхем обраної серії згрупованих по категоріях.

Рис. 2.2 Вікно бібліотеки сімейства мікросхем обраної серії

Вибрати з бібліотеки потрібні елементи і розмістити їх в робочій області схемного редактора:

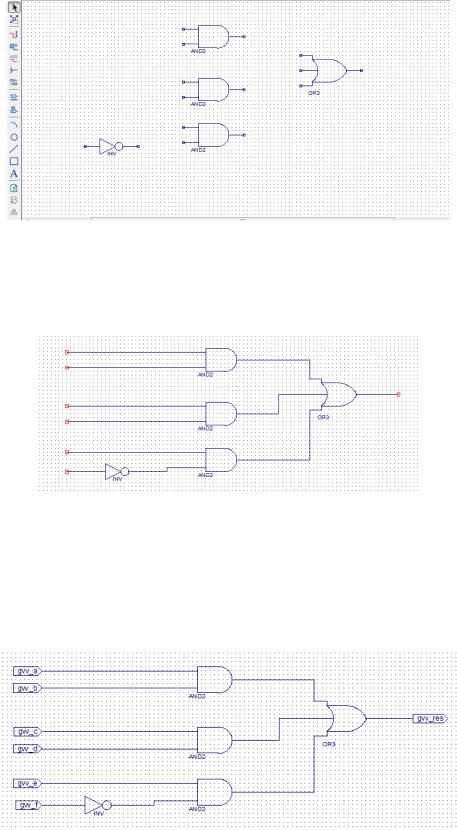

Рис.2.3 Вікно схемного редактора з розміщеними бібліотечними елементами

2.3 Задати режим створення зв’язків  , до кожного виводу задіяних елементів під’єднати зв’язки, довжиною приблизно рівній ширині елемента та зробити необхідні з’єднання на схемі для реалізації поставленого завдання.

, до кожного виводу задіяних елементів під’єднати зв’язки, довжиною приблизно рівній ширині елемента та зробити необхідні з’єднання на схемі для реалізації поставленого завдання.

Рис.2.4 Схема з’єднань логічних елементів для реалізації заданої ФАЛ

Двічі клацнувши на кожному зв’язку задати їхні імена – входи елементів назвати gvv_a, gvv_b, gvv_c, gvv_d, gvv_e, gvv_f, виходи – gvv_a_and_b, gvv_c_nand_d, gvv_e_and_nf, gvv_res.

2.3Натиснути на позначку  і перейти до режиму вводу вхідних

і перейти до режиму вводу вхідних

івихідних контактів ієрархічних схем.

Рис. 2.5 Під’єднання вхідних та вихідних контактів розробленої схеми реалізації ФАЛ

2.4 У вікні Processes запустити на виконання процес Synthesize. У процесі синтезу з файлів HDL-описів проектованого пристрою формується файл списку з'єднань у форматі EDIF. Відзначене відповідною піктограмою в рядку Synthesize завершення цього процесу дозволяє відкрити звіт про результати синтезу(View Text Report).

На етапі синтезу створено звіт, витяг з якого подаємо.

=============================================================

* Final Report

=============================================================

Final Results

RTL Top Level Output File Name |

: GVV_sch1.ngr |

|

|

||

Top Level Output File Name |

: GVV_sch1 |

|

|

||

Output Format |

: NGC |

|

|

|

|

Optimization Goal |

: Speed |

|

|

|

|

Keep Hierarchy |

: NO |

|

|

|

|

Design Statistics |

|

|

|

|

|

# IOs |

: 7 |

|

|

|

|

Cell Usage : |

|

|

|

|

|

# BELS |

: 5 |

|

|

|

|

# |

AND2 |

: 3 |

|

|

|

# |

INV |

: 1 |

|

|

|

# |

OR3 |

: 1 |

|

|

|

# IO Buffers |

: 7 |

|

|

|

|

# |

IBUF |

: 6 |

|

|

|

# |

OBUF |

: 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Device utilization summary: |

|

|

|

|

|

--------------------------- |

|

|

|

|

|

Selected Device : 4vlx15sf363-12 |

|

|

|

|

|

|

Number of Slices: |

1 |

out of |

6144 |

0% |

|

Number of 4 input LUTs: |

1 |

out of |

12288 |

0% |

|

Number of IOs: |

7 |

|

|

|

Number of bonded IOBs: |

7 |

out of |

240 |

2% |

|

Крім текстового звіту про виконання етапу синтезу, засоби пакета САПР серії Xilinx ISE дозволяють відобразити список з'єднань (netlist) проектованого пристрою на RTL рівні в схемотехнічній формі, якщо перед виконанням цього процесу для параметра Generate RTL Schematic було встановлено значення YES або ONLY. В якості компонентів принципової схеми, що відбиває RTL представлення синтезованого пристрою, застосовуються узагальнені елементи, вигляд яких не залежить від архітектурних особливостей сімейства ПЛІС, використовуваного для подальшої реалізації цього пристрою.

Для перегляду функціональної схеми слід у вікні процесів Processes Window помістити курсор на рядок View RTL Schematic і двічі клацнути лівою кнопкою миші. При цьому відкривається вікно програми, вид якого подібний зображенню вікна схемо-технічного редактора.

У вікні, відображається умовний графічний образ, що представляє модуль верхнього рівня ієрархії проекту. Крім того, у вікні вихідних модулів (Sources

Window) Навігатора проекту (Project Navigator) з'являється нова сторінка Design, на якій наводиться інформація по ієрархічній структурі та елементах синтезованого проекту.

Для переходу до функціональної схеми, яка відповідає списку з'єднань проектованого пристрою на RTL-рівні, слід помістити курсор миші на зображення умовного графічного образу чи на рядок з назвою модуля верхнього рівня ієрархії проекту, розташовану на сторінці Design вікна вихідних модулів (Sources Window), і двічі клацнути лівою кнопкою миші . В якості прикладу на рис. 2.6 наведена схема, відповідно списку з'єднань на RTL рівні VHDL опису ФАЛ.

Також передбачені засоби відображення результатів синтезу розроблюваних пристроїв на технологічному рівні у формі принципових схем. Склад компонентів принципової схеми, що відбиває уявлення синтезованого пристрою на технологічному рівні, залежить від типу архітектури застосовуваного сімейства ПЛІС.

Щоб сформувати уявлення про результати синтезу проектованого пристрою на технологічному рівні, необхідно у вікні процесів Processes Window помістити курсор на рядок View Technology Schematic і двічі клацнути лівою кнопкою миші.

Після цього в області розташування робочих вікон Навігатора проекту відкривається вікно перегляду.

При цьому у вікні вихідних модулів (Sources Window) Навігатора проекту додається сторінка Design, яка відкриває доступ до елементів ієрархічної структури синтезованого проекту. Перегляд результатів синтезу на технологічному рівні здійснюється тим же способом, що і в програмі RTL Viewer. Щоб продемонструвати відмінності двох розглянутих форм подання списку з'єднань синтезованого пристрою, на рис. 2.6 показано принципова схема, що відображає результати синтезу на технологічному рівні VHDL-опису ФАЛ.

Після завершення процесу синтезу проглядаємо RTL і технологічну схеми.

Рис. 2.6 Технологічна схема проекту GVV_lab1

3. Часова симуляція роботи проекту.

Створюємо додатковий файл проекту типу VHDL Test Bench:

Рис. 3.1 Створення VHDL Test Bench тесту

В первинному тексті автоматично згенерованого тест-бенч файлу: наш вентиль інстальовано, але вхідні сигнали не ініціалізовані та їхні зміни в часі автоматом не задекларовані. Для поведінкового моделювання вручну вносимо зміни в текст Test Bench файлу:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

LIBRARY UNISIM;

USE UNISIM.Vcomponents.ALL;

ENTITY GVV_sch1_GVV_sch1_sch_tb IS

END GVV_sch1_GVV_sch1_sch_tb;

ARCHITECTURE behavioral OF GVV_sch1_GVV_sch1_sch_tb IS

COMPONENT GVV_sch1 |

|

|

||

PORT( gvv_e |

: |

IN |

STD_LOGIC; |

|

gvv_f |

: |

IN |

STD_LOGIC; |

|

gvv_c |

: |

IN |

STD_LOGIC; |

|

gvv_d |

: |

IN |

STD_LOGIC; |

|

gvv_a |

: |

IN |

STD_LOGIC; |

|

gvv_b |

: |

IN |

STD_LOGIC; |

|

gvv_res : |

OUT |

STD_LOGIC); |

||

END COMPONENT; |

|

|

||

SIGNAL gvv_e |

: |

STD_LOGIC:='0'; |

||

SIGNAL gvv_f |

: |

STD_LOGIC:='0'; |

||

SIGNAL gvv_c |

: |

STD_LOGIC:='0'; |

||

SIGNAL gvv_d |

: |

STD_LOGIC:='0'; |

||

SIGNAL gvv_a |

: |

STD_LOGIC:='0'; |

||

SIGNAL gvv_b |

: |

STD_LOGIC:='0'; |

||

SIGNAL gvv_res: |

STD_LOGIC; |

|

||