- •2. Преобразования входной информации

- •Буквенно-цифровой код

- •3.1 Двоично-десятичный код, двоично-десятичные числа.

- •3.2 Двоичная арифметика.

- •3.4Арифметика в дополнительном коде.

- •Основные элементы цифровой микропроцессорной техники.

- •Асинхронные триггеры

- •Rs-триггер с инверсными входами

- •Синхронные триггеры со статическим управлением

- •Триггеры с динамическим управлением

- •Мультиплексоры

- •Демультиплексор

- •Сдвиговый регистр

- •Суммирующие двоичные счетчики

- •Вычитающий и реверсивный счетчики

- •Кольцевой счетчик

- •Делители частоты импульсной последовательности

- •Одноразрядный двоичный сумматор

- •Многоразрядные двоичные сумматоры

- •Программная модель 32-разрядных процессоров

- •Процессоры р6

- •Устройство управления. Принципы построения арифметико-логического устройства. Микропроцессорная память, регистры. Команды, процедуры их выполнения и способы адресации.

- •1. Pentium II

- •4. Pentium III

- •5. Pentium IV

- •2. Термоустойчивый корпус

- •Организация интерфейса в микропроцессоре. Способы обмена информацией в микропроцессорных средствах. Интерфейсы – средства сопряжения модулей в систему.

- •Структура процессора

- •Два подхода к построению процессоров

- •Цифровые автоматы

- •Функционирование микро-эвм. Режимы работы эвм: однопрограммные и многопрограммные; прерывания.

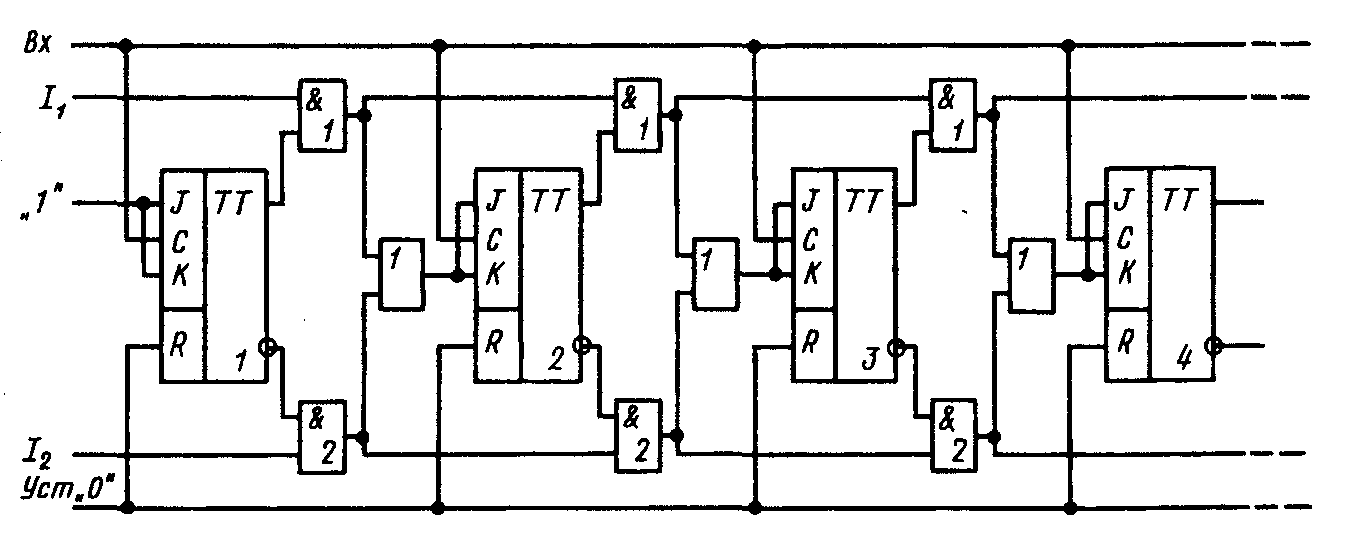

Суммирующие двоичные счетчики

В суммирующем счетчике поступление на вход очередного уровня лог. 1 (очередного импульса) вызывает увеличение на единицу хранимого в счетчике числа. Таким образом, в счетчике устанавливается число, которое получается путем суммирования предыдущего значения с единицей. Это суммирование проводится по обычным правилам сложения в двоичной системе счисления.

Вычитающий и реверсивный счетчики

В вычитающем счетчике поступление на вход очередного уровня лог.1 (очередного импульса) вызывает уменьшение хранившегося в счетчике числа на единицу.

Реверсивный счетчик допускает в процессе работы переключение из режима суммирования в режим вычитания и наоборот. В ней предусмотрены две цепи передачи переносов, одна из которых соответствует схеме суммирующего счетчика, другая — схеме вычитающего счетчика.

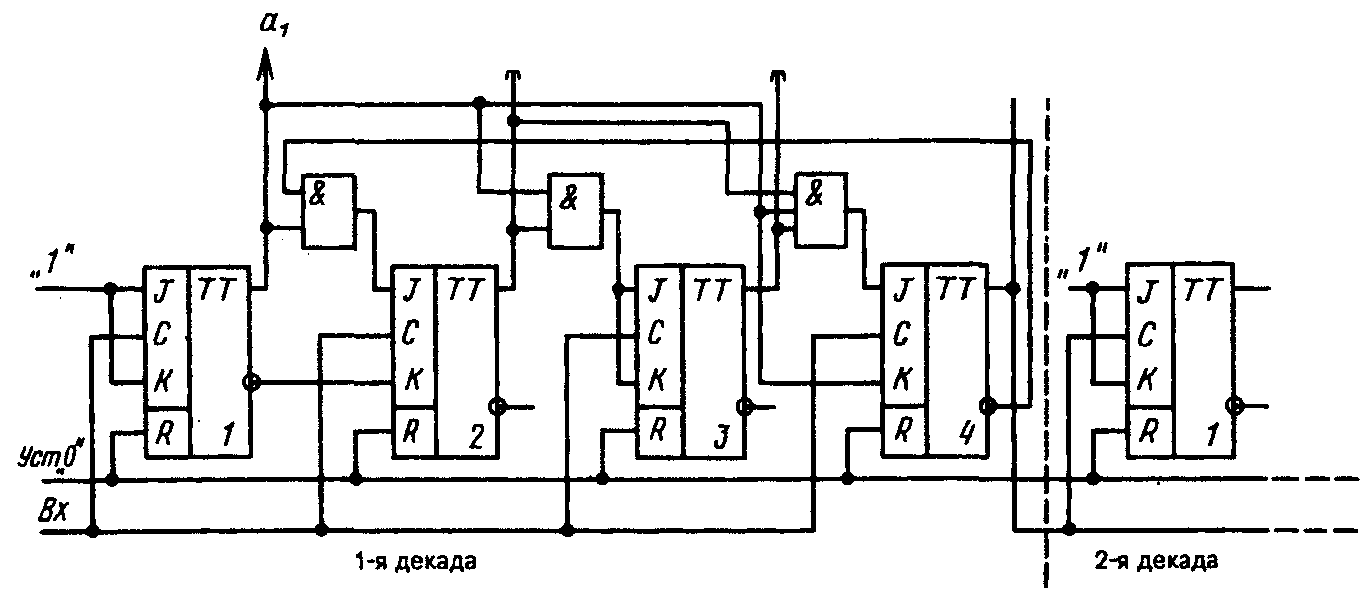

Десятичный счетчик

На рис. 4.8 была показана структура десятичного счетчика. Каждый десятичный разряд такого счетчика — декада — является двоичным счетчиком с периодом цикла N = 10.

Десятичные счетчики находят широкое применение в тех случаях, когда число поступающих импульсов необходимо представлять в привычной для человека десятичной системе счисления.

Рис.

4.8

Рис.

4.8

Рис.

4.9

Рис.

4.9

Кольцевой счетчик

Кольцевой счетчик строится в виде сдвигового регистра, в котором выдвигаемая из старшего разряда информация вводится в младший разряд.

Кольцевой счетчик обеспечивает высокую скорость работы.

Делители частоты импульсной последовательности

Делитель частоты — устройство, которое при подаче на его вход периодической последовательности импульсов формирует на выходе такую же последовательность, но имеющую частоту повторения импульсов, в некоторое число раз меньшую, чем частота импульсов входной последовательности.

Отличие делителей частоты от счетчиков состоит в следующем. В счетчике каждая комбинация состояний триггеров определяет в некоторой системе счисления число импульсов, поступивших к данному моменту времени. В делителе частоты последовательность состояний может быть выбрана произвольной, важно лишь обеспечить заданный период цикла N. Последовательность состояний выбирается из соображений обеспечения при заданном N наибольшей простоты межтриггерных связей. Эти связи должны выполняться непосредственным соединением выходов одних триггеров со входами других без логических элементов. Счетчик, имеющий то же значение N, может исполнять роль делителя частоты, однако следует иметь в виду, что такое решение будет неэкономичным.

4.8. СУММАТОРЫ

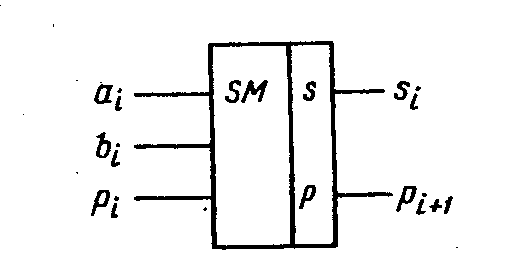

Одноразрядный двоичный сумматор

Из

рассмотренного принципа сложения

многоразрядных двоичных чисел

следует, что в каждом из разрядов

производятся однотипные действия:

определяется цифра суммы путем сложения

по модулю 2 цифр слагаемых и поступающего

в данный разряд переноса и формируется

перенос, передаваемый в следующий

разряд. Эти действия реализуются

одноразрядным

двоичным сумматором. Символическое

изображение такого сумматора показано

на рис. 4.10,а. Он имеет три входа для подачи

цифр разрядов слагаемых а,b;

и переноса р ; на выходах формируются

сумма s

и перенос рi+1,

предназначенный для передачи в следующий

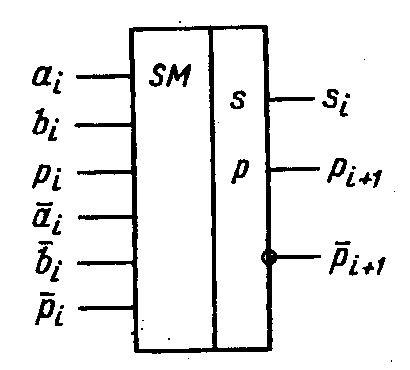

разряд. В одноразрядном сумматоре могут

предусматриваться входы для подачи

как прямых а,b,p

так и инверсных значений

входных переменных. Пример такого

одноразрядного сумматора приведен на

рис. 4.10,6.

входных переменных. Пример такого

одноразрядного сумматора приведен на

рис. 4.10,6.

a) б) Рис. 4.10