- •Программирование на языке ассемблера сигнального процессора tms320c6x

- •Введение

- •Рекомендуемая литература

- •Содержание отчета

- •Сохранение результатов лабораторной работы

- •1. Симулятор команд tms320c6201

- •Подготовка к работе

- •Задания и методические указания к их выполнению

- •2. Операции пересылки данных

- •Подготовка к работе

- •Задания и методические указания к их выполнению

- •3. Арифметические операции

- •Подготовка к работе

- •Задания и методические указания к их выполнению

- •4. Ветвление с простым условием

- •Подготовка к работе

- •Задания и методические указания к их выполнению

- •Раздел 1. Ввод исходных данных для выполнения операций 1-3.

- •5. Ветвление со сложным условием

- •Подготовка к работе

- •Задания и методические указания к их выполнению

- •6. Ветвление с вложеными условиями

- •Подготовка к работе

- •Задания и методические указания к их выполнению

- •7. Регулярные циклы

- •Подготовка к работе

- •Задания и методические указания к их выполнению

- •8. Итеративные циклы

- •Подготовка к работе

- •Задания и методические указания к их выполнению

4. Ветвление с простым условием

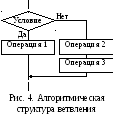

Ветвления позволяют реализовать альтернативные вычисления в зависимости от каких-либо условий. Наиболее просто ветвление организуется для одного условия с одним отношением, например a<b.

Подготовка к работе

1. По указанной выше литературе изучить форматы и особенности выполнения логических и сервисных команд ассемблераTMS320C6x.

2. Выполнить пункты 3 и 4 отчета (см. стр. 3 – 4) в соответствии с первым заданием работы. При этом требования пункта 4 отчета ограничить программой и прогнозами результатов выполнения ее команд.

Задания и методические указания к их выполнению

1. На языке ассемблера TMS320C6x подготовить программу, реализующую ветвление (рис. 4) с одним простым условием. При этом:

– операция 1 заключается в вычислении

абсолютной величины числа, взятого из

табл. 1 работы 2 по номеру варианта V

= 33-N, а операции 2

и 3 – соответственно операциям 1 и 2

работы 3 по номеру варианта V

= 31-N;

операция 1 заключается в вычислении

абсолютной величины числа, взятого из

табл. 1 работы 2 по номеру варианта V

= 33-N, а операции 2

и 3 – соответственно операциям 1 и 2

работы 3 по номеру варианта V

= 31-N;

в реализации условия предусмотреть различные исходные данные, чтобы можно было убедиться в правильной реализации ветвления. Для этого и с целью выполнения только одного прогона программа может иметь следующую структуру:

Раздел 1. Ввод исходных данных для выполнения операций 1-3.

Раздел 2. Ввод в используемые вусловии РОН исходных данных, обеспечивающих выполнение операции 1.

Раздел 3. Реализация операции ветви «Да» рис. 4.

Раздел 4. Ввод в используемые вусловии РОН исходных данных, обеспечивающих выполнение операций 2 и 3.

Раздел 5. Реализация операций ветви «Нет» рис. 4.

условие и способ формирования содержимого регистра условия R (назначить из РОН по своему усмотрению) выбрать из таблицы при V = N:

|

V |

Условие ветвления |

Способ (команда) формирования содержимого регистра условия R |

|

1 |

2 |

3 |

|

1 |

(A8) (A9) |

CMPLTU |

|

2 |

0 в пяти старших разрядах В8 |

Сброс области бит с 0-го по 26-й (CLR) |

|

3 |

(A8) 0 |

SHR |

|

4 |

(В8) четное |

AND |

|

5 |

(A8) < (A9) |

CMPLT |

|

6 |

(B8) = (B9) |

XOR |

|

7 |

(A8) 0 |

EXTU |

|

8 |

0 в пяти старших разрядах В8 |

Сдвиг вправо на 27 разрядов (SHRU) |

|

9 |

(A8) > (A9) |

CMPGTU |

|

10 |

(В8) нечетное |

CLR |

|

11 |

(A8)0 |

CMPGT |

|

12 |

(B8) (B9) |

XOR |

|

13 |

(A8) (A9) |

CMPLT |

|

14 |

0 в пяти старших разрядах В8 |

Выделение области бит с 27-го по 31-й (EXT) |

|

15 |

(A8) 0 |

CLR |

|

16 |

(B8) четное |

SHL |

|

17 |

(A8) (A9) |

CMPLT |

|

|

|

|

|

1 |

2 |

3 |

|

18 |

В пяти старших разрядах В8 хотя бы одна 1 |

Выделение области бит с 27-го по 31-й (EXTU) |

|

19 |

(A8)0 |

EXT |

|

20 |

0 в пяти старших разрядах В8 |

Конъюнкция с числом F8000000h(AND) |

|

21 |

(A8) < (A9) |

CMPLTU |

|

22 |

(В8) нечетное |

EXTU |

|

23 |

(A8)0 |

SHRU |

|

24 |

(B8) = (B9) |

CMPEQ |

|

25 |

(A8) > (A9) |

CMPGT |

|

26 |

1 в пяти старших разрядах В8 |

Сравнение (В8) с числом F7FFFFFFh(CMPLT) |

|

27 |

(A8)0 |

AND |

|

28 |

(B8) четное |

EXT |

|

29 |

(A8) (A9) |

CMPGTU |

|

30 |

(B8) (B9) |

CMPEQ |

где (Z) – содержимое регистра Z.

Алгоритмическая структура, приведенная на рис. 4, используется при программировании на языках высокого уровня. Однако в языке ассемблера, во-первых, возможны только два признака ветвления – содержимое регистра условия Rнулевое (выполняются операции одной ветви) или ненулевое (выполняются операции другой ветви). Для формирования этих признаков требуются дополнительные логические и/или сервисные операции, что должно быть отражено в алгоритмической структуре (рис. 5). При этом для одного и того же исходного условия признаки ветвления могут быть получены разными способами. Например:

1. В случае сравнения с 0 помимо команд сравнения (обсуждаются ниже) можно использовать знак числа (значение 31-го двоичного разряда). Для его выделения пригодны конъюнкция (команда AND) с числом 80000000h, выделение области из одного старшего бита (командаEXTилиEXTU), сдвиг вправо на 31 разряд (командаSHRилиSHRU), обнуление 31 младших разрядов (командаCLR).

2 .Для определения

четности числа можно использовать

его конъюнкцию с числом 00000001h,

выделение области

из одного младшего

бита, сдвиг влево на 31 разряд, обнуление

31 старших разрядов.

.Для определения

четности числа можно использовать

его конъюнкцию с числом 00000001h,

выделение области

из одного младшего

бита, сдвиг влево на 31 разряд, обнуление

31 старших разрядов.

Эта множественность решений отражена в разделе «Способ формирования содержимого регистра условия R» таблицы задания, где для одного и того же условия в зависимости от варианта предлагаются различные команды его реализации.

Во-вторых, команды сравнения реализуют только строгие отношения: а < b,a>bиa=b. Поэтому в случае условийab,abиabследует использовать альтернативные условия –a>b, а <bиa=b, соответственно. При этом признаки выполнения ветвей «Да» и «Нет» блока ветвления меняются местами. Например, некоторая операция должна выполняться, только еслиab(признак «Да»). При использовании условияa>bзаданная операция должна выполняться только в случае его нарушения, то есть признак «Да» заменяется признаком «Нет».

В-третьих, все команды, соответствующие операциям той или иной ветви, должны быть условными. В противном случае команды одной из ветвей будут выполняться всегда, то есть вне зависимости от условия ветвления.

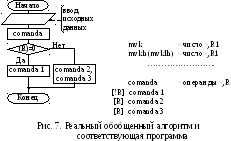

Таким образом, в соответствии с заданием

пример обобщенных алгоритма и

программы (без указания конкретных

чисел,имен регистров РОН, команд

по формированию содержимого регистра

условияR), соответствующ их

операциям 1 – 3, приведен на рис. 6.

их

операциям 1 – 3, приведен на рис. 6.

Однако структуры рис. 6 не предъявляются

к практическому использованию, то есть

с этой точки зрения не являются реальными.

Они удобны лишь для отладки – правильность

реализации ветвления проверяется за

один прогон программы. Если пренебречь

этим удобством, отладку можно выполнить

и на реальных в указанном смысле

структурах (рис. 7). Правда, при этом

потребуется два прог она

программы.

она

программы.

2. Получить исполняемый программный модуль (см. стр. 6 – 7).

3. Загрузить исполняемый модуль в симулятор (см. стр. 8).

4. В пошаговом режиме выполнить прогон программы (см. стр. 9), для каждой командной строки записывая в таблицу отчета соответствующие данные из окна CPU симулятора.

5. Предъявить результаты выполнения работы преподавателю, после чего завершить работу с симулятором (см. стр. 9).