Microsoft Word - лаб раб 1

.pdf

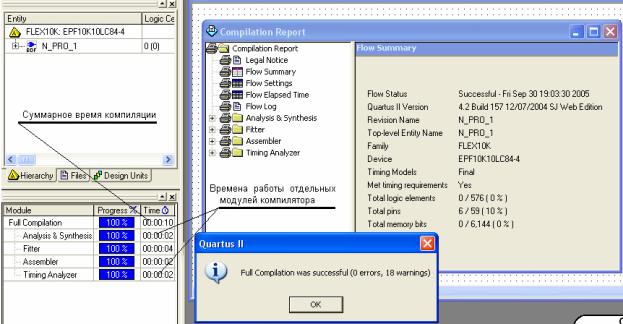

Рисунок 1.16. Окно компилятора

Для завершения процесса компиляции необходимо нажать кнопку «ОК».

Назначение внешних выводов подключения сигналов к ПЛИС

После того, как произведена компиляция проекта следует подключить входные и выходные контакты к внешним выводам ПЛИС. Для этого необходимо выбрать Assignment/Pins. В результате появиться окно (См. рисунок 1.17).

Рисунок 1.17. Окно подключения схемы к внешним выводам

В колонке Node Name располагаются имена входов и выходов ПЛИС. Для назначения номера вывода ПЛИС выбранного входа или выхода, необходимо произвести двойной щелчок указателем мыши в колонке Location напротив соответствующего сигнала, и выбрать номер вывода, к которому необходимо подключить вход (выход) электронной схемы. После назначения всех выводов следует провести повторную компиляцию проекта.

Конфигурирование ПЛИС

Программатор позволяет физически реализовать спроектированное устройство внутри кристалла ПЛИС, как говорят, программировать структуру ПЛИС. С помощью программатора файл конфигурации проекта с расширением .pof, созданный при компиляции, используется для организации соединений между ячейками ПЛИС.

Наиболее простым и доступным разработчикам средством прошивки ПЛИС является загрузочный кабель ByteBlasterMV. Схема электрическая принципиальная и таблица цоколевки разъема кабеля ByteBlasterMV приведена в приложении 2 на рисунке 1.21 и таблице 1.2. На рис. 1.18 показано подключение устройства ByteBlasterMV к LPT порту компьютера. Схема электрическая принципиальная приведена в приложении 2.

Рисунок 1.18. Подключение кабеля ByteBlasterMV к ЭВМ.

Перед конфигурированием ПЛИС необходимо убедиться, что аппаратные средства конфигурирования подключены к отладочной плате к разъему XP1. Питание стенда подключено.

Для начала процесса программирования необходимо открыть окно программатора.

Для этого необходимо «кликнуть» иконку  на панели инструментов или выбрать в меню Tools вкладку Programmer (см. рисунок 1.19).

на панели инструментов или выбрать в меню Tools вкладку Programmer (см. рисунок 1.19).

Рисунок 1.19. Диалоговое окно программатора

Убедиться что в столбце File находиться файл для конфигурирования и установлена метка в поле Program/Configure. Нажать кнопку «Старт» (Start) меню программирования файла***.pof, показанного на рисунке 1.19. О ходе выполнения конфигурирования

можно судить по процентам выполнения, появляющимся в окне «Выполнение конфигурирования» (Progress). После успешного окончания конфигурирования система Quartus II выдаст соответствующее сообщение.

Описание стенда

Все лабораторные работы выполняются на стенде, основой которого является ПЛИС семейства MAX3000A. Принципиальная схема приведена в приложении 3. Стенд подключается к компьютеру через параллельный порт (LPT1) посредством кабеля ByteBlasterMV. Схема электрическая принципиальная кабеля ByteBlasterMV и цоколевка разъема кабеля ByteBlasterMV приведены в приложении 2 (см. рисунок 1.21, 1.22, таблица 1.2). К выводам ПЛИС (D1) подключены 4 двухцветных светодиода (HL1 – HL4) (см. рисунок 1.27), которые могут быть использованы как индикаторы логических уровней в различных точках схемы. Два 7 – сегментных индикатора (HL5, HL6) (см. рисунок 1.28) предназначены для индикации цифр от 0 до 9. К входу общей синхронизации ПЛИС (вывод 87) подключен кварцевый генератор частотой 5 МГц (см. рисунок 1.31). Элемент SA1SA4 представляет собой одиночную кнопку (см рисунок 1.29), формирующую, благодаря резисторам R29-R32, два логических уровня (0 и 1). Сборка микропереключателей SB5 (см. рисунок 1.25) предназначена для формирования логических уровней на выводах ПЛИС. Микросхема DA1 – стабилизатор напряжения питания платы (см рисунок 1.30). Выводы конфигурирования ПЛИС выводятся на контакты разъема (XP1) (см. рисунок 1.26), который служит для смены конфигурационного файла ПЛИС с помощью персонального компьютера и согласующего кабеля ByteBlasterMV.

Расположение описанных компонентов можно проследить по сборочному чертежу, приведенному на рисунке 1.20.

Рисунок 1.20. Сборочный чертеж платы лабораторного стенда

Задание для самостоятельного выполнения

Внимание!

При выполнении практикума в лабораторном классе:

Соблюдайте правила техники безопасности при работе со стендом и приборами как с электрическими установками! Сетевое питание на стенд и питание на тестируемые схемы подавайте только после полного монтажа схемы и проверки монтажа преподавателем!

Загрузите проект, из предложенных преподавателем, в среду Quartus II. Как видно из окна графического редактора, схема состоит из двух логических элементов: логических элемент «И» на два входа, а также логический элемент «ИЛИ» на два входных сигнала.

Входы логических элементов подключены (см. схему электрическую принципиальную, приложение 3) к сборке микропереключателей SB5, два выхода к светодиодам

HL1 и HL2.

Пользуясь редактором временных диаграмм, заполните таблицу истинности 1.1 представленных элементов.

IN 0 |

IN1 |

OUT |

0 |

0 |

? |

0 |

1 |

? |

1 |

0 |

? |

1 |

1 |

? |

Таблица 1.1. Таблица истинности логических элементов (заполняется при выполнении лабораторной работы)

Сконфигурируйте ПЛИС, предложенным файлом и проведите исследование логических элементов. Для этого с помощью младших (левых) двух микропереключателей в сборке SB5 последовательно устанавливайте возможные комбинации уровней на входах элемента «И», контролируя состояние выхода последнего с помощью светодиода HL1. Повторно заполните таблицу истинности 1.1. Проведите аналогичное исследование для элемента «ИЛИ», используя для управления логическими входами элемента, старшие два микропереключателя (правые) из сборки SB5 и для контроля выхода светодиод HL2. Данные занесите в таблицу истинности 1.1.

Сравните по заполненным таблицам истинности результаты моделирования и практического исследования. Оформите отчет выполненной лабораторной работы.

5. Контрольные вопросы

Расскажите что такое ПЛИС.

Что такое файл конфигурации ПЛИС?

Каким образом производиться конфигурирование ПЛИС? Расскажите как устроен лабораторный стенд.

Что такое таблица истинности?

Приложение 1.

Таблица соответствия обозначений логических элементов

Название элемента

«И»

«И-НЕ»

«ИЛИ»

«ИЛИ-НЕ»

«ИСКЛЮЧАЮЩЕЕ ИЛИ»

«ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ»

Российское обозначе- ние

Название эле-

мента в Обозначение в Quartus

Quartus

and

nand

or

nor

xor

xnor

«НЕ» |

|

not |

|

|

|

Приложение 2

Схема электрическая принципиальная кабеля ByteBlasterMV

Рисунок 1.21. Принципиальная электрическая схема кабеля BateBlaster II

10-контактный разъём загрузочного кабеля показан на рисунке 1.22

Рисунок 1.22. Разъем загрузочного кабеля

Обозначение и назначение контактов разъема загрузочного кабеля для различных режимов конфигурирования приведены в таблице 1.2.

Контакт |

|

Сигналы |

|

||

|

|

||||

|

PS-режим |

JTAG-режим |

|||

|

|

||||

|

Обозначение |

Описание |

Обозначение |

Описание |

|

1 |

DCLK |

Тактовый сигнал |

TCK |

Тактовый сигнал |

|

2 |

GND |

Земля |

GND |

Земля |

|

|

|

|

|

|

|

3 |

CONF_DONE |

Контроль состояния |

TDO |

Выход данных |

|

|

|

конфигурации |

|

|

|

4 |

VCC |

Напряжение питания |

VCC |

Напряжение питания |

|

5 |

nCONFIG |

Контроль состояния |

TMS |

Управление конечным ав- |

|

конфигурации |

томатом JTAG |

||||

|

|

|

|||

6 |

- |

Не используется |

- |

Не используется |

|

7 |

nSTATUS |

Состояние конфигура- |

- |

Не используется |

|

ции |

|||||

|

|

|

|

||

8 |

- |

Не используется |

- |

Не используется |

|

9 |

DATA0 |

Вход данных |

TDI |

Вход данных |

|

|

|

|

|

|

|

10 |

GND |

Земля |

GND |

Земля |

|

|

Таблица 1.2. Цоколевка и назначение контактов кабеля BateBlaster II |

||||

Приложение 3

Схема электрическая принципиальная лабораторного стенда

Рисунок 1.23. Подключение питающего напряжения к ПЛИС

Рисунок 1.24. Подключение контрольных точек к ПЛИС