- •Исследование процессов ввода/вывода информации и системы команд микропроцессоров семесйства intel 80×i86

- •Введение

- •1.Цель работ

- •2.1. Архитектура микропроцессора Intel 8086.

- •2.2. Адресация памяти и данных.

- •2.3. Синтаксис операндов языка assembler

- •2.4. Команды передачи данных.

- •Mov ax,segment

- •3) Mov [bx],dx переслать (dx) в ячейку адресованную (вх)

- •Mov al,es:[si]; ds заменен на es

- •Команды lea, lds, les.

- •Lea reg, memr

- •Команда xchg

- •Стековые команды push и рор

- •2.5 Префикс программного сегмента (psp)

- •2.6 Арифметические команды

- •Команды сложения и вычитания

- •0015 65А0

- •0037 1D3e

- •0004 В837

- •0001 F0f8

- •Команды расширения знака.

- •Команды inc, dec, neg, cmp.

- •Команды двоичного умножения и деления.

- •Дополнительные сведения.

- •2.7 Основные правила при разработке программ на языке assembler.

- •Int 21h

- •Int 21h

- •Int 21h

- •Int 21h

- •Int 21h

- •Int 21h

- •Int 21h

- •3. Лабораторные работы

- •Контрольные вопросы

- •Лабораторная работа № 2

- •Контрольные вопросы

- •Лабораторная работа № 3

- •Дополнительная информация для составления программы по данному заданию.

- •Лабораторная работа № 4

- •Контрольные вопросы

- •Лабораторная работа № 5

- •Контрольные вопросы

- •Лабораторная работа № 6

- •Контрольные вопросы

- •Лабораторная работа № 7

- •Рекомендации по выполнению лабораторной работы.

- •4.1. Тексты подпрограмм вывода на экран.

- •Int 21h

- •Int 21h

- •Контрольные вопросы

- •Лабораторная работа № 8

- •Контрольные вопросы

- •Лабораторная работа № 9

- •Контрольные вопросы

- •Лабораторная работа № 10

- •Контрольные вопросы

- •Контрольные вопросы

- •Лабораторная работа № 14

- •Контрольные вопросы

- •6. Требования к отчетам

- •7. Библиографический список

2.2. Адресация памяти и данных.

Хотя все регистры данных, указателей и сегментов 16-разрядные, на шину адреса вызывается и используется при обращениях к оперативной памяти (ОП) 20-разрядные исполнительные (физические) адреса, позволяющие обращаться к ОП емкостью 1 Мбайт. Это становится возможным благодаря механизму сегментации памяти. В адресуемом пространстве выделяются сегменты, содержащие по 64 Кбайта. Допускаются перекрытия сегментов. Базовые (начальные) 16-разрядные адреса сегментов, хранятся в соответствующих сегментных регистрах, трактуются как 20-разрядные с нулями в четырех младших разрядах.

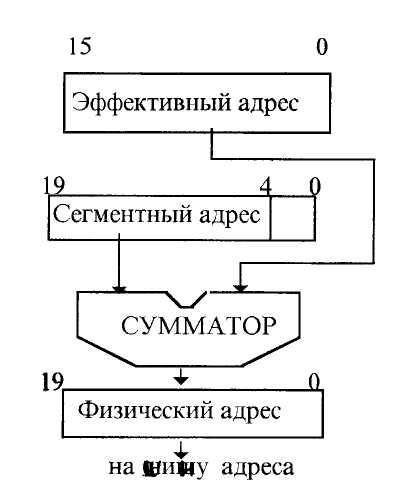

Физический адрес операнда или команды формируется, как показано на рис.3, суммированием содержимого сегментного регистра (СS), сдвинутого на четыре разряда влево и дополненного нулями, и так называемого эффективного адреса (смещения) ЕА, формируемого командой на основе содержащейся в ней информации о способе формирования этого адреса.

Рис.3. Схема формирования физического адреса

Если, например, (СS)=123А и (ЕА)=341В, то следующая команда будет выбрана по физическому адресу 157ВВ:

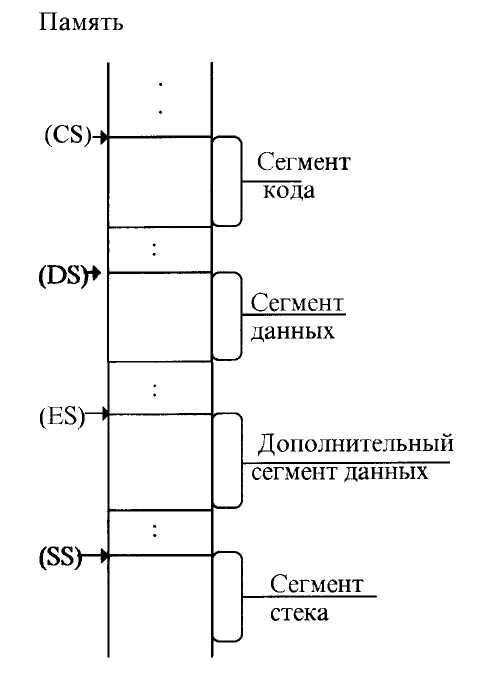

На рис.4 показано, каким образом можно распределить в памяти программный код, данные и стек.

Рис. 4. Распределение памяти под программный код и данные

Рассмотрим наиболее типичные режимы адресации микропроцессора ВМ86. Они разделяются на два класса - режимы адресации данных и режимы адресации переходов.

Адресация данных при использовании языка ASSEMBLER может быть выполнена несколькими способами.

1) Непосредственная. Данное длинной 8 или 16 бит являются частью команды.

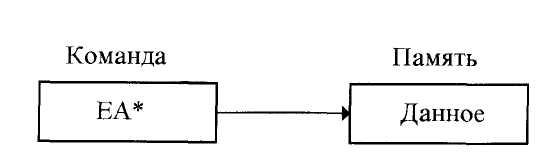

2) Прямая. Шестнадцатибитный эффективный адрес (смещение относительно сегментного адреса области данных) является частью команды.

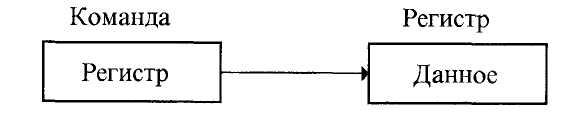

3) Регистровая. Данное содержится в определенном командой регистре.

16-битный операнд может находиться в регистрах АХ, ВХ. СХ, DX. SI, DI, SP, ВР; 8-битный операнд в регистрах AL, АН, BL, BH, CL, CH, DL, DH.

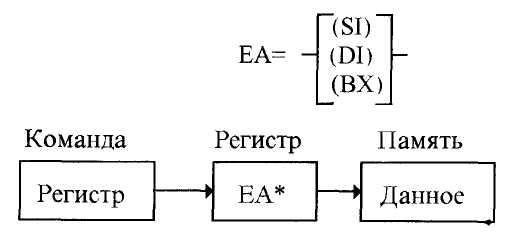

4) Регистровая косвенная. Эффективный адрес данного находится в базовом регистре ВХ или индексном регистре, определенном командой.

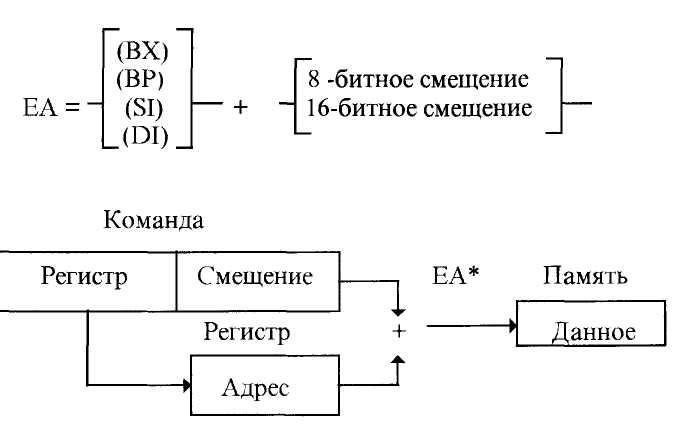

5) Регистровая относительная. Эффективный адрес равен сумме 8 или 16-битового смещения и содержимого базового или индексного регистров.

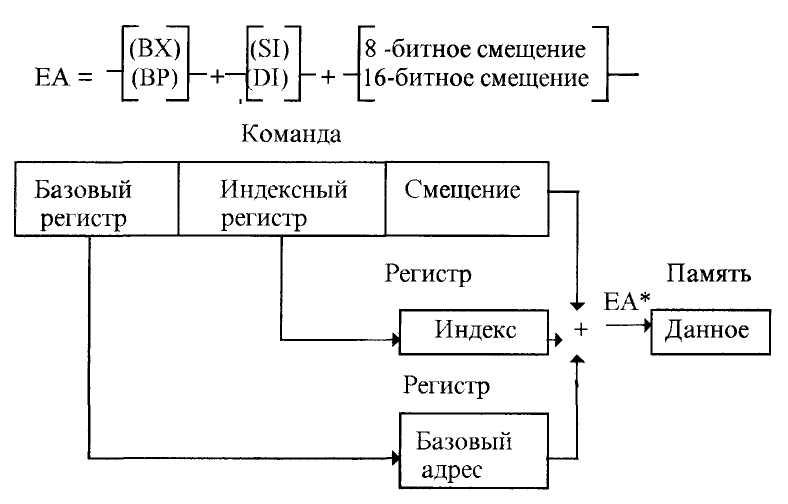

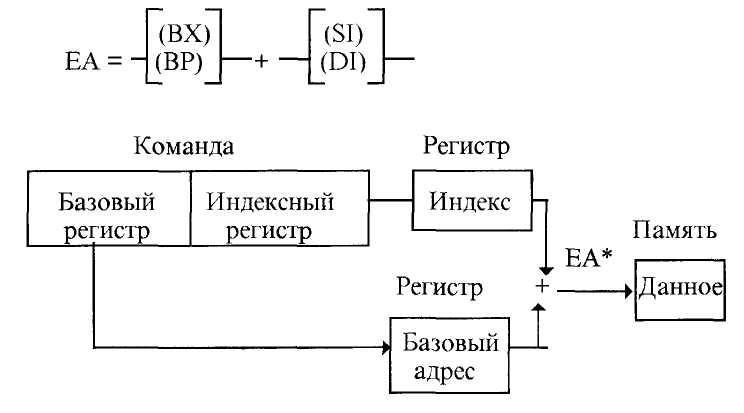

6) Базовая индексная. Эффективный адрес равен сумме содержимого базового и индексного регистров определенных командой.

7) Относительная базовая индексная. Эффективный адрес равен сумме 8 или 16-битового смещения и содержимого базового и индексного регистров.

Отметим, что найденное ЕА в пунктах 2), 4), 5), 6). 7) суммируется с умноженным на 16 содержимым соответствующего сегментного регистра.

Рассмотрим пример. Предположим, что (ВХ)=0158, (DI)=10A5, смещение=1В57, (DS)=2100 и что в качестве сегментного регистра применяется DS. Тогда рассмотренные способы адресации дают следующие эффективные и физические адреса: Прямой: ЕА=1В57

Физический адрес=1В57+21000=22В57.

Регистровый:

ЕА нет- данное в указанном регистре.

Регистровый косвенный (с участием регистра ВХ):

ЕА=0158, физический адрес=0158+21000=21158.

Регистровый относительный (с участием регистра ВХ):

EA=O158+1B57=1CAF, физический адреса 1CAF+21OOO=22CAF.

Базовый индексный (с участием регистров ВХ и DI):

EA=O158+1OA5=11FD, физический адрес=11FD+21000=221FD.

Относительный базовый индексный (с участием регистров ВХ и DI):

EA=0158+10A5+lB57=2D54, физический aдрес=2D54+21000=23D54.

Отметим также, что способ формирования физического адреса зависит от типа данных, к которым обращается процессор во время работы. Правила формирования адреса ячейки памяти приведены в таблице 1.

Таблица 1

-

Тип операции

Сегмент памяти

Индексный регистр

Альтернативный сегментный регистр

Выборка

Команды

CS

IP

нет

Стековая операция

SS

SP

нет

Обращение к переменной

DS

ЕА

CS, SS, ES

Цепочка источник

DS

SI

CS, SS, ES

Цепочка приемник

ES

DI

нет

ВР как базовый регистр

SS

ЕА

CS, SS, ES