- •Исследование процессов ввода/вывода информации и системы команд микропроцессоров семесйства intel 80×i86

- •Введение

- •1.Цель работ

- •2.1. Архитектура микропроцессора Intel 8086.

- •2.2. Адресация памяти и данных.

- •2.3. Синтаксис операндов языка assembler

- •2.4. Команды передачи данных.

- •Mov ax,segment

- •3) Mov [bx],dx переслать (dx) в ячейку адресованную (вх)

- •Mov al,es:[si]; ds заменен на es

- •Команды lea, lds, les.

- •Lea reg, memr

- •Команда xchg

- •Стековые команды push и рор

- •2.5 Префикс программного сегмента (psp)

- •2.6 Арифметические команды

- •Команды сложения и вычитания

- •0015 65А0

- •0037 1D3e

- •0004 В837

- •0001 F0f8

- •Команды расширения знака.

- •Команды inc, dec, neg, cmp.

- •Команды двоичного умножения и деления.

- •Дополнительные сведения.

- •2.7 Основные правила при разработке программ на языке assembler.

- •Int 21h

- •Int 21h

- •Int 21h

- •Int 21h

- •Int 21h

- •Int 21h

- •Int 21h

- •3. Лабораторные работы

- •Контрольные вопросы

- •Лабораторная работа № 2

- •Контрольные вопросы

- •Лабораторная работа № 3

- •Дополнительная информация для составления программы по данному заданию.

- •Лабораторная работа № 4

- •Контрольные вопросы

- •Лабораторная работа № 5

- •Контрольные вопросы

- •Лабораторная работа № 6

- •Контрольные вопросы

- •Лабораторная работа № 7

- •Рекомендации по выполнению лабораторной работы.

- •4.1. Тексты подпрограмм вывода на экран.

- •Int 21h

- •Int 21h

- •Контрольные вопросы

- •Лабораторная работа № 8

- •Контрольные вопросы

- •Лабораторная работа № 9

- •Контрольные вопросы

- •Лабораторная работа № 10

- •Контрольные вопросы

- •Контрольные вопросы

- •Лабораторная работа № 14

- •Контрольные вопросы

- •6. Требования к отчетам

- •7. Библиографический список

1.Цель работ

Целью данных лабораторных работ является изучение процессов ввода/вывода информации в (из) память ЭВМ с использованием стандартных устройств (клавиатуры и экрана монитора), а также исследование системы команд микропроцессоров семейства Intel 80×i86 и Pentium и разработка программ на языке ASSEMBLER.

2. ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

2.1. Архитектура микропроцессора Intel 8086.

На основе n-МОП технологии с кремниевыми затворами фирмой Intel был создан однокристальный 16-разрядный МП 8086 (отечественный аналог - МП КМ1810ВМ86). Производительность этого микропроцессора при тактовой частоте 5 МГц составляет 2,5 миллиона операций типа регистр-регистр в секунду. В дальнейшем будем называть его ВМ86. Отметим, что архитектура этого микропроцессора легла в основу разработки последующих поколений микропроцессоров, выпускаемых фирмами Intel, AMD и т. д. Поэтому изучение микропроцессорных средств персональных ЭВМ, а также основ разработки программ для них на языке ASSEMBLER, целесообразно начинать с изучения архитектуры ВМ86, системы его команд и способов адресации. Важно отметить, что программы написанные под эту архитектуру, прекрасно работают и на современных персональных ЭВМ, использующих микропроцессоры отмеченных выше фирм.

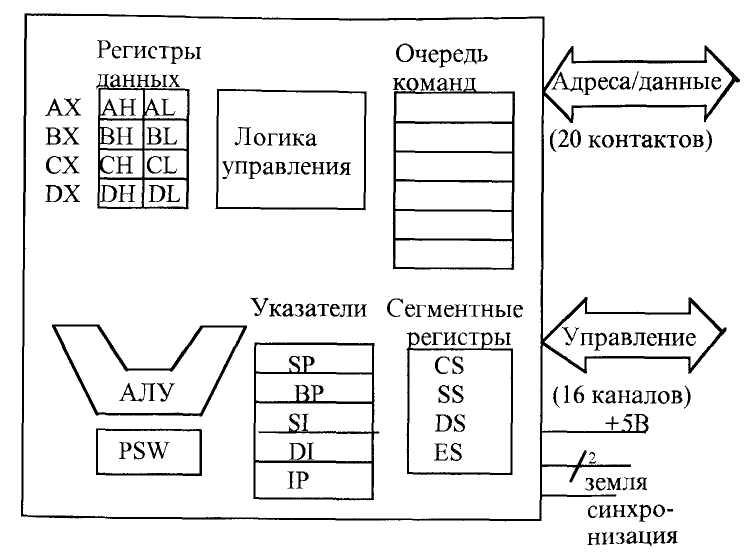

Архитектура ВМ86 имеет следующие особенности: выполнение аппаратными средствами арифметических операций над 8 и 16-разрядными двоичными числами со знаком и без знака, десятичными двоично-кодированными числами, логические операции над цепочками данных, расширенные возможности работы с отдельными разрядами слов; наличие 16-разрядного АЛУ с аппаратной реализацией умножения и деления; регистровая структура; практически неограниченное число уровней векторного прерывания; сегментная адресация, позволяющая прямо адресовать одно-мегабайтовую память, производить динамическое перемещение программ; использование одного уровня напряжения питания 5В. На рис.1 представлена архитектура центрального процессора ВМ86.

Регистры управления и рабочие регистры разделены на три группы в соответствии с выполняемыми ими функциями. Имеются группа регистров данных, указательная группа и сегментная группа. Все регистры имеют длину 16 бит. Регистром команд служит 6- байтная очередь. В группу регистров данных входят регистры АХ, ВХ, СХ и DX. Они предназначены для хранения операндов и результатов операций и допускают адресацию не только целых регистров, но и их младшей L и старшей Н половин.

Рис. 1. Архитектура центрального процессора ВМ86.

Регистры ВХ, СХ и DX кроме арифметических функций имеют и специальные назначения: ВХ служит базовым регистром в вычислениях адреса, СХ в некоторых командах выступает неявным счетчиком, DX в некоторых операциях ввода-вывода содержит адрес порта ввода-вывода.

Указательная и индексная группы представлены регистрами IP, SP, BP, SI и DI. Указатель команды IP и регистр SP фактически являются программным счетчиком и указателем стека. Однако полные адреса команды и стека образуются суммированием содержимого этих регистров и регистров CS и SS. Регистр ВР является базовым при обращении к стеку. Регистры SI и DI предназначены для индексирования. Хотя их можно использовать сами по себе, они часто используются в комбинации с регистрами ВХ, ВР и (или) смещением. Любой из указателей, кроме IP, может хранить 16- разрядный операнд.

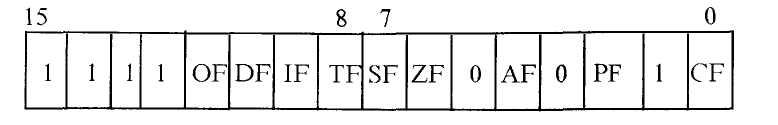

Регистр признаков - Flag (F), приведенный на рис. 2, имеет 16 разрядов.

Рис.2. Формат регистра флагов

В регистре признаков формируются:

а) признаки результата: переполнение OF (операции с целыми числами); знака результата SF; нуля ZF; вспомогательного переноса AF (перенос из третьего или заем из четвертого разряда); четности PF (четное число единиц в младшем байте результата); переноса CF (перенос из старшего или заем в старший разряд результата;

б) признаки управления: пошагового режима TF (управление пошаговыми прерываниями); разрешения прерывания IF (разрешение или запрещение направления DF (указывает направление обработки цепочки данных, начиная с элемента с наименьшим адресом при DF= 0 или с наибольшим адресом при DF = 1)), где:

OF - флажок переполнения;

DF - флажок направления сканирования;

IF - флажок разрешения прерывания;

TF - флажок пошагового режима;

SF - флажок знака;

ZF - флажок нуля;

AF - флажок вспомогательного переноса;

PF - флажок четности;

CF - флажок переноса.

Память имеет байтовую организацию - двухбайтовое слово размещается в смежных ячейках, причем старший байт занимает ячейку с большим номером. Адресом слова служит адрес младшего байта. Рекомендуется, для повышения скорости обработки данных, размещать слова по четным адресам.