SRS_Expedition_PCB

.pdfимпортируется в рабочий проект командой File >> Import >> IDF... и автоматически отрабатывается редактором Expedition PCB.

4. Обзор основных возможностей редактора Expedition PCB по трассировке критических (в т.ч. высокочастотных) цепей.

Схемотехнический редактор DxDesigner и топологический редактор Expedition PCB системно интегрированы с программами анализа и моделирования HyperLynx, ICX и Quiet Expert, входящими в состав маршрута Expedition Enterprise и предназначенными для проверки целостности цепей, расчета временных характеристик и анализа электромагнитной совместимости. Их использование позволяет контролировать поведение критических сигналов (на этапе создания электрической схемы – для выработки рекомендаций по согласованию линии, по результатам трассировки - для возможной корректировки с учетом реального прохождения трассы и влияния на нее соседних проводников). Предусмотрена возможность работы с логической цепью. Логическая цепь представляет полный путь от источника сигнала до приемника и включает в себя все последовательные физические цепи и встроенные элементы согласования (резисторы, индуктивности и т.п.). Моделирование требует подключения к библиотечным элементам поведенческих SPICE- и IBIS-моделей.

Кроме того, в редакторе CES имеются встроенные возможности для прямого задания отдельных параметров критических цепей. Перечень основных из них приводится ниже :

1.Задание структуры платы (Layer Stackup):

-количество и расположение сигнальных и экранных слоев;

-толщины и электрические характеристики металлизации (объемное сопротивление);

-толщины и электрические характеристики диэлектриков (диэлектрическая проницаемость, тангенс угла потерь);

81

-расчет волнового сопротивления цепи или дифференциальной пары в зависимости от параметров проводника (ширины, зазоров) и наоборот, расчет параметров проводника или дифференциальной пары для заданного волнового сопротивления. При этом учитывается положение проводника в объеме платы (полосковая линия для внутренних слоев между экранами, микрополосковая - для внешних слоев).

2.Выделение критических цепей в отдельные классы (Net Classes).

3.Расчет ширины проводников в зависимости от волнового сопротивления и назначение ее для цепей (классов цепей).

4.Расчет и назначение зазоров между цепями, между классами цепей, а также внутри классов цепей.

5.Назначение максимального количества переходных отверстий цепи (Max Vias) при ее трассировке.

6.Назначение длины максимального ветвления цепи (Max Stab Length).

7.Назначение номиналов для цепей питания (Supply Voltage).

Цепи питания не рассматриваются как цепи-агрессоры при подсчете допустимых наводок (см. п.13).

Данные номиналов питания используются в программах моделирования.

8. Возможность назначения порядка трассирования выводов цепи (Net Order).

Предлагается набор готовых шаблонов (“цепочка”, “звезда”, Т-образный и т.д. или определяемый пользователем).

Шаблон можно настраивать для всей цепи или для ее частей. Допускается ветвление цепи.

Допускается назначать разрешенные для трассировки слои.

9. Задание максимальной (Max Length) и минимальной длины цепи.

Длина задается (один из вариантов): - в мм/дюймах; - в виде задержки сигнала (наносек.); - в процентах от кратчайшего расстояния между выводами (pins).

82

Трассировщик при необходимости зигзагообразно удлиняет проводник (Tuning). Для повышения точности согласования имеется параметр, определяющий внутреннюю длину от вывода корпуса до кристалла (по данным изготовителя микросхемы).

10.Задание одинаковой (согласованной) длины/задержки сигнала для группы цепей в пределах указанного допуска (Matched Length).

Трассировщик, ориентируясь на наиболее длинную трассу группы, зигзагообразно увеличивает длины остальных (Tuning).

Допускается указывать максимальную и минимальную длину для каждой группы цепей.

11.Задание для отдельной цепи допустимых длин/задержек сигнала между выводами

(Delay Formulas).

Допустимые длины/задержки сигнала между выводами задаются в явном (числовом) виде или относительном (с помощью формул).

12. Задание дифференциальных пар (Diff Pairs).

Дифференциальная пара может формироваться на одном слое или в смежных слоях (друг под другом).

Допускается указывать максимальную и минимальную длину дифференциальной пары (как в п.9) и задавать одинаковую (согласованную) длину для группы дифференциальных пар (как в п.10).

13. Ограничение допустимых наводок.

Задается величиной максимальной перекрестной помехи (Max Crosstalk) или допустимой параллельной длиной соседних проводников (Parallelism). Одновременное назначение обоих требований не допускается.

83

Max Crosstalk (V или mV) зависит от длины соседних проводников, их зазоров с критичной цепью и технологии примененных элементов (Tech) (например, TTL, CMOS и т.п.).

Tech выбирается из перечня прилагаемых типовых технологий или задается в виде новой технологии двумя параметрами: длиной переднего фронта цепиагрессора (Rise Time, наносек.) и перепадом напряжения цепи-агрессора (Voltage Swing, V). В случае нескольких приложенных источников выбирается меньший

Rise Time и больший Voltage Swing.

Превышение заданной величины Max Crosstalk не является ограничением трассировки, но отслеживается средствами проверки в процессе (OnLine) и по окончании (DRC) разводки. Нарушения устраняются в интерактивном режиме увеличением зазоров или уменьшением длины соседних трасс.

Parallelism определяется правилами в виде таблицы, включающей допустимую параллельную длину соседних проводников в зависимости от зазоров между ними. Правила задаются как в пределах одного слоя, так и для смежных слоев.

14. Задание дополнительных конструктивных требований.

Экранирование цепей или групп цепей в пределах слоя или между смежными слоями.

Скругление дугами с заданным радиусом острых и прямых углов оттрассированных проводников (Modify Corners).

Формирование каплевидного подхода проводников к контактным площадкам для уменьшения отражения сигналов (Teardrops).

5.FabLink XE. Панелизация печатных плат.

5.1.Назначение программы.

Программа FabLink XE используется на этапе подготовки производства и предназначена для объединения на общей панели нескольких печатных плат.

84

Допускается сочетание плат различных проектов. Необходимость многоплатных панелей обусловлена, по крайней мере, двумя факторами:

-использованием методов полуавтоматического или автоматического монтажа элементов при средне- и крупносерийном производстве;

-экономией при подготовке производства (за счет стоимости фотошаблонов) путем совмещения на одной панели различных печатных плат при штучном или мелкосерийном производстве.

Групповой монтаж элементов поверхностного монтажа с использованием метода оплавления (Reflow) заключается в:

-предварительном нанесении на контактные площадки паяльной пасты через специальный трафарет;

-автоматической или полуавтоматической установке элементов на плату, подклейке их, при необходимости;

-прохождении платы через конвекционную печь, имеющую зоны, в которых в соответствии с заданным профилем температура плавно, по нарастающей, достигает температуры плавления припоя, а затем, по ниспадающей, остывает до комнатной.

Для печатных плат малых габаритов применение панелей существенно повышает производительность труда за счет сокращения времени на совмещение трафарета с контактными площадками платы и времени нанесения паяльной пасты.

5.2. Типы многоплатных панелей.

Существует три основных типа панелей:

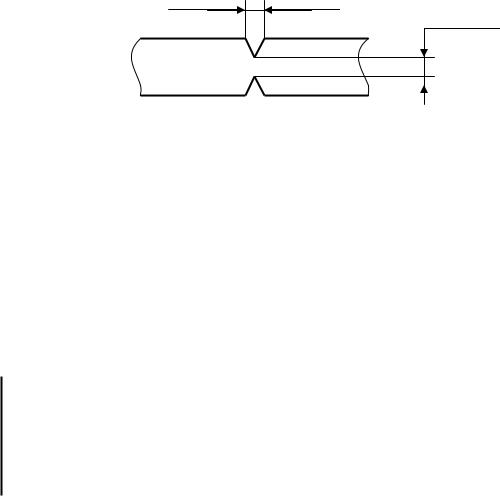

-панели с V-cut надрезами для последующего скрайбирования (разламывания) на отдельные платы. Геометрия надрезов приведена на рис. 5.1 и получается одновременным прохождением над и под панелью дисковых фрез;

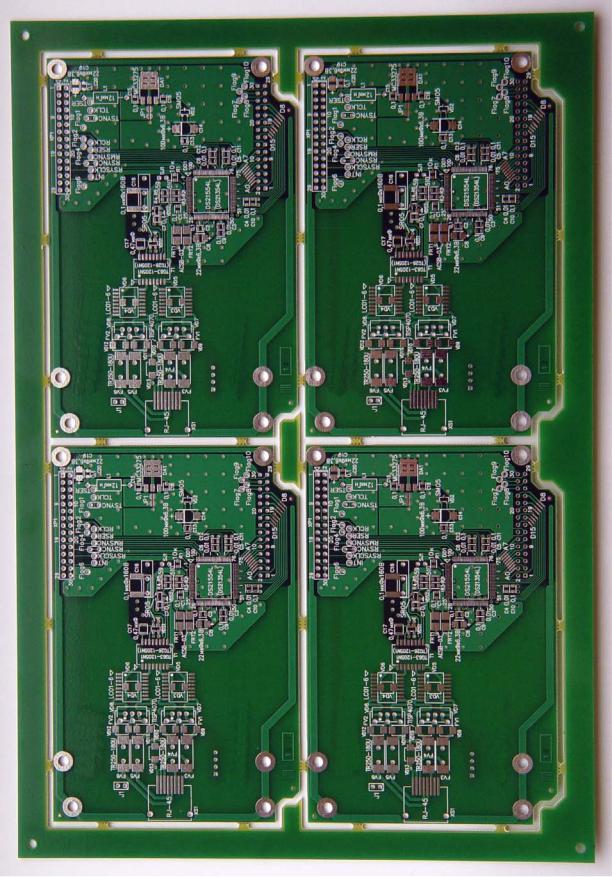

-панели с фрезерованными вырезами и удерживающими перегородками (см. рис. 5.2), при этом используются торцевые фрезы диаметром 1,5...2,5 мм. Платы после монтажа элементов разламываются;

85

-панели комбинированные, сочетающие и выгодно использующие преимущества двух предыдущих типов.

0,4...0,5

0,4...0,5

Рис. 5.1. Геометрия V-cut надрезов под скрайбирование на многоплатных панелях.

Панели с V-cut надрезами более компактны (зазор между платами практически близок к нулевому), но применимы только к прямоугольным платам, к тому же они иногда имеют острые режущие края (зависит от культуры производства).

Панели с фрезерованными вырезами применимы к печатным платам любой конфигурации, имеют гладкие края (кроме мест разлома), но требуют большей площади панели и соответственно удорожают стоимость.

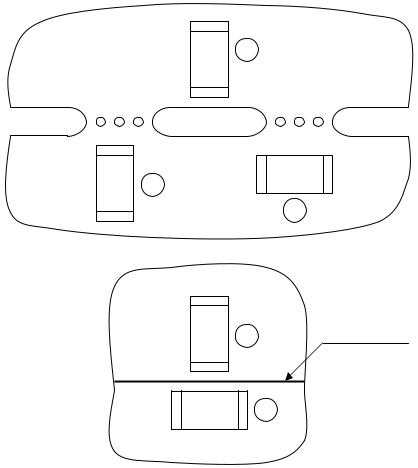

При проектировании печатной платы с учетом последующей панелизации для элементов, расположенных близко к местам разламывания (или скрайбирования), необходимо предусматривать одинаковое силовое воздействие на все их выводы

вмомент разъединения плат (см. рис. 5.3).

5.3.Трафареты для нанесения паяльной пасты.

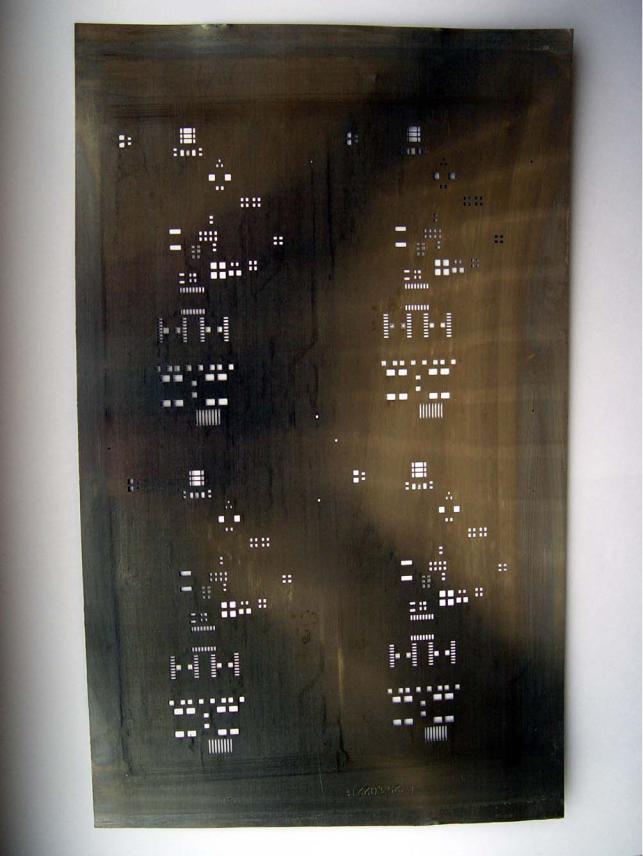

Трафареты для нанесения паяльной пасты, как правило, изготавливаются из тонких металлических листов толщиной 0,12 мм или 0,15 мм. Исходными материалами служат нержавеющая сталь или бериллиевая бронза. Пример трафарета для нанесения паяльной пасты приведен на рис. 5.4.

Трафареты из нержавеющей стали применяются для изделий с высокой плотностью монтажа, имеющих микросхемы с малым шагом выводов (0,5 мм и менее) и ориентированных на средне- и крупносерийное производство.

86

Рис. 5.2. Многоплатная панель с фрезерованными вырезами.

87

+

–

+

– |

V-cut линия |

+

Рис. 5.3. Правильное (+) и неправильное (–) размещение элементов при панелизации.

Высокая точность отверстий произвольной конфигурации, получаемых прожиганием лучом лазера, повышенная износостойкость и другие преимущества таких трафаретов позволяют добиться оптимальной дозировки паяльной пасты и достичь высокого качества трафаретной печати в сочетании с долгим сроком службы и повторяемостью процесса в течение всего этого времени. При определении стоимости таких трафаретов обычно оценивается суммарное количество отверстий.

Для снижения стоимости трафаретов из нержавеющей стали иногда используется комбинированная технология изготовления, когда часть отверстий получается вырезанием лазерным лучом, а оставшаяся - методом двустороннего химического травления.

88

Рис. 5.4. Трафарет для нанесения паяльной пасты.

89

Трафареты из бериллиевой бронзы применяются для изготовления небольших партий изделий с невысокой плотностью монтажа, на которых отсутствуют микросхемы с малым шагом выводов (0,5 мм и менее). Отверстия получаются методом двустороннего химического травления, они могут иметь произвольную конфигурацию, но относительно невысокую точность соблюдения размеров. Достоинством данных трафаретов является их низкая стоимость, которая не зависит от требуемого количества отверстий.

5.4. Работа с программой FabLink XE.

Программа FabLink XE проста в освоении и содержит практически тот же интерфейс, что и программа Expedition PCB. Для их совместной работы требуется подключить соответствующую лицензию (Expedition PCB: команда основного меню

Setup >> Licensed Modules >> Acquire FabLink XE).

Основные возможности программы FabLink XE:

-использование типовых панелей для унифицированных по габаритам печатных плат;

-возможность создания индивидуальных панелей;

-простота размещения плат на панели (задается указанием строк / столбцов матрицы и шагом смещения по осям Х / Y, а также необходимостью централизации матрицы относительно панели);

-возможность компоновки на одной панели различных печатных плат;

-повороты (на 90° и 180°), смещение и зеркальное отражение плат на панели;

-размещение на панели сопроводительного текста, технологических отверстий, реперных знаков совмещения (Fiducial), тестовых структур (например, для контроля волнового сопротивления) и т.д.;

-заполнение свободной площади панели медной поверхностью (Cupper Balancing) для устранения возможного прогиба ее при температурном воздействии в конвекционной печи и для повышения точности параметров печатного рисунка при травлении;

90