- •Глава 6

- •Устройства управления

- •Кодирование микрокоманд

- •Обеспечение последовательности выполнение микрокоманд

- •Адресация микрокоманд

- •Организация памяти микропрограмм

- •Запоминающие устройства микропрограмм

- •Минимизация количества слов памяти микропрограмм

- •Минимизация разрядности микрокоманды

- •Пути повышения быстродействия автоматов микропрограммного управления

- •Контрольные вопросы

Глава 6

Устройства управления

Данная глава освещает различные аспекты структурной организации и функционирования устройства управления вычислительной машины.

Функции центрального устройства управления

Устройство управления (УУ) вычислительной машины реализует функции управления ходом вычислительного процесса, обеспечивая автоматическое выполнение команд программы. Процесс выполнения программы в ВМ представляет собой последовательность машинных циклов. Детализируем основные целевые функции, реализуемые устройством управления в ходе типового машинного цикла [25]. Для простоты примем, что ВМ обеспечивает одноадресную систему команд. При этом, в частности, полагается, что до начала выполнения двухоперандной арифметической команды второй операнд уже находится в процессоре.

Первым этапом в машинном цикле является выборка команды из памяти (этап ВК). Целевую функцию этого этапа будем обозначать как ЦФ - ВК.

За выборкой команды следует этап декодирования ее операционной части (кода операции). Для простоты пока будем рассматривать этот этап в качестве составной части этапа ВК.

Вторая целевая функция — формирование адреса следующей команды. На это выделяется специальный такт работы — этап ФАСК, которому соответствует целевая функция ЦФ-ФАСК.

Далее следует этап формирования исполнительного адреса операнда или адреса перехода, (этап ФИА), на котором УУ реализует функцию ЦФ-ФИА. Функция имеет столько модификации, сколько способов адресации (СА) предусмотрено в системе команд ВМ.

На четвертом этапе реализуется целевая функция выборки операнда (ЦФ-ВО) из памяти по исполнительному адресу, сформированному на предыдущем этапе.

Наконец на последнем этапе машинного цикла действия задаются целевой функцией исполнения операции - ЦФ-ИО. Очевидно, что количество модификаций ЦФ-ИО равно количеству операций, имеющихся в системе команд ВМ.

294

Порядок следования целевых функций полностью определяет динамику работы устройства управления и всей ВМ в целом. Этот порядок удобно задавать и отражать в виде граф-схемы этапов исполнения команды (ГСЭ). Как и гpaф- микропрограммы, 1СЭ содержит начальную, конечную, операторные и условные вершины. В начальной и конечной вершинах проставляется условное обозначение конкретной команды, а в условной вершине записывается логическое условие, влияющее на порядок следования этапов. В операторные вершины вписываются операторы этапов.

По форме записи оператор этапа — это оператор присваивания, в котором:

* слева от знака присваивания указывается наименование результата действий выполненных на этапе;

* справа от знака присваивания записывается идентификатор целевой функции определяющей текущие действия, а за ним (в скобках) приводится список исходных данных этапа.

Исходной информацией для первого этапа служит хранящийся в счетчике команд адрес AKj текущей команды К(. Процесс выборки команды отображается оператором первого этапа: К, := BK(AKi).

Адрес AKj обеспечивает также второй этап, результатом которого является адрес следующей команды AKi+1, поэтому оператор второго этапа имеет вид: Акы := ФАСК(АК,). В качестве исходных данных для третьего этапа машинного цикла выступают содержащиеся в коде текущей команды способ адресации CAS (он определяет конкретную модификацию ЦФ-ФИАО) и код адресной части А,. Результатом становится исполнительный адрес операнда Аисп := ФИА(САi, Ai).

Полученный

адрес используется на четвертом этапе

для выборки операнда

![]()

Результат

исполнения операции Р0i,

получаемый на пятом этапе машинного

цикла, зависит от кода операции i-й

команды КОп, (определяет модификацию

ЦФ-ИО), кода первого операнда 0, и кода

второго операнда — результата предыдущей

(i-1)-и

операции

![]()

В соответствии со структурой граф-схемы этапов все команды ВМ можно разделить на три типа:

* команды типа «Сложение» (Сл);

* команды типа «Запись» (Зп);

* команды типа «Условный переход» (УП).

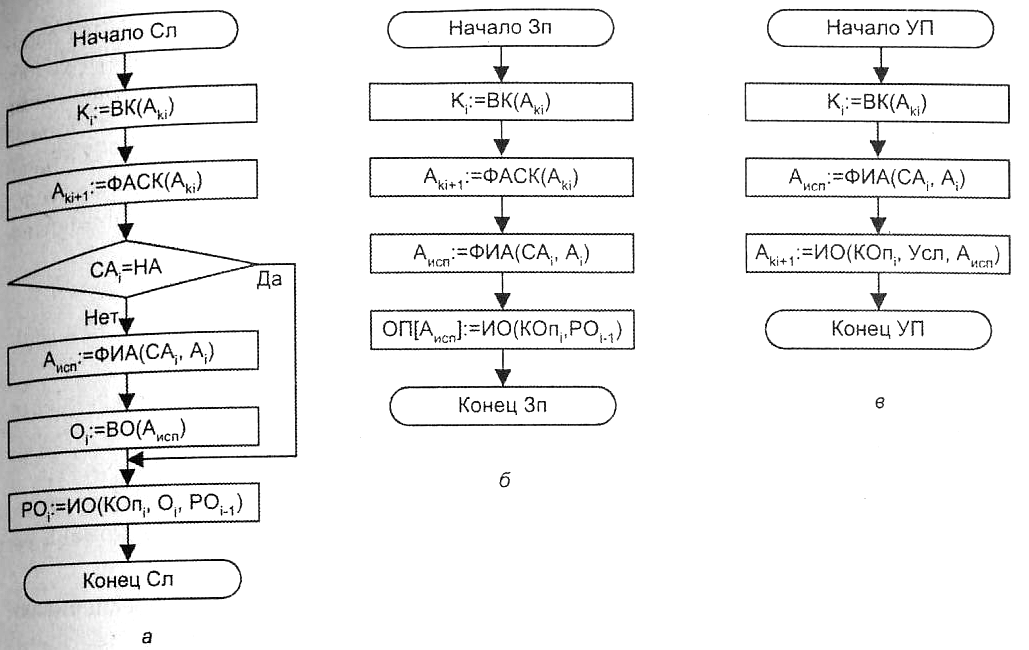

Типовые граф-схемы этапов представлены на рис. 6.1.

Видно, что количество этапов в командах типа «Сл» (см. рис. 6.1, а) колеблется от трех (для непосредственной адресации НА) до пяти. При непосредственной адресации второй операнд записан в адресной части команды, поэтому нет необходимости в реализации устройством управления целевых функций ЦФ-ФИА, ЦФ-ВО. Количество этапов для команд типа «Зп» постоянно и равно четырем (см. рис. 6.1,б) здесь отсутствует необходимость в ЦФ-ВО. Машинный цикл команд типа «УП» состоит из трех этапов (см. рис. 6.1, в), поскольку здесь, помимо выборки операнда, можно исключить и этап ФАСК — действия, обычно выполняемые на этапе, фактически реализуются на этапе ИО.

Рис. 6.1. Типовые граф-схемы этапов исполнения команды: а — «Сложение»; б — «Запись»;

в — «Условный переход»

Оператор этапа исполнения операции для команд «Зп* имеет смысл записи результата предыдущей операции Р0м в ячейку с адресом Аисп:

![]()

Местоположение РО^^ определяется кодом операции Копi. Оператор этапа ИО для команд «УП» обеспечивает формирование адреса следующей (i + 1)-й команды в зависимости от Аисп и значения проверяемого условия перехода Уел:

АК1+1:=И0(К0п!,Усл,Аисп).

Местоположение проверяемого условия также определяется кодом операции КОп,.i

Модель устройства управления

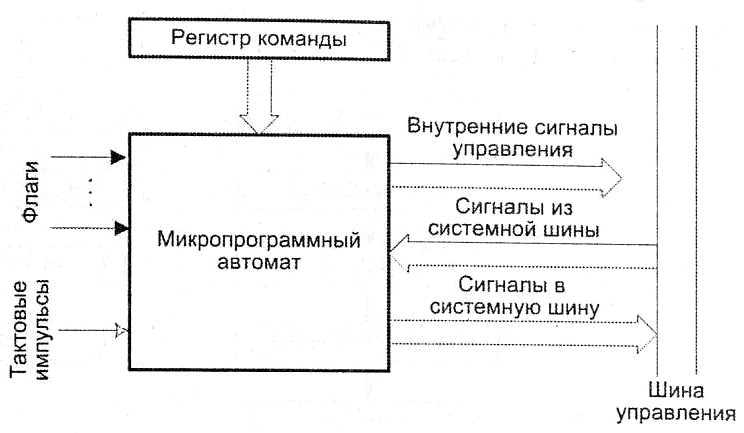

Для выполнения своих функций УУ должно иметь входы, позволяющие определить состояние управляемой системы, и выходы, через которые реализуется управление поведением системы. Модель УУ показана на рис. 6.2 [200]. Годной информацией для устройства управления служат:

* тактовые импульсы — с каждым тактовым импульсом УУ инициирует выполнение одной или нескольких микроопераций;

* код операции — код операции текущей команды поступает из регистра команды и используется, чтобы определить, какие микрооперации должны выполняться в течение машинного цикла;

Рис.6.2 Модель устройства управления

* флаги — требуются устройству управления для оценки состояния ЦП и результата предшествующей операции, что необходимо при выполнении команд условного перехода;

* сигналы из системной шины — часть сигналов с системной шины, обеспечивающая передачу в УУ запросов прерывания, подтверждений и т. п.

В свою очередь, УУ, а точнее микропрограммный автомат, формирует следующую выходную информацию:

* внутренние сигналы управления — эти сигналы воздействуют на внутренние схемы центрального процессора и относятся к одному из двух типов: тем, которые вызывают перемещение данных из регистра в регистр, и тем, что инициируют определенные функции операционного устройства ВМ;

* сигналы в системную шину — также относятся к одному из двух типов: управляющие сигналы в память и управляющие сигналы в модули ввода/вывода.

Структура устройства управления

Как уже отмечалось ранее, процесс функционирования ВМ состоит из последовательности элементарных действий в ее узлах. Такие элементарные преобразования информации, выполняемые в течение одного такта сигналов синхронизации. называются микрооперациями (МО). Совокупность сигналов управления, вызывающих одновременно выполняемые микрооперации, образует микрокоманду (MК). В свою очередь, последовательность микрокоманд, определяющую содержание и порядок реализации машинного цикла, принято называть микропрограммой. Сигналы управления вырабатываются устройством управления, а точнее одним из его узлов— микропрограммным автоматом (МГЛА). Название отражает то, что МПА определяет микропрограмму как последовательность выполнения микроопераций.

Микропрограммы реализации перечисленных ранее целевых функций инициируются задающим оборудованием, которая вырабатывает требуемую последовательность сигналов управления и входит в состав управляющей части УУ.

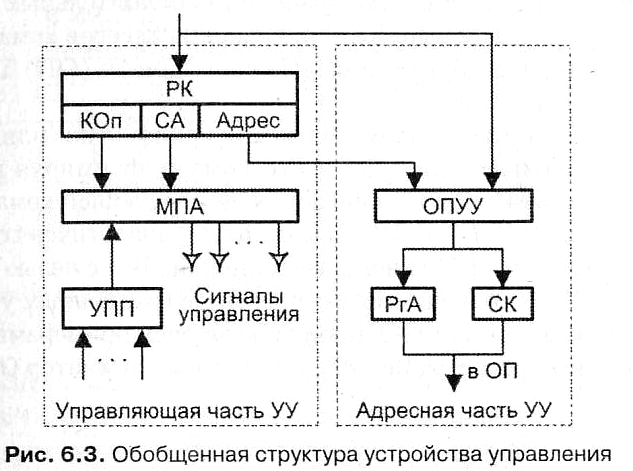

Выполняются микропрограммы исполнительным оборудованием, входящим в состав основной памяти (для ЦФ-ВК и ЦФ-ВО) и операционного устройства ЦФ-ИО). Исполнительным оборудованием для целевых функций ЦФ-ФАСК, ЦФ-ФИА служит адресная часть устройства управления. В обобщенной структуре УУ (рис. 6.3) можно выделить две части: управляющую и адресную.

Управляющая часть УУ предназначена для координирования работы операционного блока ВМ, адресной части устройства управления, основной памяти и других узлов ВМ.

Адресная часть УУ обеспечивает формирование адресов команд и исполнительных адресов операндов в основной памяти.

В состав управляющей части УУ входят:

* регистр команды (РК), состоящий из адресной (Адрес) и операционной (КОп, СА) частей;

* микропрограммный автомат (МПА);

* узел прерываний и приоритетов УПП

Регистр команды РК предназначен для приема очередной команды из запоминающего устройства. Микропрограммный автомат на основании результатов расшифровки операционной части команды (КОп, СА) вырабатывает определенную последовательность микрокоманд, вызывающих выполнение всех целевых функций УУ.

В зависимости от способа формирования микрокоманд различают микропрограммные автоматы:

*с жесткой или аппаратной логикой;

*с программируемой логикой.

Организация МПА этих двух типов будет рассмотрена в последующих разделах.

Узел прерываний и приоритетов позволяет реагировать на различные ситуации, связанные как с выполнением рабочих программ, так и с состоянием ВМ.

298 ^

Адресная часть УУ включает в себя:

* операционный узел устройства управления (ОПУУ);

* регистр адреса (РгА);

* счетчик команд (СК).

Регистр адреса используется для хранения исполнительных адресов операндов, а счетчик команд — для выработки и хранения адресов команд. Содержимое РгА и СК посылается в регистр адреса основной памяти (ОП) для выборки операндов и команд соответственно.

ОПУУ, называемый иначе узлом индексной арифметики или узлом адресной арифметики, обрабатывает адресные части команд, формируя исполнительные адреса операндов, а также подготавливает адрес следующей команды при выполнении команд перехода. Состав ОПУУ может быть аналогичен составу основного операционного устройства ВМ (иногда в простейших ВМ с целью экономии затрат на оборудование ОПУУ совмещается с основным операционным устройством).

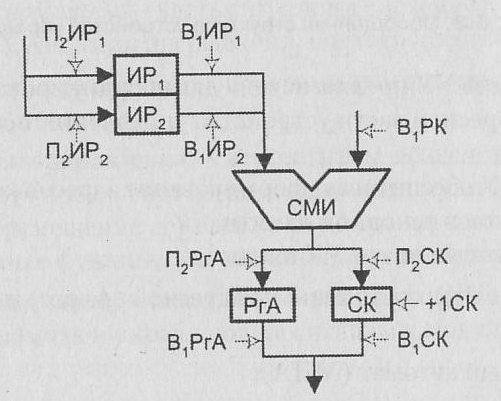

Сказанное об адресной части УУ проиллюстрируем примерами. Пусть в ОПУУ входят два индексных регистра ИР1, ИР2 и индексный сумматор СМИ, как показано на рис. 6.4.

Рис. 6.4. Пример реализации адресной части УУ

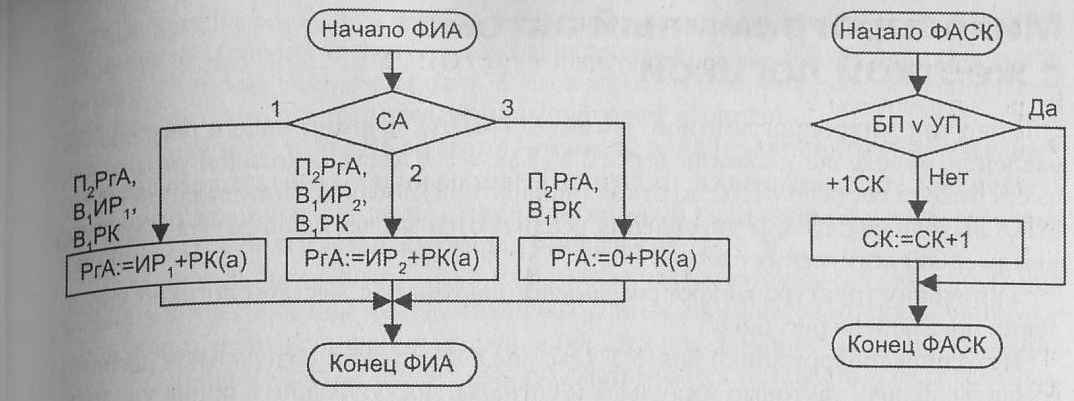

Для данной схемы микропрограмма формирования исполнительного адреса имеет вид, представленный на рис. 6.5, а.

ПРИМЕЧАНИЕ Индексы при сокращениях П. (Прием) и В (Выдача) обозначают фазность передаваемого кода. Каждый длоичпый разряд однофазного код передается по одной цепи (и поступает только на вход S соответствующего триггера). Каждый двоичный разряд парафазного кода передается по двум цепям (и поступает на входы S н R соответствующего триггер, при этом не требуется предварительное обнуление трнггера-приеммика.

Выполняемые действия определяются полем способа адресации. Если СА указывает на индексную адресацию относительно ИР1 или ИРг (СА = 1, СА = 2), то по

Рис. 6.5. Микропрограмма формирования: a — исполнительного адреса; б— адреса

следующей команды

![]()

![]()

Микропрограмма формирования адреса следующей команды (ЦФ-ФАСК) изображена на рис. 6.5, б. Видим, что естественное формирование адреса следующей команды (с помощью СК) не производится, если исполняется команда безусловного (БП) или условного (УП) перехода. Такой адрес формируется на этапах ФИА и ИО, он равен исполнительному адресу (если это УП и условие перехода выполняется, или если это БП),

В состав УУ могут также входить дополнительные узлы, в частности узел организации прямого доступа к памяти. Этот узел обычно реализуется в виде самостоятельного устройства - контроллера прямого доступа к памяти (КПДП). КПДП обеспечивает совмещение во времени работы операционного устройства с процессом обмена информацией между ОП и другими устройствами ВМ, тем самым повышая общую производительность машины.

Довольно часто регистры различных узлов УУ объединяют в отдельный узел управляющих (специальных) регистров устройства управления.

Все множество технологий, используемых при реализации микропрограммых автоматов устройств управления.

Все множество технологий, используемых при реализации микропрограммых автоматов управления, можно свести к двум категориям:

*МПА «жесткой» логикой или аппаратурной реализацией;

*МПА с программируемой логикой.

Микропрограммный автомат с жесткой логикой

Обычно тип микропрограммного автомата (МПА), формирующего сигналы управления, определяет название всего УУ. Так, УУ с жесткой логикой управления имеет в своем составе МПА с жесткой (аппаратной) логикой. При создании такого. МПА выходные сигналы управления реализуются за счет однажды соединенных между собой логических схем.

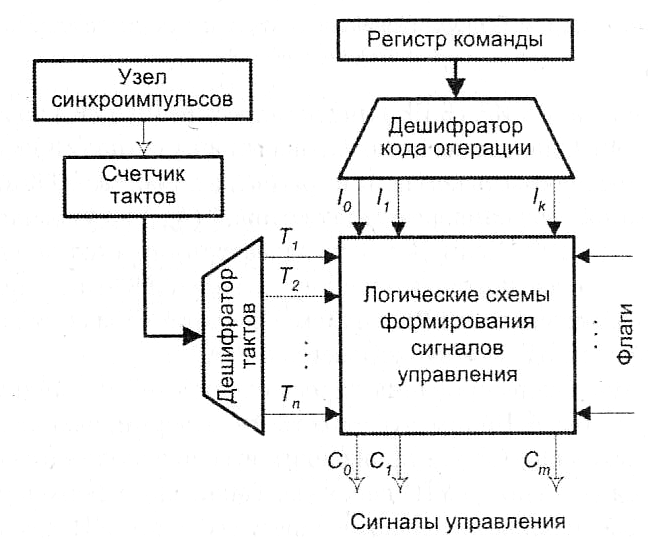

Типичная структура микропрограммного автомата с жесткой логикой управления показана на рис. 6.6.

Исходной информацией для УУ (см. рис. 6.2) служат: содержимое регистра команды, флаги, тактовые импульсы и сигналы, поступающие с шины управления.

![]()

Код операции, хранящийся в РК, используется для определения того, какие СУ и в какой последовательности должны формироваться, при этом, с целью упрощения логики управления, желательно иметь в УУ отдельный логический сигнал для каждого кода операции (I0, I1, ..., Ik). Это может быть реализовано с помощью дешифратора. Дешифратор кода операции преобразует код j-й операции. поступающей из регистра команды (РК), в единичный сигнал j'-м выходе.

Машинный цикл выполнения любой команды состоит из нескольких тактов. Сигналы управления, по которым выполняется каждая микрооперация, должны вырабатываться в строго определенные моменты времени, поэтому все СУ «привязаны» к импульсам синхронизации (СИ), формируемым узлом синхроимпульсов. Период СИ должен быть достаточным для того, чтобы сигналы успели распространиться по трактам данных и другим цепям. Каждый СУ ассоциируется одним из тактовых периодов в рамках машинного цикла. Формирование сигналов, отмечающих начало очередного тактового периода, возлагается на синхронизатор. Синхронизатор содержит счетчик тактов, осуществляющий подсчет СИ. Узел синхроимпульсов после завершения очередного такта работы добавляет к содержимому счетчика тактов единицу. К выходам счетчика подключен дешифратор, с которого и снимаются сигналы тактовых периодов: Tlt..., Т„. В i~u состоянии счетчика тактов, то есть во время i-ro такта, дешифратор тактов вырабатывает единичный сигнал на своем i-м выходе. При такой организации в УУ должна быть предусмотрена обратная связь, с помощью которой по окончании цикла команды счетчик тактов опять устанавливается в состояние Тi.

Дополнительным фактором, влияющим на последовательность формирования СУ являются состояние осведомительных сигналов (флагов), отражающих ход вычислений, и сигналы с шины управления. Эта информация также поступает на вход УУ, причем каждая линия здесь рассматривается независимо от остальных.

Процесс синтеза схемы МПА с жесткой логикой называется структурным синтезом и разделяется на следующие этапы:

* выбор типа логических и запоминающих элементов;

* кодирование состояний автомата;

* синтез комбинационной схемы, формирующей выходные сигналы.

Чтобы определить способ реализации МПА с жесткой логикой, необходимо описать внутреннюю логику УУ, формирующую выходные сигналы управления, как булеву функцию входных сигналов. Канонический метод структурного синте

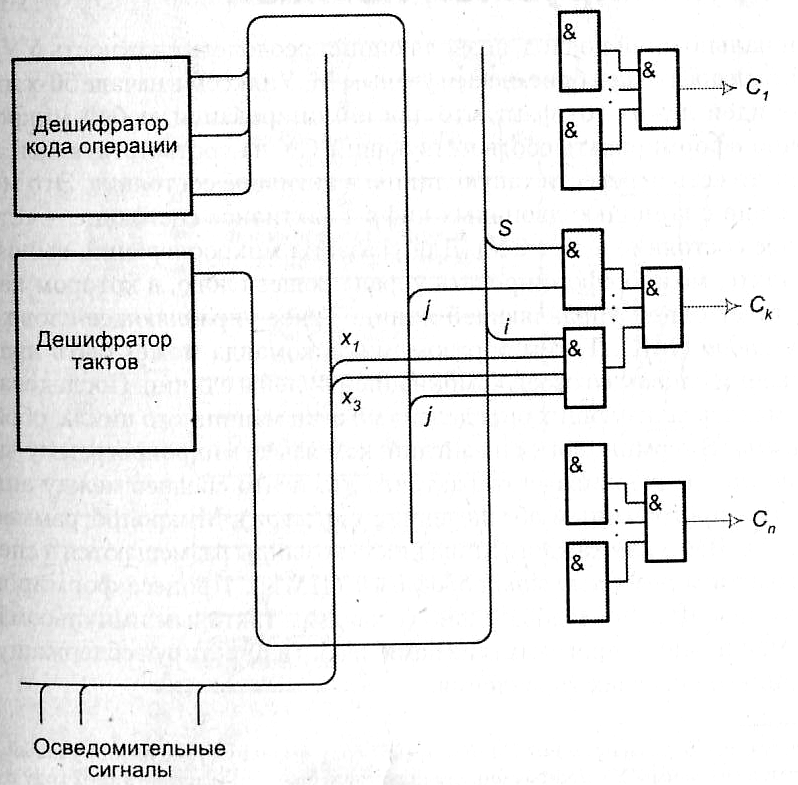

Рис.6.7. Фрагмент схемы управления сигналом

за МПА был предложен В. М. Глушковым. Согласно этому методу, задача синтеза автомата сводится к синтезу комбинационной схемы путем построения системы логических функций с последующей их минимизацией.

Принцип построения логических схем формирования управляющих сигнал поясняется на рис. 6.7. Здесь показан фрагмент схемы, обеспечивающей выработку управляющего сигнала Ск в /-м и S-м тактах выполнения команды с кодом о рации/ причем сигнал Сk появляется в i-м такте только при значениях осведомительных сигналов х1 = 1 и х3 = 1, а в S-м такте всегда.

Таким образом, название «жесткая логика» обусловлено тем, что каждой микропрограмме здесь соответствует свой набор логических схем с фиксированными связями между ними. При реализации простой системы команд узлы МПА с жесткой логикой экономичны и позволяют обеспечить наибольшее быстродействие из всех возможных методов построения МПА. Однако с возрастанием сложности системы команд соответственно усложняются и схемы автоматов с жесткой логикой, в результате чего уменьшается их быстродействие. Второй недостаток МПА с жесткой логикой — малая регулярность, а следовательно, и большие трудности при размещении УУ такого типа на кристалле интегральной микросхемы.

Микропрограммный автомат с программируемой логикой

Принципиально иной подход, позволяющий преодолеть сложность УУ с жесткой логикой, был предложен британским ученым М. Уилксом в начале 50-х годов [224]. В основе идеи лежит тот факт, что для инициирования любой микрооперации достаточно сформировать соответствующий СУ на соответствующей линии управления, то есть перевести такую линию в активное состояние. Это может быть представлено с помощью двоичных цифр 1 (активное состояние — есть СУ) и О (пассивное состояние — нет СУ). Для указания микроопераций, выполняемых в данном такте, можно сформировать управляющее слово, в котором каждый бит соответствует одной управляющей линии. Такое управляющее слово называют микрокомандой (МК). Таким образом, микрокоманда может быть представлена управляющим словом со своей комбинацией нулей и единиц. Последовательность микрокоманд, реализующих определенный этап машинного цикла, образует микропрограмму. В терминологии на английском языке микропрограмму часто называют firmware, подчеркивая тот факт, что это нечто среднее между аппаратур {hardware) и программным обеспечением (software). Микропрограммы для каждой команды ВМ и для каждого этапа цикла команды размещаются в специальном ЗУ, называемом памятью микропрограмм (ПМК). Процесс формирования можно реализовать, последовательно (с каждым тактовым импульсом) извлекая микрокоманды микропрограммы из памяти и интерпретируя содержащуюся в информацию о сигналах управления.

Аналогичную идею, независимо от Уилкса, в 1957 голу выдвинул российский ученый Н.Матюхин. Предложенное им УУ с программируемой логикой было реализовано в 1962 году в специализированной ВМ «Тетива», предназначенной для системы противовоздушной обороны.

Идея заинтересовала многих конструкторов ВМ, но была нереализуема, поскольку требовала использования быстрой памяти относительно большой емкости. Вновь вернулись к ней в 1964 году, в ходе создания системы IBM 360. С тех пор устройства управления с программируемой логикой стали чрезвычайно популярными и были встроены во многие ВМ. В этой связи следует упомянуть запатентованный академиком В. М. Глушковым принцип ступенчатого микропрограммирования который он впервые реализовал в машине «Проминь».

Принцип управления по хранимой

в памяти микропрограмме

Отличительной особенностью микропрограммного автомата с программируемой логикой является хранение

микрокоманд в виде кодов в специализированном запоминающем устройстве — памяти микропрограмм. Каждой команде ВМ в этом ЗУ в явной форме соответствует микропрограмма, поэтому часто устройства управления, в состав которых входит микропрограммный автомат с программируемой логикой, называют микропрограммными.

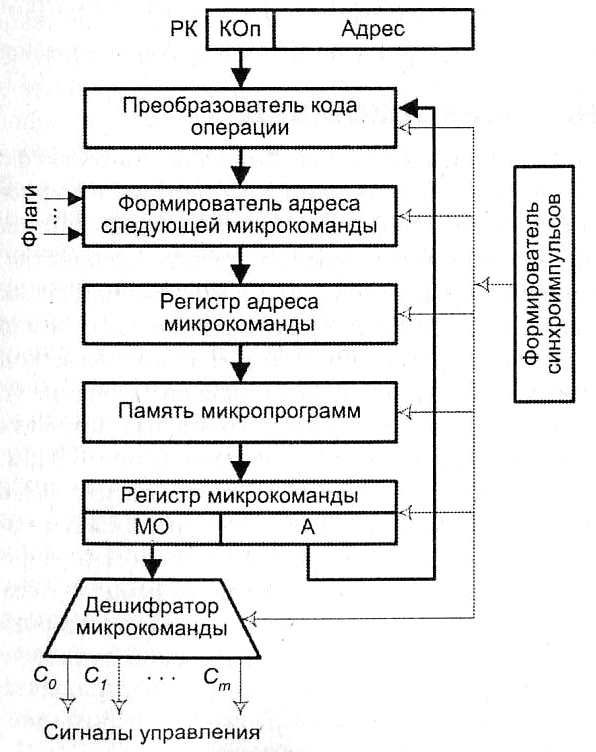

Типичная структура микропрограммного автомата представлена на рис. 6.8. В составе узла присутствуют: память микропрограмм (ПМП), регистр адреса микрокоманды (РАМ), регистр микрокоманды (РМК), дешифратор микрокоманд (ДшМК), преобразователь кода операции, формирователь адреса следующей микрокоманды (ФАСМ), формирователь синхроимпульсов (ФСИ).

Рис.6.8. Микропрограммный автомат с программируемой логикой

Запуск микропрограммы выполнения операции осуществляется путем передачи кода операции из РК на вход преобразователя, в котором код операции преобразуется в начальный (первый) адрес микропрограммы Д. Этот адрес поступает через ФАСМ в регистр адреса микрокоманды. Выбранная по адресу А из ПМП микрокоманда заносится в РМК. Каждая микрокоманда в общем случае содержит микрооперационную (МО) и адресную (А) части. Микрооперационная часть микрокоманды поступает на дешифратор микрокоманды, на выходе которого образуются управляющие сигналы Сi, инициирующие выполнение микроопераций в исполнительных устройствах и узлах ВМ. Адресная часть микрокоманды подается ФАСМ, где формируется адрес следующей микрокоманды Амк. Этот адрес может зависеть от адреса на выходе преобразователя кода операции Ан адресной части текущей микрокоманды А и значений осведомительных сигналов (флагов) X, поступающих от исполнительных устройств. Сформированный адрес микрокоманды снова записывается в РАМ, и процесс повторяется до окончания микропрограммы.

Разрядность адресной (RA) и микрооперационной (RM0) частей микрокоманды определяются из соотношений

6.1

6.2

![]() 6

6

где NMK — общее количество микрокоманд; Ncy — общее количество формируемых сигналов управления. . В свою очередь, необходимая емкость памяти микропрограмм равна

![]()