Методическое пособие

.pdf

Министерство образования Республики Беларусь

БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИНФОРМАТИКИ И РАДИОЭЛЕКТРОНИКИ

Кафедра программного обеспечения информационных технологий

А.А.Прихожий, Р.М.Мерджани

Методическое пособие по курсу

ПРОЕКТИРОВАНИЕ АППАРАТНО-ПРОГРАММНЫХ ВЫЧИСЛИТЕЛЬНЫХ СРЕДСТВ

для студентов специальности “Программное обеспечение информационных технологий”

Минск 1999

1

УДК 681.3

Прихожий А.А., Мерджани Р.М. Методическое пособие по курсу “Проектирование аппаратно-программных вычислительных средств” для студентов специальности “Программное обеспечение информационных технологий”. Мн.: БГУИР, 1999. – 40 с.

Изложены основы международного стандарта языка VHDL описания аппаратуры. Описаны методы построения поведенческих, потоковых и структурных моделей на этом языке, методы компиляционного системного и высокоуровневого синтеза цифровых систем, разбиения системы на аппаратные и программные части, методы сетевого и последовательного планирования вычислительных процессов, а также методы отображения поведенческих описаний в структуры, оптимизированные по критериям минимума времени выполнения и минимума стоимости реализации.

Ил. 28, табл. 15, список лит. - 7 назв.

С А.А.Прихожий, Р.М.Мерджани, 1999

2

|

С О Д Е Р Ж А Н И Е |

|

|

|

Стр. |

1. |

Язык описания аппаратуры VHDL.......................................................... |

4 |

|

1.1. Алфавит языка.................................................................................. |

4 |

|

1.2. Лексические элементы..................................................................... |

4 |

|

1.3. Имена................................................................................................. |

4 |

|

1.4. Предопределенные атрибуты.......................................................... |

5 |

|

1.5. Иерархия конструкций VHDL......................................................... |

7 |

|

1.6. Файл проекта..................................................................................... |

8 |

|

1.7. Библиотечные модули...................................................................... |

8 |

|

1.8. Объявления и спецификации........................................................... |

10 |

|

1.9. Типы................................................................................................... |

13 |

|

1.10. Выражения...................................................................................... |

13 |

|

1.11. Параллельные операторы.............................................................. |

17 |

|

1.12. Последовательные операторы....................................................... |

19 |

|

1.13. Пакет STANDARD......................................................................... |

21 |

2. |

Разработка моделей на языке VHDL....................................................... |

22 |

|

2.1. Поведенческая VHDL-модель......................................................... |

22 |

|

2.2. Структурная VHDL-модель............................................................. |

22 |

|

2.3. Потоковая VHDL-модель................................................................. |

23 |

3. |

Синтез на системном уровне. .................................................................. |

23 |

4. |

Высокоуровневый синтез. ........................................................................ |

24 |

5. |

Последовательное планирование вычислительных процессов. ........... |

25 |

|

5.1. Планирование методом целочисленного |

|

|

линейного программирования.......................................................... |

26 |

|

5.2. Планирование методом свертывания графа |

|

|

распараллеленности операторов...................................................... |

27 |

6. |

Сетевое планирование вычислительных процессов. ............................. |

29 |

|

6.1. Исходные отношения....................................................................... |

29 |

|

6.2. Оценка параметров сетевого алгоритма......................................... |

30 |

|

6.3. Задачи и методы оптимизации сети................................................ |

31 |

|

6.4. Пересчет множеств клик.................................................................. |

31 |

|

6.5. Проблема существования сети........................................................ |

33 |

|

6.6. Решение проблемы существования................................................ |

34 |

|

6.7. Синтез сети....................................................................................... |

34 |

7. |

Размещение и связывание........................................................................ |

35 |

8. |

Отображение поведения в структуру...................................................... |

36 |

9. |

Синтез в системе AHILES........................................................................ |

37 |

10. Лабораторные работы............................................................................. |

37 |

|

Список рекомендуемой литературы........................................................... |

39 |

|

3

1. Язык описания аппаратуры VHDL

Язык описания аппаратуры VHDL создан на базе языка программирования ADA Министерством обороны США в 1983 г. Последующие стандартные версии языка разработаны Институтом инженеров-электриков и электронщиков (IEEE) в 1987, 1982, 1998 гг. Первоначально язык создавался для построения иерархических моделей цифровых схем и систем любой степени сложности. В последние годы он расширен на аналоговые схемы. Язык широко используется в системах построения формальных моделей схем, их имитационного моделирования, синтеза, верификации, генерации тестов.

1.1. Алфавит языка

Шесть категорий базовых графических символов языка VHDL приведены в табл.1. Это прописные и строчные буквы, цифры, специальные символы, пробел.

Из отдельных базовых символов строятся составные символы (строка 7 табл.1).

Алфавит языка |

Таблица 1 |

|

№ |

Категория символов |

Примеры |

1 |

Прописные буквы |

A B C D E F G H I J K L M N O P Q R S T U V W X Y Z |

2 |

Цифры |

0 1 2 3 4 5 6 7 8 9 |

3 |

Специальные символы |

“ # & ‘ ( ) * + , - . / : ; < = > _ | |

4 |

Символ пробел |

|

5 |

Строчные буквы |

a b c d e f g h i j k l m n o p q r s t u v w x y z |

6 |

Другие специальные |

! $ % @ ? [ \ ] ^ ` { } ~ |

|

символы |

|

7 |

Составные символы |

=> ** := /= >= <= <> |

1.2. Лексические элементы

Лексические элементы включают разграничители, идентификаторы, зарезервированные слова, абстрактные литералы, символьные литералы, строковые литералы, бит-строковые литералы, комментарии. Используемые в дальнейшем обозначения и примеры лексических элементов приведены в табл.2. К разграничителям относятся некоторые специальные базовые и составные символы. Абстрактные литералы делятся на десятичные и базированные. Физические литералы строятся в виде композиций других лексических элементов. Любой VHDL-текст представляется некоторой последовательностью лексических элементов.

1.3. Имена

Имена указывают на некоторые части VHDL-моделей. Они могут быть простыми, селективными, индексными, слайсовыми, атрибутными (табл.3).

4

Лексические элементы |

|

|

|

|

Таблица 2 |

|

Обозн. |

Название |

|

Примеры, примечания |

|||

ID |

Идентификатор |

X_1 Counter S0 Segment_Register |

||||

AL |

Абстрактный литерал |

Это десятичный или базированный литерал |

||||

DL |

Десятичный литерал |

15 0.0 3.14 1.67E-10 100_300 -9.4_123E2 |

||||

BL |

Базированный литерал |

16#ABCDEF# 2#10010001# 7#15_666# |

||||

CL |

Символьный литерал |

‘Z’ ‘z’ |

‘.’ |

‘ ‘ ‘’’ ‘s’ |

‘*’ |

‘@’ ‘A’ ‘-‘ |

SL |

Строковый литерал |

“VHDL” |

“ “ |

“1010” “””” |

“Literal” |

|

BSL |

Бит строковый литерал |

B”1111_0000_0101” O”7405” X”f05” |

||||

PHL |

Физический литерал |

3ns 5min sec 7ps 12fs 9us 34ms 3hr |

||||

CM |

Комментарий |

−− Comment |

|

|

|

|

RW |

Зарезервированное слово |

abs access after alias |

not |

null with xor |

||

Имена |

|

|

Таблица 3 |

Обозн. |

Название |

|

Примеры, примечания |

NM |

Имя |

SMN SLN INN SCN ATN |

|

SMN |

Простое имя |

Name_S Z |

A12 Signal_in_25 |

SLN |

Селективное имя |

Standard.all |

U0.R.Date B12.Sig.Edge |

INN |

Индексное имя |

RAM(X”00A9”,4) WORD(0) A(I,I+1,’C’) |

|

SCN |

Слайсовое имя |

WORD(0 to 3) Reg_7(15 downto 8) |

|

ATN |

Атрибутное имя |

CLOCK’EVENT Reg_1_Out’Stable |

|

Простые имена используются для именования модулей, блоков, сигналов и т.д. Селективные имена используются для обозначения элементов записи, объектов, доступ к которым осуществляется посредством указателей, объектов, являющихся внутренними для библиотек, модулей, блоков. Индексированное имя обозначает элемент массива. Слайсовое имя обозначает одномерный массив, составленный из последовательных элементов другого массива. Атрибутные имена обозначают ассоциированные значения, функции, типы, диапазоны, сигналы, константы.

1.4. Предопределенные атрибуты

Предопределенные атрибуты ассоциируются с типом, массивом, сигналом, блоком (табл.4). Типом результата оценки атрибута может быть значение, тип, диапазон, функция, сигнал. Атрибуты, ассоциированные со скалярным типом, позволяют определять базовый тип; левое, правое, верхнее и нижнее граничное значение; номер позиции для указанного значения или значение, соответствующее указанной позиции; следующее, предыдущее, правое и левое значение для указанного значения. Атрибуты, ассоциированные с массивом, позволяют определять левую, правую, верхнюю и нижнюю границу диапазона значений указанного индекса; прямой и реверсный диапазон значений индекса; число значений в диапазоне. Атрибуты, ассоциированные с сигналом, позволяют вводить задержанные копии существующих сигналов, создавать новые

5

сигналы, характеризующие поведение существующих, проверять, есть ли событие (изменение значения) на сигнале или была ли попытка изменить значение, и когда это произошло. Атрибуты, ассоциированные с блоком, проверяют, поведение или структура описывается этим блоком.

Атрибуты |

Таблица 4 |

|

№ |

Имя атрибута |

Результат |

|

Атрибуты |

типа Т |

1 |

T’BASE |

Базовый тип |

2 |

T’LEFT |

Левая скалярная граница |

3 |

T’RIGHT |

Правая скалярная граница |

4 |

T’HIGH |

Верхняя скалярная граница |

5 |

T’LOW |

Нижняя скалярная граница |

6 |

T’POS(X) |

Номер позиции значения X |

7 |

T’VAL(X) |

Значение с номером позиции X |

8 |

T’SUCC(X) |

Значение, номер позиции которого на 1 больше номера |

|

|

позиции значения X |

9 |

T’PRED(X) |

Значение, номер позиции которого на 1 меньше номера |

|

|

позиции значения X |

10 |

T’LEFTOF(X) |

Значение слева от значения X |

11 |

T’RIGHTOF(X) |

Значение справа от значения X |

|

Атрибуты |

массива А |

12 |

A’LEFT[(N)] |

Левая граница диапазона N-го индекса |

13 |

A’RIGHT[(N)] |

Правая граница диапазона N-го индекса |

14 |

A’HIGH[(N)] |

Верхняя граница диапазона N-го индекса |

15 |

A’LOW[(N)] |

Нижняя граница диапазона N-го индекса |

16 |

A’RANGE[(N)] |

Диапазон значений N-го индекса |

17 |

A’REVERSE_RANGE |

Реверсный диапазон значений N-го индекса |

|

[(N)] |

|

18 |

A’LENGTH[(N)] |

Число значений в диапазоне N-го индекса |

|

Атрибуты |

сигнала S |

19 |

S’DELAYED[(T)] |

Сигнал, задержанный на Т единиц времени |

20 |

S’STABLE[(T)] |

Сигнал, принимающий TRUE, если на S не было события |

|

|

Т единиц времени, иначе FALSE |

21 |

S’QUIET[(T)] |

Сигнал, принимающий TRUE, если S является тихим в |

|

|

течение Т единиц времени, иначе FALSE |

22 |

S’TRANSACTION |

Сигнал типа BIT, принимающий инверсное значение в |

|

|

каждом цикле моделирования, в котором S активен |

23 |

S’EVENT |

Значение TRUE, если на S произошло событие, иначе |

|

|

FALSE |

24 |

S’ACTIVE |

Значение TRUE, если S активен, иначе FALSE |

25 |

S’LAST_EVENT |

Время, прошедшее с момента последнего события на S |

26 |

S’LAST_ACTIVE |

Время, прошедшее с момента последней активности S |

27 |

S’LAST_VALUE |

Предыдущее значение, существовавшее до последнего |

|

|

изменения S |

|

Атрибуты |

блока В |

28 |

B’BEHAVIOR |

Значение TRUE, если блок В не содержит оператора |

|

|

конкретизации компонента, иначе FALSE |

29 |

B’STRUCTURE |

Значение TRUE, если блок В не содержит не пассивного |

|

|

оператора процесс, иначе FALSE |

6

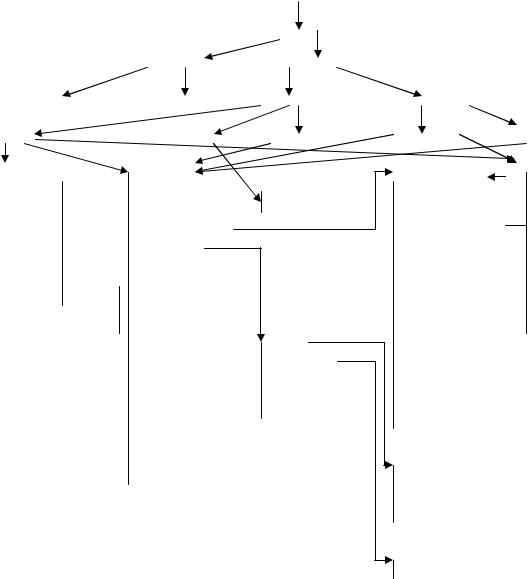

1.5. Иерархия конструкций в языке VHDL

Наиболее общим понятием, отображающим способ построения VHDLмодели, является файл проекта (design file). Файл проекта строится из модулей проекта (design unit), каждый из которых формируется из контекстного клоза

(context clause) и библиотечного модуля (library unit). Контекстный клоз появляется в двух вариантах: библиотечный клоз (library clause) и клоз использования (use clause). Различаются два типа библиотечных модулей:

первичные (primary unit) и вторичные (secondary unit). К первичному типу относятся сущность (entity), конфигурация (configuration) и пакет (package). Ко вторичному типу относятся архитектурное тело (architecture) и тело пакета

(package body). В модуле сущность определяется интерфейс проекта с внешней средой (interface declaration), выполняются некоторые внутренние объявления (declarative item) и описываются некоторые элементы поведения с помощью параллельных операторов (concurrent statement). В модуле

конфигурация определяется элементный состав иерархического проекта с помо-

Design_file

Design_unit

Context_clause

Library_clause Use_clause

Entity Configuration

Interface_decl Decl_item

−Subprogram_d −Subprogram_b −Type_decl −Subtype_decl −Constant_decl  −Signal_decl −Variable_decl −File_decl −Alias_decl −Compon_decl −Attribute_decl −Attribute_spec −Configur_spec −Disconnec_spec −Use_clause

−Signal_decl −Variable_decl −File_decl −Alias_decl −Compon_decl −Attribute_decl −Attribute_spec −Configur_spec −Disconnec_spec −Use_clause

Library_unit

Primary_unit

Package

−Block_config −Compon_config

−Scalar −Composite −Access −File

−Inc_definition

Secondary_unit |

|

|

Architecture |

|

Package_body |

Sequential_stat |

|

Concurrent_stat |

−Wait |

|

−Block |

−Assertion |

|

−Process |

|

||

−Signal_assign |

|

−Procedure_call |

−Variable_assign |

|

−Assertion |

−Procedure_call |

|

−Signal_assign |

−If |

|

−Component_inst |

−Case |

|

−Generate |

−Loop |

|

|

−Next |

|

|

−Exit |

|

|

−Return |

|

|

−Null |

|

|

−Enumeration |

|

|

−Integer |

|

|

−Floating |

|

|

−Physical |

|

|

−Array |

|

|

−Record |

|

|

Рис.1. Основные понятия языка VHDL

7

щью конфигураций блоков (block configuration) и конфигураций компонентов

(component configuration). Модули пакет и тело пакета содержат объявления составляющих проекта, причем тело подпрограммы (subprogram body) объявляется только в пакете. В модуле архитектурное тело описываются структура и функционирование проекта.

1.6. Файл проекта

VHDL-проект представляется набором файлов проекта. Один файл проекта DF (design file) включает несколько модулей проекта DU (design unit) (табл.5). Модуль проекта состоит из последовательности (возможно пустой) контекстных атомов CI (context item) и одного библиотечного модуля LU (library unit). Контекстный атом либо определяет логическое имя библиотеки, содержащей ранее компилированные модули проекта, либо обеспечивает по выбору прямую видимость объявлений в библиотеке, пакете или другом модуле. Библиотечный модуль принадлежит к одному из пяти ранее определенных типов.

Основные понятия файла проекта |

|

Таблица 5 |

|

Обозна |

Название понятия |

Определение |

|

чение |

|

|

|

DF |

Файл проекта (design file) |

DU … DU |

|

DU |

Модуль проекта (design unit) |

CI … CI LU |

|

CI |

Контекстный атом (context item) |

library ID,…,ID; use |

SN,…,SN; |

LU |

Библиотечный модуль (library unit) |

entity (ED) configuration (CD) package |

|

|

|

(PD) architecture (AB) |

package body (PB) |

1.7. Библиотечные модули

Правила объявления всех пяти типов библиотечных модулей представлены

втабл.6. Каждое объявление использует свое подмножество множества зарезервированных слов. Квадратные скобки [] означают возможное отсутствие содержащегося в нем описания.

Объявление сущности ED (entity) с именем ID определяет интерфейс между объектом проекта и внешней средой, в которой он используется. Параметры настройки и порты определяются посредством объявлений интерфейсов IFD

(interface declaration). Атомы объявлений DI (declarative item) (за исключением объявлений переменных и компонент, а также спецификаций конфигураций) и

параллельные операторы CST (concurrent statement) (разрешены операторы утверждения, вызова процедуры и пассивные операторы процесс), включаемые

вмодуль entity, относятся ко всем архитектурным телам и конфигурациям, ссылающимся на модуль.

Объявление конфигурации CD (configuration) связывает компоненты с частями иерархического проекта. Объявление включает имя конфигурации ID, имя сущности IDE, объявления клозов использования и спецификаций атрибутов DI, конфигурацию блока BC. Конфигурация блока BC с именем NM относится либо к архитектурному телу, либо к внутреннему блоку,

8

определяемому оператором блока или оператором генерации (в этом случае используется выражение EXPR). В конфигурацию блока входят либо конфигурации вложенных блоков, либо конфигурации компонентов. Конфигурация компонента CC относится к копиям ID компонента NM. Компонент может связываться с парой модулей сущность/архитектура, с вложенной конфигурацией или не быть связанным. В конфигурацию компонента вкладывается конфигурация блока BC.

Библиотечные модули |

|

Таблица 6 |

|

Обозн- |

Название |

Определение |

Пример |

ачение |

|

|

|

ED |

Интерфейс |

entity ID is |

entity Inverter is |

|

объекта |

[generic (IFD; … IFD);] |

generic (Delay:Time:=1ns); |

|

проекта (entity |

[port (IFD; … IFD);] |

port (A:in Bit; |

|

declaration) |

DI … DI |

B:out Bit); |

|

|

[begin CST … CST] |

end Inverter; |

|

|

end [ID]; |

|

CD |

Конфигурация |

configuration ID of ID is |

configuration C_1 of Adder is |

|

(configuration |

DI … DI BC |

use Cells.all; |

|

declaration) |

end [ID]; |

for Structure |

|

|

|

• • • |

|

|

|

end for; |

|

|

|

end C_1; |

BC |

Конфигурация |

for NM [EXPR] |

for Block_1 |

|

блока (block |

DI … DI |

for Block_9 |

|

configuration) |

BC|CC … BC|CC |

• • • |

|

end for; |

||

|

|

end for; |

|

|

|

|

end for; |

CC |

Конфигурация |

for ID, … ,ID : NM |

for REG_1: Reg |

|

компонента |

[use entity NM [(ID)] | |

use entity REGISTER(Str); |

|

(component |

configuration NM | open |

for Str |

|

configuration) |

[generic map (AE, … ,AE)] |

for Fl1 : Flip_Flop |

|

|

[port map (AE, … ,AE)];] |

use entity Flip_Flop(Flow); |

|

|

BC |

end for; |

|

|

end for; |

end for; |

|

|

|

end for; |

PD |

Пакет (package |

package ID is |

package Con_pi is |

|

declaration) |

DI … DI |

constant Pi : Real:=3.14; |

|

|

end [ID]; |

end Con_pi; |

AB |

Архитектурное |

architecture ID of ID is |

architecture Fun of Inverter is |

|

тело |

DI … DI |

begin |

|

(architecture |

begin CST … CST |

B<=not A after Delay; |

|

body) |

end [ID]; |

end Fun; |

PB |

Тело пакета |

package body ID is |

package body Logic is |

|

(package body) |

DI … DI |

function “not” (A:Integer) |

|

|

end [ID]; |

return Integer is |

|

|

|

begin |

|

|

|

if A=0 then return 1; |

|

|

|

else return 0; end if; |

|

|

|

end “not”; |

|

|

|

end Logic; |

9

1.8. Объявления и спецификации

Язык VHDL определяет следующие виды сущностей, которые объявляются

явно или неявно: подпрограмма (subprogram), тело подпрограммы (subprogram body), тип (type), подтип (subtype), константа (constant), сигнал (signal), переменная (variable), файл (file), повторное объявление (alias declaration), ком-

понент (component), атрибут (attribute). Подпрограмма может объявляться в виде процедуры (procedure) или в виде функции (function). Специфицироваться

в языке могут атрибуты (attribute specification), конфигурации (configuration specification), развязывания (disconnection specification). Объявления и специфи-

кации могут подключаться с помощью клоза использования (use clause).

Вобъявлении процедуры или функции (subprogram declaration) определяет-

ся ее имя ID или SL, список формальных параметров IFD (interface declaration)

иподтип NM возвращаемого значения для функции. Формальные параметры относятся к классам константа, переменная, сигнал. Допустимыми режимами

параметров являются in, out, inout. Объявление интерфейса определяет класс, имя, режим, подтип и значение по умолчанию формальных параметров.

Вдополнение к объявлению, тело подпрограммы (subprogram body) содержит определение внутренных объектов ID и описание алгоритма с использованием последовательных операторов SST (sequential statement).

Объявление типа является полным (full type declaration) или неполным ICD (incomplete type declaration). Полное объявление определяет скалярный SCLR (scalar type), составной CMPS (composite type) тип, тип доступ ACC (access) или тип файл FIL (file).

Объявление подтипа (subtype declaration) определяет подтип ID с помощью указания подтипа STI (subtype indication). В указании подтипа определяются имя разрешающей функции RFN (resolution function name), имя базового типа

NM, диапазон значений типа либо диапазон значений индексов базового типа массив.

Вобъявлении константы (constant declaration), сигнала (signal declaration)

ипеременной (variable declaration) определяются имена объектов ID, их подтипы STI, значения по умолчанию посредством статических выражений EX.

Объявление файла (file declaration) определяет имя файла ID, подтип содержащихся в нем значений STI, режим in или out и имя файла NM в окружающей операционной системе.

Повторное объявление (alias declaration) вводит новое имя ID подтипа STI

для ранее объявленного объекта с именем NM. Класс имени ID совпадает с классом имени NM.

Вобъявлении компонента (component declaration) определяются имя ID,

формальные параметры настройки (generic) и порты (port).

Объявление атрибута (attribute declaration) определяет имя ID и подтип NM атрибута.

Вспецификации атрибута (attribute specification) описываются имя ID

атрибута, имена NM и тип сущностей, которые он характеризует, значение EX.

10