- •1. Управляющие эвм, требования к ним по сравнению с пк

- •2. Сигнальные процессоры и плк

- •3. Упрощенный критерий оценки эвм, блок-схема «машины фон-Неймана», сравнение с Гарвардской архитектурой

- •4. Контроллер памяти, шина процессора

- •X86-система с внешним контроллером памяти (слева) и с контроллером памяти, встроенным в процессор (справа)

- •5. Скорость чтения и записи памяти, латентность памяти

- •6. Архитектура процессора как совместимость с кодом, наборы команд

- •7. О многоядерности как концепции, различия между ядрами одной микроархитектуры, ревизии цп

- •8. Принцип действия кэШа, многоуровневое кэширование, регистры процессора

- •9. Предвыборка данных, принцип повышения скорости передачи информации для памяти ddr2, ddr3

- •10. Сравнение кинематических пар вращательной и поступательной в управляемых механизмах (станки, роботы)

- •11. Ангулярная система координат

- •12. Основные команды управления траекторией движения промышленного робота

- •13. График движения между двумя точками, торможение

- •14. Многокоординатное управление движениями, влияние технологического процесса и размера партии изготавливаемых деталей, пример

- •15. Позиционное и контурное управление движениями

- •16. Числовое программное управление (nc, cnc)

- •17. Исполнительные элементы привода, гидро и пневмоцилиндры

- •18. Классификация электродвигателей, обратимость электромашин

- •19. Электромашина постоянного тока, основные параметры и их зависимости

- •20. Бесколлекторные двигатели постоянного тока

- •21. Механические характеристики электродвигателей (графики зависимости ω от м)

- •22. Асинхронный электродвигатель (принцип работы, достоинства, относительный недостаток, скольжение)

- •23. Синхронный двигатель (сравнение с асинхронным двигателем)

- •24. Датчики сау (основные требования к ним, классификация, датчики приближения)

- •25. Датчики угла поворота вала

- •26. Частотно-регулируемый привод на примере sb-19

- •27. Оптическая развязка сигнальных цепей

- •28. Основные показатели усилителя

- •29. Логарифмическая шкала, децибелы

- •30. Сквозной акустический тракт, частотные свойства слуха человека

- •31. Представление звука как суммы гармонических колебаний

- •32. Акустическое оформление громкоговорителей (колонки)

- •33. Ачх акустического тракта

- •34. Полевые моп-транзисторы

- •35. Логические ячейки nor и nand

- •36. Полевые транзисторы с управляющим p-n переходом

- •37. Физический принцип работы флеш-памяти, основные параметры

- •38. Блок питания с непрерывным регулированием

- •39. Операционный усилитель

- •40. Пример линейной сау температурой

- •41. Система пид

- •42. Анализ устойчивости сау

- •43. Терморегулятор на примере трм251

- •44. Охлаждение эвм

- •45. Энергосбережение в эвм

- •46. Импульсный блок питания эвм

- •47. Силовые импульсные цепи

- •48. Шим и чим

- •49. Источники бесперебойного питания эвм

- •50. Мостовые схемы преобразования переменного тока в постоянный и обратно

- •51. Система scada

- •52. Компьютерные сети в управлении (can, profibus)

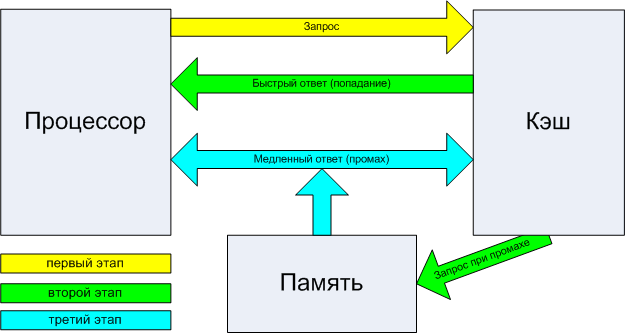

8. Принцип действия кэШа, многоуровневое кэширование, регистры процессора

Во всех современных процессорах есть кэш (cache). Это разновидность памяти (кардинальные отличия кэша от ОЗУ — скорость работы и меньшая задержка доступа), которая является своего рода «буфером» между контроллером памяти и процессором и служит для увеличения скорости работы с ОЗУ.

Основной принцип работы процессорного кэша. Второй этап предусматривает два различных варианта развития событий: быстрый ответ, либо передачу запроса дальше, в память. Третий этап в случае быстрого ответа отсутствует.

В

каждый момент программа работает не со

всей памятью, а, как правило, с относительно

маленьким её фрагментом. Напрашивается

решение — загрузить этот фрагмент в

«быструю» память, обработать его там,

а потом уже записать обратно в «медленную»

(или просто удалить из кэша, если данные

не изменялись). В общем случае, именно

так и работает процессорный кэш: любая

считываемая из памяти информация

попадает не только в процессор, но и в

кэш. И если эта же информация нужна

снова, сначала процессор проверяет: нет

ли её в кэше? Если есть (а современные

кэши совершенны настолько, что это

происходит в подавляющем большинстве

случаев) — информация берётся оттуда,

и обращения к памяти не происходит

вовсе. Аналогично с записью: информация,

если её объём влезает в кэш, пишется

именно туда, и только потом, когда

процессор закончил операцию записи, и

занялся выполнением других команд,

данные, записанные в кэш, параллельно

с работой процессорного ядра «потихоньку»

выгружаются в ОЗУ.

Специфика конструирования современных процессорных ядер привела к тому, что систему кэширования в подавляющем большинстве CPU приходится делать многоуровневой. Кэш первого уровня (самый «близкий» к ядру) традиционно разделяется на две (как правило, равные) части: кэш инструкций (L1I) и кэш данных (L1D). Это разделение предусматривается так называемой «гарвардской архитектурой» процессора, которая по состоянию на сегодня является самой популярной теоретической основой для построения современных CPU. В L1I, соответственно, аккумулируются только команды (с ним работает декодер), а в L1D — только данные (они впоследствии, как правило, попадают во внутренние регистры процессора — обо всём этом см. ниже). Иерархически «над» L1 стоит кэш второго уровня — L2. Он, как правило, в 2-8 раз больше по объёму, примерно втрое медленнее, и является уже «смешанным» — там располагаются и команды, и данные. В первых многоядерных процессорах у каждого ядра были свои L1, но общий L2. Сегодня у каждого ядра есть свой L2, зато общим для всех ядер является L3 (кэш третьего уровня), который в 4-32 раза больше, чем L2, и ещё примерно втрое медленнее (но всё ещё быстрее памяти). Алгоритм работы с многоуровневым кэшем в общих чертах не отличается от алгоритма работы с одноуровневым, просто добавляются дополнительные итерации: сначала информация ищется в L1, если там промах — в L2, потом — в L3, и уже потом, если ни на одном уровне кэша она не найдена — идёт обращение к основной памяти (ОЗУ).

Регистры — по сути, те же ячейки памяти, но «территориально» они расположены прямо в процессорном ядре. Разумеется, скорость работы с регистрами намного больше не только скорости работы с ОЗУ, но и с кэшами любого уровня. Поэтому большинство команд архитектуры x86 предусматривают осуществление действий именно над содержимым регистров, а не над содержимым памяти. Однако общий объём регистров процессора, как правило, очень мал — он не сравним даже с объёмом кэшей первого уровня и составляет всего сотни байт. Поэтому код программы (не на языке высокого уровня, а именно машинный) обычно содержит примерно такую последовательность операций: загрузить в регистры процессора информацию из ОЗУ, произвести некое действие над содержимым этих регистров, поместив результат туда же, в регистры, а потом снова выгрузить результат в основную память.