- •И.А. Чернышев, А. Ю. Чернышев

- •ЭЛЕКТРОННАЯ, МИКРОПРОЦЕССОРНАЯ И ПРЕОБРАЗОВАТЕЛЬНАЯ ТЕХНИКА

- •Лабораторная работа №1

- •ОСЦИЛЛОГРАФИРОВАНИЕ В ЭЛЕКТРОННЫХ СХЕМАХ

- •Таблица 1.1

- •ИССЛЕДОВАНИЕ ЛОГИЧЕСКИХ СХЕМ

- •Таблица 2.1

- •Таблица 2.5

- •Таблица 2.7

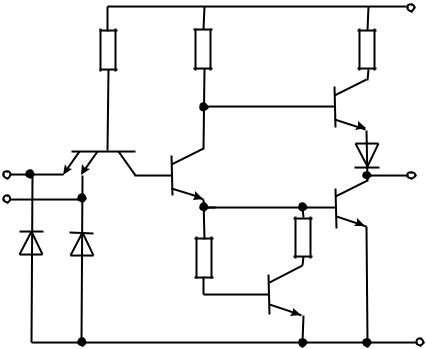

- •Рис. 2.25. Принципиальная схема

- •Таблица 2.8

- •Теория

- •Таблица 2.9

- •Таблица 2.10

- •Таблица 2.11

- •Приложение 1

- •Серия ТТЛ

- •Параметр

- •Адрес

- •Таблица 4.4

- •Таблица 5.1

- •Хранение

- •Таблица 5.4

- •Примечание

- •Лабораторная работа № 6

- •Таблица 6.2

- •Состояния выходов счетчика

- •Таблица 6.3

- •Рис. 7.5. Диаграммы напряжений параллельного режима работа

- •регистра К155ИР16

- •Таблица 7.1

- •Таблица 7.3

- •Рис.8.4.Диаграммы напряжений

- •Electronics Workbench

- •Лабораторная работа № 10

- •ЦИФРО-АНАЛОГОВЫЕ ПРЕОБРАЗОВАТЕЛИ

- •Рис.10.2. Простейшая схема ЦАП с суммированием весовых токов

- •3. Последовательные ЦАП с широтно-импульсной модуляцией

входных сигналов. Схема работает следующим образом. Если на входе инвертора действует напряжение логического нуля, то транзистор VT1, имеющий p -канал, полностью открыт, поскольку его затвор при этом

соединен с общим проводом и поэтому на него подается напряжение отпирающей полярности относительно истока, соединенного с плюсом источника питания. Транзистор VT2, имеющий n-канал, закрыт, вследствие чего напряжение на выходе инвертора максимально и соответствует напряжению логической единицы.

Когда на вход схемы подается положительное напряжение логической единицы, то транзистор VT1 закрывается, а транзистор VT2 полностью открывается, вследствие чего напряжение на выходе становится нулевым, то есть его логический уровень низкий.

Возможные состояния работы микросхемы сведены в табл. 2.5.

|

Таблица 2.5 |

Uвх |

Uвых |

0 |

1 |

1 |

0 |

Особенностью КМОП микросхем является то, что если вход схемы не подключен к источнику сигнала, то это соответствует высокому входному логическому уровню.

4. Транзисторно-транзисторная логика

Интегральные микросхемы транзисторно-транзисторной логики (ТТЛ) получили широкое распространение благодаря сравнительно высокому быстродействию и надежности, технологичности изготовления, функциональной полноте серии ТТЛ элементов.

Основной элемент ТТЛ представлен на рис.2.16. Вход интегральной схемы (ИС) представляет собой многоэммитерный транзистор VT1. Отдельно такие транзисторы не выпускаются, а используются только в интегральных схемах.

Если на входы 1 и 2 ИС подан высокий уровень напряжения Uвх1

(рис.2.17), то ток, проходящий через резистор R1 по открытому в прямом направлении переходу база-коллектор транзистора VT1, течет и через базу транзистора VT2, открывая его. Ток эмиттера транзистора VT2 открывает по базовым цепям транзисторы VT3 и VT5.

При этом базовый ток транзистора VT5 поддерживается на таком уровне, что транзистор остается в открытом состоянии даже при боль-

20

ших значениях выходного тока (10mA – 15mA). Выходное напряжение ИС в этом режиме работы составляет 0,1 – 0,4 В.

|

R1 |

R3 |

+5В14 |

|

R5 |

||

|

|

|

VT 4 |

|

VT1 |

|

VD3 |

|

|

|

|

1 |

|

VT 2 |

3 |

2 |

|

|

VT5 |

|

|

|

|

VD1 |

VD2 |

R4 |

|

R2 |

|

||

|

|

||

|

|

|

|

|

|

VT3 |

Общ 7 |

Рис.2.16. Принципиальная схема основного элемента интегральной схемы транзисторно-транзисторной логики

Если хотя бы на один вход многоэмиттерного транзистора VT1 подан низкий уровень напряжения Uвх0 (рис. 2.18), то соответствующий

переход база – эмиттер открывается и отбирает базовый ток транзистора VT2, который при этом закрывается. Это приводит к выключению транзисторов VT3 и VT5. Тогда открывается транзистор VT4, ток базы которого протекает через резистор R3. Открытый транзистор VT4 подключает к выходу схемы источник питания. Выходной потенциал микросхемы в этом случае высокий и для серии 155, например, не менее 2,4В. Транзистор VT4 с нагрузкой Rн образует эмиттерный повторитель, благода-

ря чему выход ИС является низкоомным и обладает высокой нагрузочной способностью.

Сведем возможные состояния ИС рис.2.16. в табл. 2.6. Таблица 2.6

Uвх1 |

Uвх2 |

Uвых |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

|

21 |

|

|

R1 |

|

R3 |

+5В14 |

|

Iб1 |

|

||

|

|

|

|

|

Uвх1 |

VT1 |

|

|

Uвых0 |

1 |

|

|

Iб5 |

|

2 |

|

VT 2 |

|

3 |

|

|

VT5 |

||

|

|

|

||

|

|

|

|

|

VD1 |

VD2 |

R4 |

|

|

R2 |

|

|||

|

|

|

|

|

|

|

I |

б3 |

VT3 |

|

|

|

||

Общ7

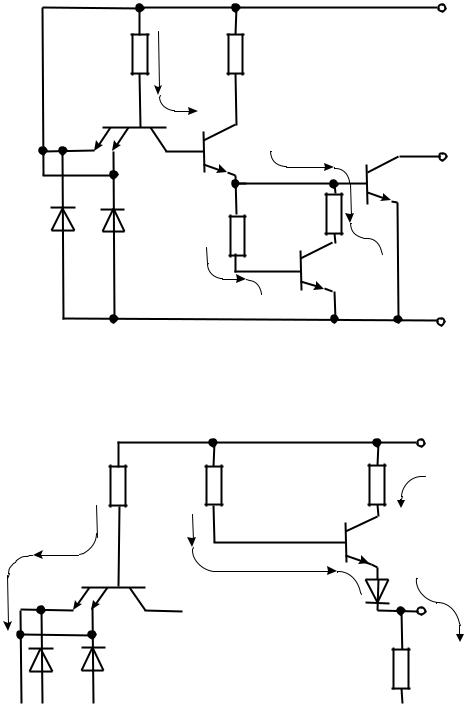

Рис. 2.17. Распределение токов и напряжений при высоком входном логическом уровне

Анализ состояний базового элемента ИС ТТЛ показывает, что он выполняет логическую функцию И-НЕ позитивной логики.

|

|

14 |

|

|

+5В |

R1 |

R3 |

R5 |

Iвх0 |

|

Iпот |

|

VT 4 |

|

VT1 |

|

Iвых |

1 |

Iб3 |

VD3 |

|

|

|

||

2 |

|

|

Uвых1 |

|

|

|

|

|

VD1 VD2 |

|

R нОбщ |

7

7

Рис. 2.18. Распределение токов и напряжений при низком входном логическом уровне

Большим недостатком схемы ТТЛ является то, что в момент ее переключения на короткое время открываются оба транзистора и VT4, и VT5 (рис. 2.16.). В этом случае потребление тока микросхемой ограничивается только защитным резистором R5. Импульс тока момента переключения вызывает высокочастотные помехи на шине питания. Поэто-

22

му правила эксплуатации рекомендуют микросхему шунтировать по цепи питания высокочастотным керамическим конденсатором развязки с емкостью 0,1мкФ и более.

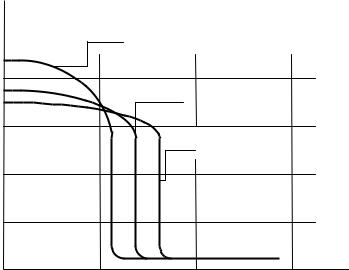

Передаточная характеристика ИС ТТЛ приведена на рис.2.19. Как следует из рисунка, низкий уровень выходного напряжения ИС не равен нулю, а высокий – меньше напряжения питания микросхемы (5В). ИС обладает усилительными свойствами с коэффициентом передачи около

10.

В Uвых

+125оС

4 + 25оС

3

−60оС

2

1

|

|

Uвх |

1 |

2 |

3 В |

Рис.2.19. Передаточные характеристики схемы ТТЛ для различных температур

Входной и выходной импульсы простейшего логического элемента И-НЕ (НЕ) интегральной схемы ТТЛ показаны во времени на рис.2.20. Как следует из рисунка, выходной импульс Uвых несколько

задержан относительно входного Uвых . Для элементов ТТЛ времена задержки распространения при включении t1зд.0.р и при выключении tзд0.1.р

определяются глубиной насыщения, в которое попадают при переключении импульсные транзисторы и емкостью входной и выходной цепей соединительных проводников микросхемы. Так влияние входной емкости определяется следующим образом: входной сигнал уже окончился, но выходной еще не нарастает (рис.2.20), поскольку необходимо время для стекания избыточного заряда во входной цепи. Собственные време-

на задержек логических элементов ИС серии 155 составляют: t1зд.0.р < 15нс , tзд0.1.р< 22нс и приводятся в паспортах данных микросхем.

23

Uвх

Uвх

2

Uвых |

t |

Uвых

2

1.0 |

0.1 |

|

t |

||

tзд.р |

|

tзд.р |

|

||

|

|

|

|

|

|

Рис. 2.20. Входной и выходной импульс схемы ТТЛ

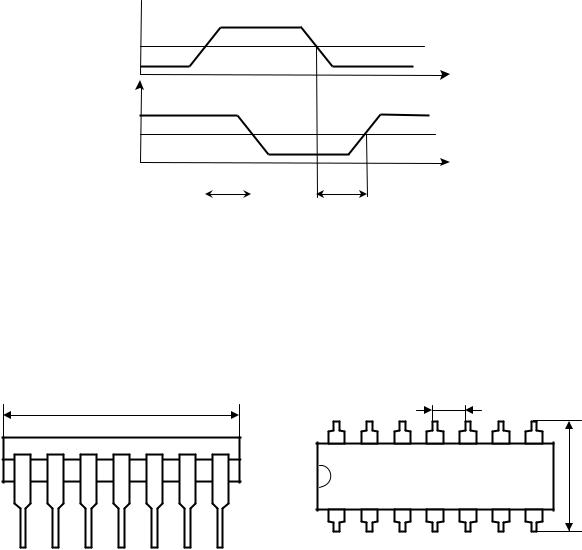

Промышленность выпускает интегральные схемы в пластмассовых, керамических или метало-керамическких корпусах. Один из вариантов корпуса ИС приведен на рис. 2.21. С одной из сторон корпуса микросхемы нанесен ключ, от которого против хода часовой стрелки отсчитываются номера выводов.

19,5 |

2,5 |

14 |

8 |

Зона |

7,5 |

ключа 1 |

7 |

Рис. 2.21. Вариант исполнения корпуса интегральной схемы

5. Синтез цифрового автомата

Произвести синтез цифрового автомата. Составить принципиальную схему цифрового автомата, соответствующего таблице истинности. Упростить схему цифрового автомата в соответствии с правилами преобразования логических схем. Составить цифровой автомат на элементах ТТЛ или КМОП логики. Привести диаграммы выходных и входных сигналов логической схемы. Исследовать упрощенную схему цифрового автомата в программной среде Electronics Workbench. Варианты заданий приведены в Приложении 1.

Составим таблицу истинности работы цифрового автомата (табл.

2.7).

24