- •И.А. Чернышев, А. Ю. Чернышев

- •ЭЛЕКТРОННАЯ, МИКРОПРОЦЕССОРНАЯ И ПРЕОБРАЗОВАТЕЛЬНАЯ ТЕХНИКА

- •Лабораторная работа №1

- •ОСЦИЛЛОГРАФИРОВАНИЕ В ЭЛЕКТРОННЫХ СХЕМАХ

- •Таблица 1.1

- •ИССЛЕДОВАНИЕ ЛОГИЧЕСКИХ СХЕМ

- •Таблица 2.1

- •Таблица 2.5

- •Таблица 2.7

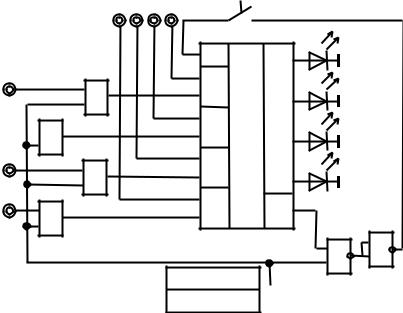

- •Рис. 2.25. Принципиальная схема

- •Таблица 2.8

- •Теория

- •Таблица 2.9

- •Таблица 2.10

- •Таблица 2.11

- •Приложение 1

- •Серия ТТЛ

- •Параметр

- •Адрес

- •Таблица 4.4

- •Таблица 5.1

- •Хранение

- •Таблица 5.4

- •Примечание

- •Лабораторная работа № 6

- •Таблица 6.2

- •Состояния выходов счетчика

- •Таблица 6.3

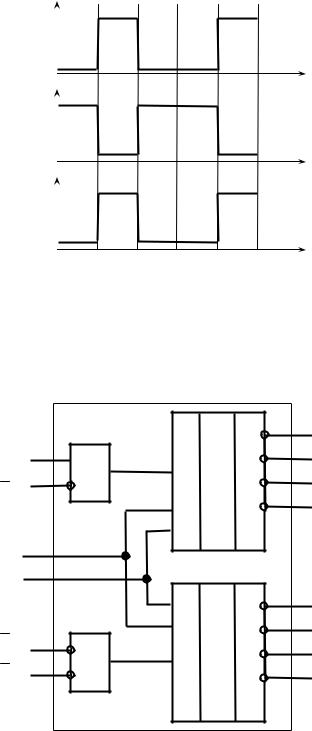

- •Рис. 7.5. Диаграммы напряжений параллельного режима работа

- •регистра К155ИР16

- •Таблица 7.1

- •Таблица 7.3

- •Рис.8.4.Диаграммы напряжений

- •Electronics Workbench

- •Лабораторная работа № 10

- •ЦИФРО-АНАЛОГОВЫЕ ПРЕОБРАЗОВАТЕЛИ

- •Рис.10.2. Простейшая схема ЦАП с суммированием весовых токов

- •3. Последовательные ЦАП с широтно-импульсной модуляцией

Приложение 3 Динамические параметры микросхем ТТЛ логики

Серия ТТЛ |

|

|

Параметр |

|

|

|

|||

Отечест- |

Зарубеж- |

Pср , |

tз0д,1.р , |

t1з,д0.р , |

Iвх0 , |

|

Iвх1 , |

Iвых0 , |

Iвых1 , |

венная |

ная |

мВ |

нс |

нс |

мА |

|

мА |

мА |

мА |

К155 |

74 |

10 |

20 |

14 |

1,6 |

|

0,04 |

16 |

0,4 |

К555 |

74LS |

2 |

18 |

12 |

0,4 |

|

0,02 |

8 |

0,4 |

К1533 |

74ALS |

1,2 |

14 |

10 |

0,2 |

|

0,01 |

8 |

0,4 |

Приложение 4 Соответствие наименований зарубежных и отечественных логиче-

ских элементов микросхем ТТЛ

74 , 74LS, 74S, |

K155, K555, K531 |

74 , 74LS, 74S, |

K155, K555, K531 |

|

74F, 74ALS |

K1531, K1533 |

74F, 74ALS |

K1531, K1533 |

|

NAND |

И - НЕ |

NOT |

НЕ |

|

74LS00 |

K555ЛА3 |

74ALS04 |

К1533ЛН1 |

|

7405 |

ЛН2 |

|||

7401 |

ЛА8 |

|||

7406 |

ЛН3 |

|||

7403 |

ЛА9 |

|||

7407 |

ЛН4 |

|||

7410 |

ЛА4 |

|||

7416 |

ЛН5 |

|||

7412 |

ЛА10 |

|||

|

|

|||

OR |

И - ИЛИНЕ |

|||

7420 |

ЛА1 |

|||

7422 |

ЛА7 |

7450 |

К155ЛР1 |

|

7426 |

ЛА11 |

|||

7451 |

ЛР11 |

|||

7430 |

ЛА2 |

|||

7453 |

ЛР3 |

|||

7437 |

ЛА12 |

|||

7454 |

ЛР13 |

|||

7440 |

ЛА6 |

|||

7455 |

ЛР4 |

|||

|

|

|||

|

|

|

|

|

NOR |

ИЛИ - НЕ |

AND |

И |

|

7402 |

ЛЕ1 |

7408 |

ЛИ1 |

|

7415 |

ЛИ4 |

|||

7423 |

ЛЕ2 |

7421 |

ЛИ6 |

|

7425 |

ЛЕ3 |

|

|

|

OR |

ИЛИ |

|||

7427 |

ЛЕ4 |

|||

|

|

|||

7428 |

ЛЕ5 |

7432 |

ЛЛ1 |

|

|

|

74136 |

ЛЛ3 |

38

Лабораторная работа №3

ИССЛЕДОВАНИЕ СУММАТОРОВ

Цель работы: изучить логические основы и особенности работы многоразрядных сумматоров, а также получить практические навыки работы с ними.

1.Общие положения

При создании цифровых автоматов и специализированных микро

– ЭВМ наряду с элементарными комбинационными логическими элементами широко используются типичные комбинационные схемы – сумматоры. Как правило, они выполнены с помощью интегральной технологии и представляют собой интегральные схемы средней степени интеграции.

Сумматор предназначен для выполнения операции арифметического сложения двух двоичных чисел. При сложении двух одноразрядных двоичных чисел А и В формируются двоичные значения суммы (S) и переноса (C). Работу логической схемы, реализующей операцию сложения, описывает таблица истинности 3.1.

|

|

|

|

|

Таблица 3.1 |

|

Вход |

|

Выход |

||

А |

|

В |

S |

|

C |

0 |

|

0 |

0 |

|

0 |

0 |

|

1 |

1 |

|

0 |

1 |

|

0 |

1 |

|

0 |

1 |

|

1 |

0 |

|

1 |

Значения суммы S и переноса C в табл. 3.1 совпадают соответственно со значениями функции ИСКЛЮЧАЮЩЕЕ ИЛИ и функции И и поэтому могут быть описаны следующими выражениями:

S = A |

B |

+ |

A B = A B, С = A B |

(3.1) |

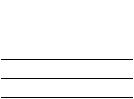

Логическая схема, реализующая обе указанные функции, называется полусумматором (рис. 3.1).

39

A |

=1 |

|

S |

&

C

B

Рис. 3.1. Полусумматор

С помощью полусумматора можно выполнить сложение лишь одноразрядных двоичных чисел. При сложении двоичных чисел, имеющих более одного разряда, полусумматор можно использовать только для одного младшего разряда, так как для старших разрядов необходимо учитывать значение переноса, поступающего из соседнего младшего разряда числа. Таким образом, в старших разрядах складываются не два, а три числа, поскольку может произойти перенос со следующего за ним младшего разряда. В общем случае для каждого разряда необходима логическая схема с тремя входами Ai , Bi , Ci и двумя выходами Si и

Ci+1 . Такая схема называется полным сумматором. Ее можно реализо-

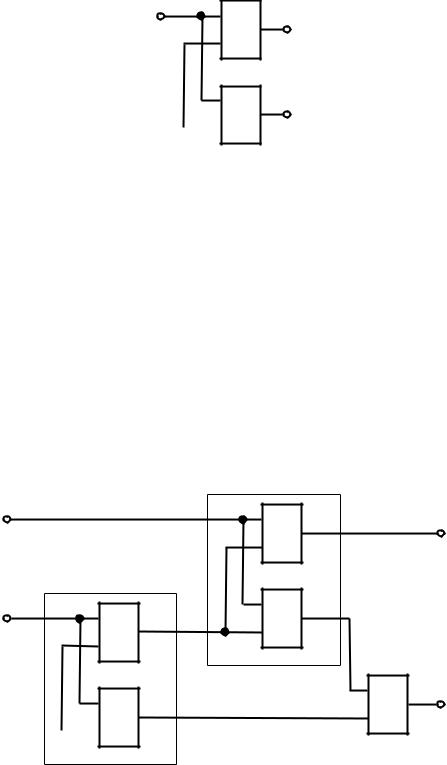

вать, например, с помощью двух полусумматоров, как показано на рис.3.2.

Pi |

=1 |

|

Si |

Ai |

=1 |

&

Bi

& |

1 |

Pi+1 |

|

Рис.3.2. Схема полного сумматора

40

Режим работы полного сумматора при сложении одного разряда двоичных чисел А и В представлен таблицей истинности 3.2, где Ci+1 –

перенос, формируемый в i-м разряде и поступающий в (i+1)-й разряд.

|

|

|

|

Таблица 3.2. |

|

|

Вход |

|

|

Выход |

|

Ci |

Ai |

Bi |

Si |

|

Ci+1 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

|

1 |

Для сложения двух многоразрядных двоичных чисел на каждый разряд необходим один полный сумматор. Только в младшем разряде можно обойтись полусумматором. На рис.3.3 приведена схема, предназначенная для сложения двух четырехразрядных чисел А и В. В ее младшем разряде также используется полный сумматор, чтобы иметь возможность наращивать разрядность схем.

|

A3 B3 |

|

A2 B2 |

|

A1 B1 |

|

A0 B0 |

|

C4 |

|

C3 |

|

C2 |

|

C1 |

|

C0 |

Сумматор |

Сумматор |

Сумматор |

Сумматор |

|||||

|

|

|

|

|

|

|

|

|

|

S 3 |

|

S2 |

|

S1 |

|

S 0 |

|

Рис. 3.3. Четырехразрядный сумматор с последовательным переносом

Четырехразрядные сумматоры, как правило, имеют по четыре входа для каждого слагаемого А и В, вход переноса из предыдущего разряда, четыре выхода суммы и выход переноса в следующий разряд. Промышленность выпускает такие сумматоры в интегральном исполнении, их представителями являются К155ИМ3, К155ИМ6, К555ИМ7 и др.

Сумматоры могут работать в двух режимах: в режиме сложения и в режиме вычитания многоразрядных двоичных чисел. В режиме сложения на вход переноса сумматора младшего разряда подается сигнал

41

логического нуля, а слагаемые – поразрядно соответственно на входы Ai и Bi . Полученная сумма

S = A + B |

(3.2) |

снимается с выходов Si с учетом информации на выходе переноса в следующий разряд – Ci +1 .

Режим вычитания двух многоразрядных чисел сводится к операции сложения операндов Ai и Bi . Действительно,

S = A −B = A +(F −B) −F. |

(3.3) |

При этом следует F выбирать таким образом, чтобы операция F −В(вычисление дополнения В до F), также как и вычитание F, проводилась без помощи специальных схем, реализующих вычитание. В

случае |

i-разрядных двоичных чисел |

Ai и |

Bi это возможно при |

F = 2i |

−1. В этом случае, выражение |

F − B |

называется поразрядным |

|

|

i |

|

дополнением Bi1. Поразрядное дополнение Bi1 получается путем инвертирования всех разрядов числа Bi . Справедливость этого утверждения

вытекает из того, что максимальное число, которое можно записать в двоичном i-разрядном коде равно

1111.... = 2i −1. (3.4)

Следовательно, вычитая из этой величины любое двоичное число Bi с целью определения его дополнения Bi1, мы получим тоже двоичное число, которое составляется путем инверсии всех разрядов Bi .

Рассмотрим операцию вычитания в случае поразрядного дополнения. При F = 2i −1 из выражения (3.3) следует, что

Ai − Bi = Ai +(2i −1− Bi ) −(2i −1) = Ai + Bi1 −2i +1 |

(3.5) |

Таким образом, вычитание можно осуществить, инвертируя число Bi , прибавляя еще одну единицу и вычитая 2i . Вычитание 2i достига-

ется весьма просто – путем инверсии разряда переноса. Для добавления 1 на свободный вход сигнала переноса младшего разряда С0 необходи-

42

мо подать единицу. При этом получается схема, представленная на рис. 3.4.

|

|

A3 B3 |

|

A2 B2 |

A1 B1 |

A0 B0 |

|||||||

|

|

|

1 |

|

1 |

|

1 |

|

1 |

|

|

||

|

C4 |

|

|

|

|

|

|

|

|

|

|

|

C0 |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

Четырехразрядный сумматор |

||||||||||

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

S 3 |

|

|

S 2 |

S1 |

S 0 |

||||||||

|

|

|

|||||||||||

|

|

|

|

||||||||||

|

Рис. 3.4. Вычисление разности двух четырехразрядных чисел |

||||||||||||

|

|

A − B = S ; C4 =1; |

V =0 при S ≥ 0 |

||||||||||

|

|

A − B = |

|

; C4 =0; |

V =1 при S < 0 |

||||||||

|

|

S |

|||||||||||

Рассмотрим теперь случай, когда искомая разность S отрицательна. При этом на выходе переноса C4 появится ноль, а на выходе V еди-

ница. Она может рассматриваться как отрицательный перенос - 2i (минус два в степени i). Поясним это на примере схемы рис.3.4. Таким образом, можно записать

Si =−2i + Zi .

При изменении порядка вычитания следует

Si = 2i − Zi

Введенное число Zi представляет собой точное двоичное допол-

нение (поразрядная инверсия) модуля разности. Знак числа укажет C4 = 0 или V =1. При продолжении арифметических операций такое

представление является весьма удобным.

Таким образом, общие правила вычитания можно сформулировать следующим образом:

- при вычитании из большего числа меньшего на вход Ai подается число в прямом коде, а на вход Bi – в инверсном. На вход C0 поступает

сигнал, соответствующий логической единице. То есть, производится суммирование кода числа Ai с дополнительным кодом числа Bi . Раз-

ность сигналов снимается с выхода Si в прямой форме, при этом на вы-

43

ходе C4 устанавливается значение логической единицы, а на выходе V –

логического нуля.

- при вычитания из меньшего числа большего, входные сигналы на информационные входы Ai и Bi подаются также как в первом слу-

чае, но на вход C0 подается сигнал соответствующий логическому нулю. Выходной сигнал снимается с Si в инверсной форме, а на выходе C4 устанавливается значение логического нуля, на выходе V – логиче-

ской единицы.

Таким образом, при вычитании многоразрядных двоичных чисел выход переноса в сумматор старшего разряда выступает как информационный выход, показывающий, какой из видов вычитания был выполнен в результате логических действий и в каком виде представлена выходная информация.

2. Задание и методика постановки исследования

Исследование работы сумматоров проводится на примере микросхемы К155ИМ3, представляющей собой полный четырехразрядный двоичный сумматор ТТЛ – логики. Принципиальная схема лабораторной установки представлена на рис. 3.5.

A0 A1A2 A3 |

|

SB1 |

|

B0

B1 DD1.2

=1

=1

B2

B3 DD1.4

=1 |

|

13 |

С0 |

S |

S0 |

9 |

|

DD1.1 |

10 |

|

|

|

|

|

A0 |

|

|

|

|

||

=1 |

11 |

B0 |

|

S1 |

6 |

|

|

|

|

|

|

||

|

8 |

|

|

|

|

|

|

A1 |

|

|

2 |

|

|

|

7 |

B1 |

|

S2 |

|

|

DD1.3 |

3 |

|

|

|

|

|

A2 |

|

|

|

|

||

=1 |

4 |

|

|

15 |

|

|

B2 |

|

S3 |

|

|||

|

1 |

|

|

|

|

|

|

A3 |

|

C4 |

14 |

|

|

|

16 |

B3 |

|

|

||

|

|

|

DD3.2 |

|||

|

|

|

|

DD3.1 |

||

|

|

|

DD2 |

|

||

|

|

|

|

& |

& |

|

|

|

|

|

|

|

|

|

0 сложение |

|

|

|

||

1вычитание  X1

X1

Рис. 3.5. Принципиальная схема лабораторной установки

44

Она содержит исследуемый сумматор К155ИМ3 и поразрядную световую индикацию состояния сумматора. Для получения необходимого логического уровня второго операнда Bi используется схема DD1

– ИСКЛЮЧАЮЩЕЕ ИЛИ, которая позволяет формировать прямой или дополнительный код четырехразрядного числа Bi , при подаче на второй

вход элементов DD1, соответственно, низкого или высокого логического уровня. Элементы DD3.1 и DD3.2 позволяют вычислить абсолютную величину и знак разности по методу циклического переноса.

2.1.Установите по вольтметру на пределе измерения 20В с помощью ручек настройки ГРУБО и ПЛАВНО источника питания V1 постоянное напряжение 5В и подключите его, соблюдая полярность, к соответствующим гнездам лабораторного стенда.

2.2.Начните исследование работы сумматора с операции сложения. Для этого подключите к гнезду Х1 низкий логический уровень, соединив гнездо с общим выводом источника питания. Подключив к входам Ai и Bi необходимые логические уровни, подайте два двоичных

четырехразрядных числа на информационные входы Ai и Bi суммато-

ра. Полученное состояние входов и выходов сумматора, отраженное светодиодами, запишите в таблицу 3.3.

Таблица 3.3

|

|

Код числа А |

|

|

|

|

Код числа В |

|

|

|

|||||||||||

А |

|

|

|

|

|

|

|

|

В |

|

|

|

|

|

|

|

|

||||

|

А3 |

А2 |

А1 |

А0 |

В3 |

В2 |

В1 |

|

В0 |

А+В |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

0 |

1 |

|

1 |

|

0 |

|

5 |

|

0 |

|

1 |

0 |

|

|

1 |

11 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

А-В |

6 |

0 |

1 |

|

1 |

|

0 |

|

5 |

|

0 |

|

1 |

0 |

|

|

1 |

1 |

||||

|

|

|

|

|

|

|

|

|

Код суммы А+В |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

Теория |

|

|

|

|

|

|

|

Эксперимент |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

S3 |

|

S2 |

|

|

S1 |

|

S0 |

C4 |

|

S3 |

|

S2 |

S1 |

|

S0 |

|

C4 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

1 |

|

0 |

|

|

1 |

|

|

1 |

0 |

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

Код разности А-В |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

0 |

|

0 |

|

|

0 |

|

|

1 |

1 |

|

|

|

|

|

|

|

|

|

|

||

2.3.Повторите пункт 2.2 для других произвольно заданных чисел, так чтобы результат суммирования превышал четырехразрядное число.

2.4.Подключите к гнезду Х1 высокий логический уровень. Иссле-

дуйте работу сумматора в режиме вычитания для случаев А>В и А<В. Результаты экспериментов занесите в таблицу 2.1.

45

2.5.Проанализируйте полученные данные и подтвердите их справедливость с помощью логических уравнений.

2.6.Повторите исследования работы сумматора в режиме вычита-

ния для случаев А>В и А<В, для режима циклического переноса, при замкнутой кнопке SB1.

3. Порядок выполнения работы в программной среде

Electronics Workbench

3.1.Ознакомиться с элементной базой и инструментальными средствами программы Electronics Workbench 5.12.

3.2.Исследуйте работу четырехразрядного сумматора, синтезированного на базе четырех одноразрядных сумматоров ТТЛ – серии интегральных микросхем в режимах сложения и вычитания. Для этого выберите из библиотеки Digital четыре полных сумматора. Нажав дважды левую клавишу мыши установите в карте Full – Adder Properties из библиотеки (Library) ttl – серию, модель (Model) LS. Нажмите клавишу ОК.

3.3.Соберите схему четырехразрядного сумматора и подключите

кего выводам формирователь логических уровней и анализатор логических сигналов.

3.4.Задаваясь операндами А и В исследуйте режимы сложения и вычитания. Результаты экспериментов занесите в таблицу 3.3.

3.5.Данные экспериментов выведите на лист бумаги с помощью принтера. При вызове команды Print в открывшемся окне появляется список атрибутов схемы и приборов, которые могут быть распечатаны. Выберете нужные Вам приборы, так чтобы рядом появился символ 9, а затем выполните команду Print.

Соответствие наименований зарубежных и отечественных микросхем сумматоров на элементах ТТЛ приведено в таблице 3.4.

|

|

|

Таблица 3.4 |

74, 74LS, 74S, |

K155, K555, |

74, 74LS, 74S, |

K155, K555, K531 |

74F, 74ALS |

K531 |

74F, 74ALS |

K1531, K1533 |

|

K1531, K1533 |

|

|

7480 |

ИМ1 |

74283 |

ИМ6 |

7482 |

ИМ2 |

74358 |

ИМ7 |

7483 |

ИМ3 |

74385 |

ИМ8 |

46

4. Содержание отчета

4.1.Цель работы.

4.2.Принципиальные схемы лабораторной установки в соответствии со стандартами.

4.3.Таблицы, диаграммы напряжений, комментарии и пояснения

кним.

4.4.Выводы о проделанной работе и полученных результатах.

4.5.Ответить на контрольные вопросы, указанные преподавате-

лем.

5.Контрольные вопросы

5.1.Чем отличается полный сумматор от полусумматора?

5.2.Какую функцию выполняют выходы сумматора Pi+1 и Si при

сложении и вычитании многоразрядных двоичных чисел?

5.3.Чем отличаются режим вычитания из большего – меньшего числа, от режима вычитания из меньшего – большего?

5.4.Как маркируются сумматоры, и какие их типы Вы знаете?

5.5.Поясните терминологию «Поразрядное дополнение числаBi1».

5.6.Какая схема называется полным сумматором?

5.7.В каких режимах работают сумматоры?

6.Литература

6.1.Браммер Ю. А. Цифровые устройства: учебное пособие для студентов вузов. - М.: Высшая школа, 2004. - 229 с.: ил.

6.2.Миловзоров О. В. Электроника. - М.: Высшая школа, 2004. -

288 с. : ил.

6.3.Мышляева И. М. Цифровая схемотехника: учебник. - М.:

Академия, 2005. - 400 с. : ил.

6.4.Титце У., Шенк К. Полупроводниковая схемотехника: Справочное руководство. Пер. с нем. -М.: Мир, 1982. -512 с., ил.

6.5.Шило В. Л. Популярные цифровые микросхемы: Справочник. -М.: Металлургия, 1988. -352 с.: ил.

47

Лабораторная работа №4

ИССЛЕДОВАНИЕ ДЕШИФРАТОРОВ

Цель работы: изучить особенности работы дешифраторов, а также получить практические навыки с ними.

1. Общие положения

Дешифратором называют комбинационную логическую схему, в которой каждой из комбинаций сигналов на входах соответствует сигнал только на одном из его выходов. Другими словами дешифраторы преобразуют двоичный код в напряжение логического уровня, появляющееся на том выходном проводе, десятичный номер которого соответствует двоичному коду. Остальные выходы в этом случае находятся либо в неактивном состоянии, либо в состоянии разомкнутой цепи (Z- состояние). Дешифраторы находят применение в управляющих системах для выдачи управляющих воздействий в те или иные цепи в зависимости от комбинации сигналов на входах. Дешифраторы различаются по емкости (2, 3 или 4 бита), по числу каналов (один или два), а также форматом входного кода (двоичный или двоично-десятичный).

Промышленность выпускает большой набор дешифраторов. Только в интегральном исполнении транзисторно-транзисторной логики (ТТЛ) выпускается 20 функционально отличных дешифраторов.

Простейший дешифратор, имеющий один вход и два выхода, представлен на рис. 4.1. Возможные состояния дешифратора сведены в табл. 4.1.

|

X |

|

DC |

Y 0 |

||

|

|

|

Y1 |

|||

|

|

|

|

|||

|

|

|

|

|

|

|

|

4.1. Простейший дешифратор |

|||||

|

|

|

|

|

Таблица 4.1. |

|

Вход |

|

|

|

Выход |

|

|

X |

|

Y 0 |

|

Y1 |

|

|

Н (0) |

|

В (1) |

|

Н (0) |

|

|

В (1) |

|

Н (0) |

|

В (1) |

|

|

Н - низкий логический уровень, В - высокий логический уровень.

48

Работу дешифратора можно также пояснить с помощью диаграмм напряжения, приведенных на рис.4.2. Активным уровнем дешифратора, приведенного на рис.4.1, является высокий логический уровень. У других типов дешифраторов активным уровнем может быть низкий логический уровень.

X

Y 0 |

t |

Y1 |

t |

|

t

Рис.4.2. Диаграммы напряжений простейшего дешифратора

2. Дешифраторы на микросхемах К155ИД4

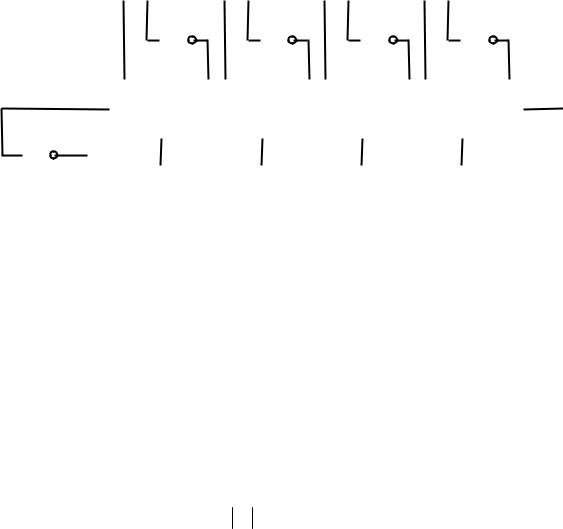

Микросхема К155ИД4 (рис.4.3) содержит сдвоенный дешифратор с двумя общими входами АО, А1 дешифруемого кода.

|

|

|

DC |

7 |

Y1 |

|

|

1 |

|

A |

6 |

||

Eа |

& |

Y2 |

||||

Y |

|

|||||

Eа |

2 |

Eа |

5 |

Y3 |

||

|

A1 |

|

4 |

Y4 |

||

|

|

|

|

|||

|

13 |

A0 |

|

|

|

|

A1 |

|

|

|

|

||

A0 |

3 |

|

|

|

|

|

|

|

|

9 |

|

||

|

|

A0 DC |

Y5 |

|||

|

|

A1 |

B |

10 |

||

Eb 14 |

Y6 |

|||||

& |

Y |

11 |

||||

Y7 |

||||||

Eb 15 |

Eb |

|

12 |

|||

|

Y8 |

|||||

Рис.4.3. Структурная схема дешифратора К155ИД4

49

Каждый из дешифраторов DCA и DCB имеет четыре выхода Y1 – Y4 и Y5 – Y8 соответственно и по два раздельных входа разрешения Ea ,

Ea и Eb , Eb . То есть, дешифратор DCA имеет прямой Ea и инверсный

Ea входы, а дешифратор DCB - только инверсные входы дешифрации

Eb .

Состояния для дешифратора DCA при дешифрации кода А1, А0 сведены в табл. 4.2.

Таблица 4.2.

|

|

|

Вход |

|

|

|

|

Выход |

|

||

|

Адрес |

Разрешение |

|

|

|

||||||

|

|

|

|

|

|

||||||

А1 |

|

А0 |

Ea |

|

Ea |

|

Y1 |

Y 2 |

|

Y 3 |

Y 4 |

Х |

|

Х |

В |

|

Х |

В |

В |

|

В |

В |

|

Н |

|

Н |

Н |

|

В |

Н |

В |

|

В |

В |

|

Н |

|

В |

Н |

|

В |

В |

Н |

|

В |

В |

|

В |

|

Н |

Н |

|

В |

В |

В |

|

Н |

В |

|

В |

|

В |

Н |

|

В |

В |

В |

|

В |

Н |

|

В |

|

Х |

Х |

|

Н |

В |

В |

|

В |

В |

|

Х - безразличное состояние.

Активным уровнем на выходе дешифратора является низкий логический уровень. Как следует из табл.4.2, разрешение дешифрации наступает при низком логическом уровне на входе Ea и высоком на входе

Ea .

Разрешение дешифрации для дешифратора DCB наступает при

подаче высокого логического уровня на входы 14 и 15 Eb .

Интегральная схема К155ИД4 может работать и как дешифратор трехразрядного кода на восемь выходов (Рис. 4.4). Для дешифрации

трехразрядного кода следует соединить Ea и Eb (адресный вход А2) и

Ea и Eb (вход разрешения С) (рис.4.5). Состояния дешифратора в этом

режиме сведены в табл.4.3.

Как следует из табл.4.3 разрешение дешифрации происходит только при низком уровне на входе С (выводы 14 и 2). Анализ таблиц 4.2 и 4.3 показывает, что при низком логическом уровне на входе А2 разрешена дешифрация на верхних четырех выходах (Y1 – Y4) дешифратора, нижние четыре выхода (Y5 – Y8) в этом случае блокированы

низким сигналом по входу 15 ( Eb ) и на них поддерживается высокий логический уровень.

50