Метод.ук.ЛБ_Схемотехника

.pdfМИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РФ Государственное образовательное учреждение высшего профессионального образования

Национальный исследовательский Томский политехнический университет

«УТВЕРЖДАЮ» Зам. директора ИК по УР

________ С.А. Гайворонский

«____»_____________2011 г.

СХЕМОТЕХНИКА ЭВМ

Методические указания к выполнению цикла лабораторных работ по курсу «Схемотехника ЭВМ»

для студентов, обучающихся по направлению

230100 «Информатика и вычислительная техника»

Томск – 2011 г.

УДК 004.4(076.5)

ББК 32.973.202-018.2я73

М216

Схемотехника ЭВМ: методические указания к выполнению цикла лабораторных работ по курсу «Схемотехника ЭВМ» для студентов, обучающихся направлению 230100 «Информатика и вычислительная техника». – 47 с.

Авторы: |

Мальчуков А.Н. |

|

Цыганков Ю.В. |

Составитель: |

Еремин В.В. |

Рецензент: к.т.н., доцент кафедры ВТ Осокин А.Н.

Методические указания рекомендованы к использованию в учебном процессе методическим семинаром кафедры вычислительной техники

2011 г.

Зав. кафедрой, д.т.н., профессор |

Марков Н.Г. |

2

Лабораторная работа №1.

«Изучение пакета NI Multisim 9.0»

Цель работы: изучить основные инструменты Multisim 9.0 и научиться моделировать в нем работу электрических схем.

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

Multisim - это интерактивный эмулятор электрических схем.

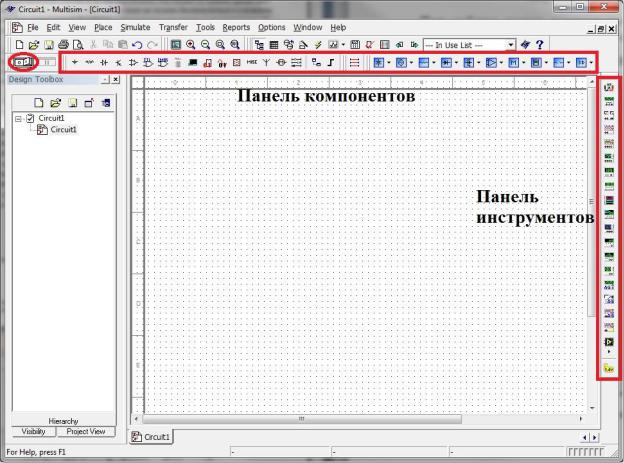

Рисунок 1. Главное окно Multisim

Для построения схемы необходимо нажать левой кнопкой мыши на один из элементов панели компонентов, подтвердить свой выбор в окне выбора компонента нажатием кнопки OK (рисунок 2), и поместить его на

рабочую область. |

|

Для примера реализуем функцию |

. Сначала |

строим таблицу функционирования (см. таблицу 1). |

|

3

Таблица 1.

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

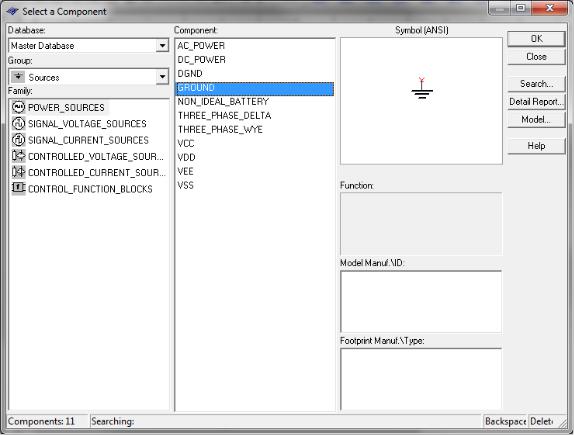

Выбираем Ground или DGND (рисунок 2). Затем выбираем CLOCK_VOLTAGE для генерации значений входных переменных. Таких элементов нам необходимо 3, для каждого в параметрах указываем различную частоту генерируемого сигнала, например 1, 2 и 4 кГц. Это необходимо, чтобы получить наглядные диаграммы работы.

Рисунок 2. Окно выбора компонента Ground

4

Рисунок 3. Окно выбора компонента CLOCK_VOLTAGE

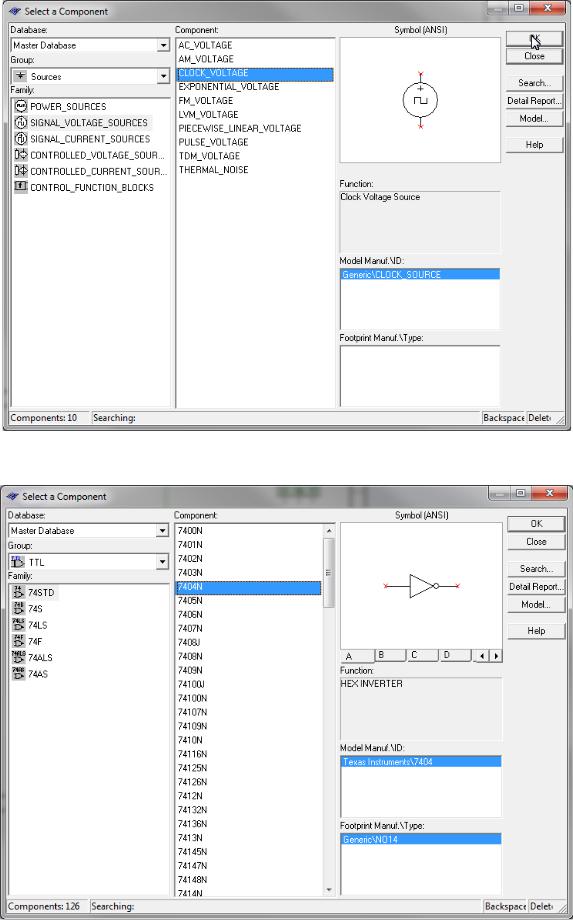

Рисунок 4. Окно выбора компонента NOT

5

Рисунок 5. Окно выбора компонента 3AND

Рисунок 6. Окно выбора компонента 3AND

6

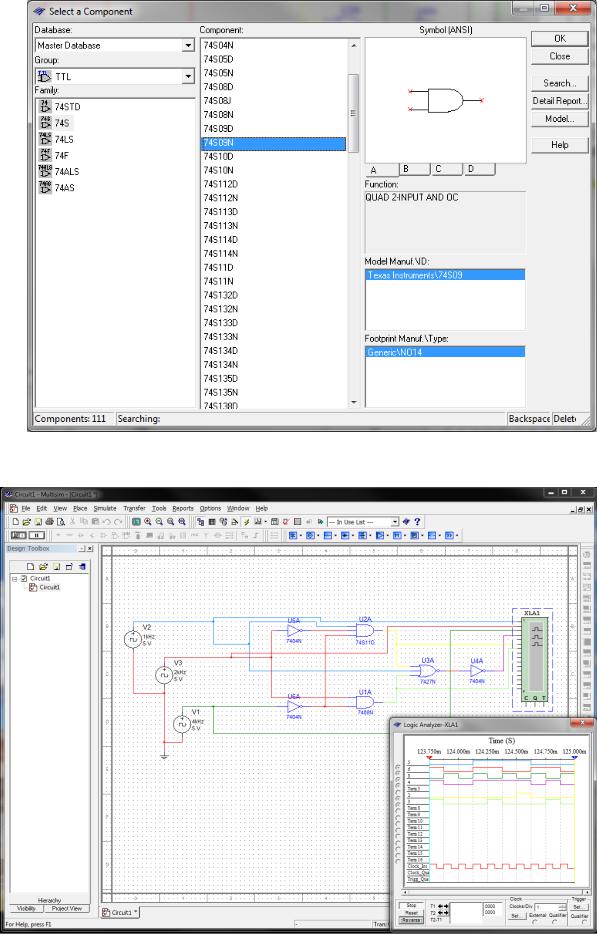

После размещения и соединения всех элементов необходимо добавить в схему логический анализатор сигналов (Logic Analyzer). Его можно найти на панели инструментов справа. К его входам подключаются выход функции f и выходы каждой из конъюнкций.

Для наглядности графиков сделаем их разного цвета. Для этого правой кнопкой мыши выбираем проводник, подходящий к одному из входов логического анализатора (Logic Analyzer), и выбираем в появившемся меню Wire Color, где можно выбрать для него любой цвет.

Для запуска/остановки симуляции необходимо нажать F5. Для паузы нажать F6. Всю схему в сборе с результатами моделирования можно увидеть на рисунке 6.

ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

1. В соответствии со своим вариантом возьмите функцию в таблице 2.

|

Таблица 2. Функции для построения схемы |

|

|

|

|

Вариант № |

Функция |

|

1 |

|

|

2 |

|

|

3 |

|

|

4 |

|

|

5 |

|

|

6 |

|

|

7 |

|

|

8 |

|

|

9 |

|

|

10 |

|

|

11 |

|

|

12 |

|

|

13 |

|

|

14 |

|

|

15 |

|

|

16 |

|

|

17 |

|

|

18 |

|

|

19 |

|

|

20 |

|

|

21 |

|

|

22 |

|

|

23 |

|

|

24 |

|

|

|

7 |

|

2.Соберите схему по аналогии с примером в методических указаниях.

3.Промоделируйте работу схемы и посмотрите результаты с помощью прибора Logic Analyzer (на панели инструментов, см. рисунок 1).

СОДЕРЖАНИЕ ОТЧЕТА

Отчет по лабораторной работе должен содержать следующее:

1)цель работы;

2)постановку задачи;

3)исходную функцию без упрощений;

4)принципиальную схему из редактора Multisim, реализующую данную функцию без упрощений;

5)таблицу функционирования функции;

6) результаты моделирования работы схемы с диаграммами работы из Logic Analyzer;

7) выводы.

Лабораторная работа №2.

«Изучение базовых элементов ИС ТТЛ, ТТЛШ и КМОП»

Цель работы: получить знания о строении логических элементов различных серий.

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

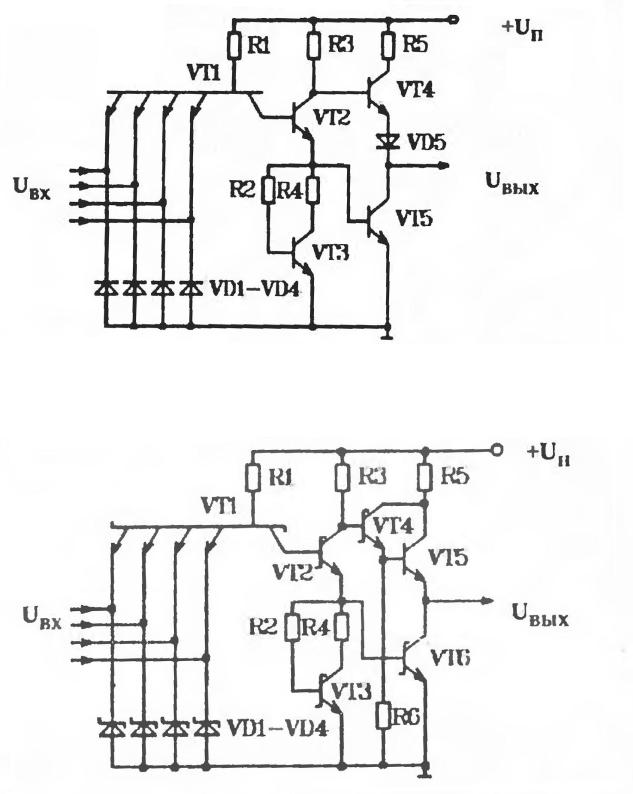

Классической структурой ТТЛ является схема базового вентиля И-НЕ серии 155. На схеме (рисунок 1) входной каскад построен на многоэмиттерном транзисторе VT1, который реализует функцию И. Антизвонные диоды VD1-VD4 защищают от отрицательного входного напряжения транзистор VT1. Далее следует фазоинверсный каскад на VT2 с источником тока на VT3. Выходной каскад построен на транзисторах VT4 и VT5. Диод VD5 предотвращает одновременное открытие этих транзисторов, что вызывает бросок тока.

8

Рисунок 1. Базовый элемент 155 серии

Рисунок 2. Базовый элемент серий К530/531

9

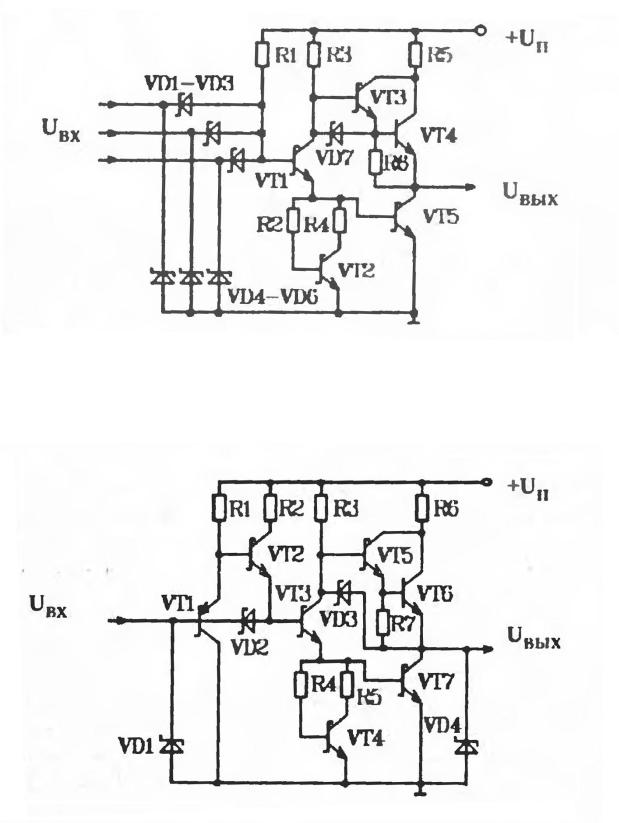

Рисунок 3. Базовый элемент серий К533/555

Рисунок 4. Базовый элемент серий К1533

10