- •1. Лабораторні роботи

- •1.1 Лабораторна робота №1

- •1.2 Лабораторна робота №2

- •1.3 Лабораторна робота №3

- •1.4 Лабораторна робота №4

- •1.5 Лабораторна робота №5

- •1.6 Лабораторна робота №6

- •1.7 Лабораторна робота №7

- •1.8 Лабораторна робота №8

- •Контрольні питання

- •2 Рекомендації до виконання завдань практичних занять

1.3 Лабораторна робота №3

ДОСЛІДЖЕННЯ ФУНКЦІОНУВАННЯ КОНТРОЛЕРІВ ПДП І ПЕРЕРИВАНЬ СЕРІЇ КР580

1.3.1 Контролер ПДП КР580ВТ57.

М

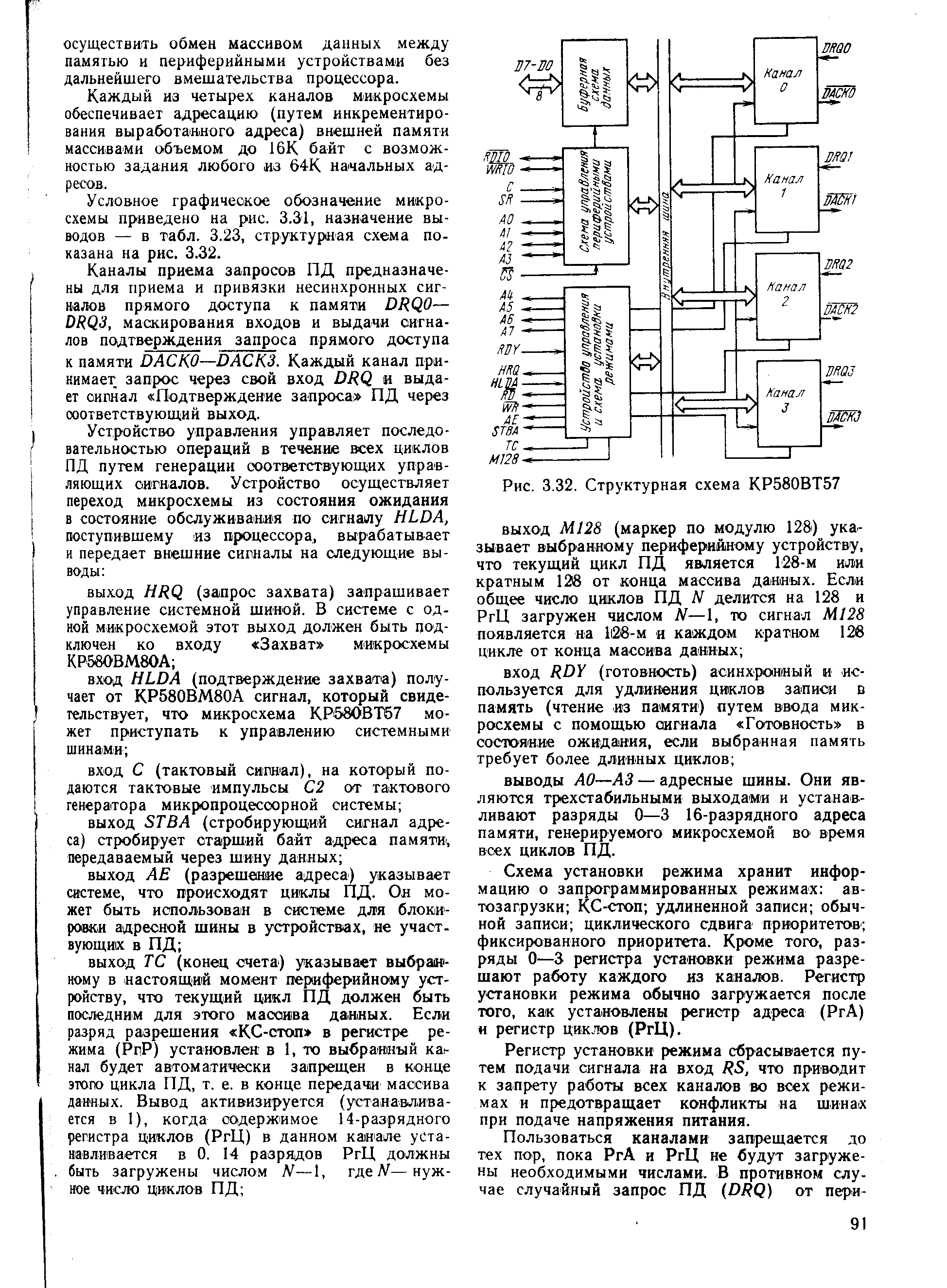

Рисунок 3.1 - Структурна схема КР580ВТ57

Пристрої, що запитують режим ПДП подають сигнали запитів на входи мікросхеми DRQ0 - DRQ3. При надходженні більше одного запитів обслуговується пристрій з найвищим пріоритетом. Пріоритет установлюється програмно. Можливі два режими установки пріоритету: фіксований, коли канал 0 має найвищий пріоритет, а канал 3 - найнижчий , і циклічне зрушення пріоритету, коли після кожного циклу пріоритет змінюється. При надходженні запиту на ПДП пристрій керування формує сигнал HRQ "Запит захоплення", що запитує центральний процесор про можливості використання системної шини для організації ПДП. При надходженні від ЦП дозволу на користування системною шиною HLDA схема прийому запитів формує сигнал DAС0 - DAС3, що підтверджує відповідному периферійному пристрою можливість ПДП.

1 .3.2

Контролер переривань КР580ВН59.

.3.2

Контролер переривань КР580ВН59.

Мікросхема КР580ВН59 - програмований контролер переривань (ПКП), обслуговує до восьми запитів на переривання мікропроцесора, що надходять від зовнішніх пристроїв.

М

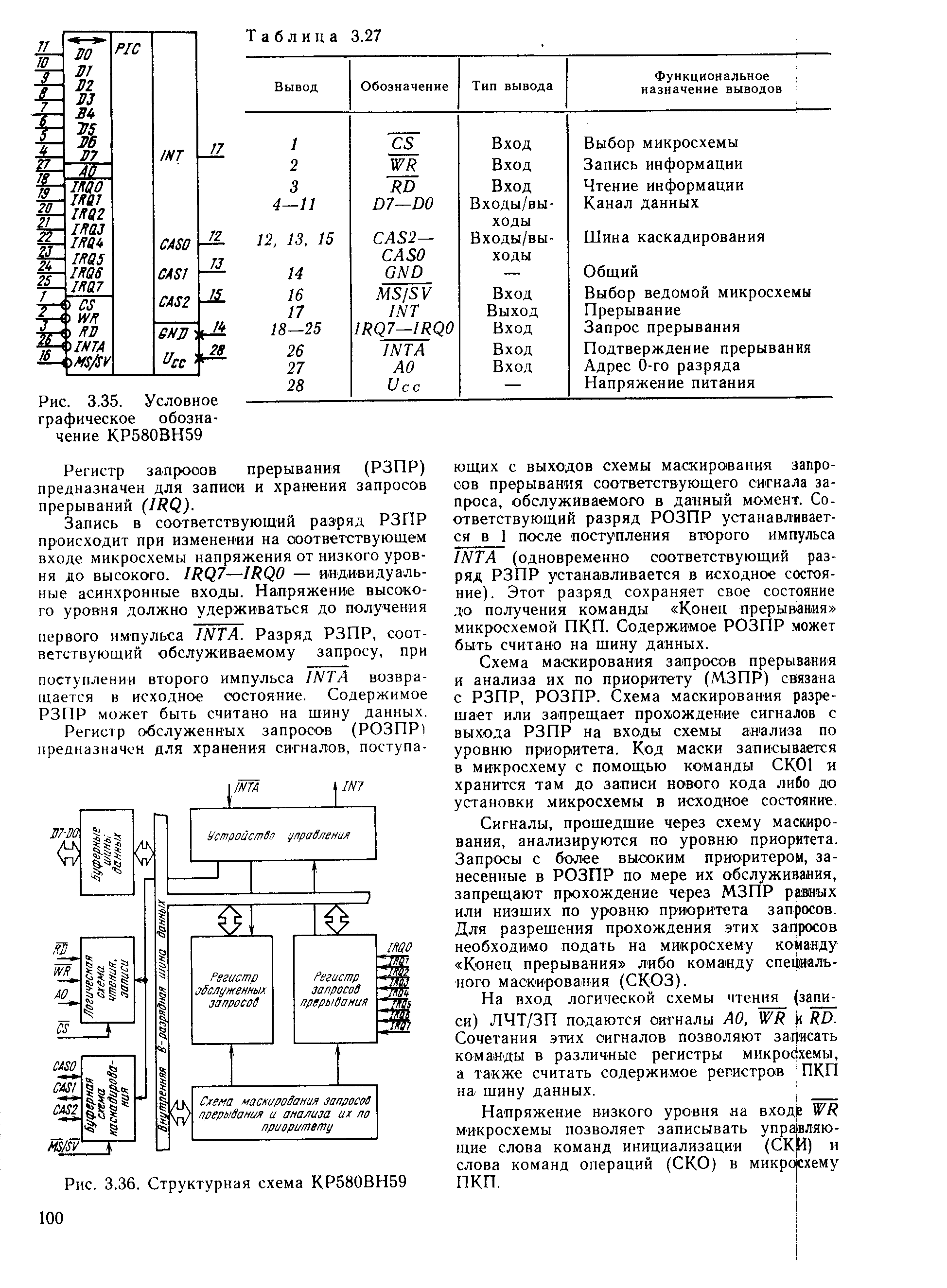

Рисунок 3.2 - Структурна схема КР580ВН59

Рисунок 3.2 - Структурна схема КР580ВН59

схема КР580ВН59

У мікросхемі передбачена можливість розширення числа запитів, що обслуговують до 64 шляхом каскадного з'єднання мікросхем ПКП. Структурна схема мікросхеми КР580ВН59 показана на рис. 3.2. Регістр запитів переривання (РЗПР) призначений для запису й зберігання запитів переривань.

Запис у відповідний розряд

РЗПР відбувається при зміні на вході

мікросхеми напруги від низького рівня

до високого ІRQ7 - ІRQ0 - індивідуальні

асинхронні входи. Напруга високого

рівня повинна втримуватися до одержання

першого імпульсу ![]() .

Розряд РЗПР, що відповідає запиту який

обслуговується, при надходженні другого

імпульсу

.

Розряд РЗПР, що відповідає запиту який

обслуговується, при надходженні другого

імпульсу ![]() повертається у початковий стан. Зміст

РЗПР може бути виданий на шину даних.

повертається у початковий стан. Зміст

РЗПР може бути виданий на шину даних.

Регістр РОЗПР призначений для зберігання незамаскованого запиту.

Схема маскування запитів переривання та аналізу їх по пріоритету (МЗПР) пов'язана із РЗПР, РОЗПР. Схема МЗПР дозволяє або забороняє проходження сигналів з РЗПР на входи схеми аналізу за рівнем пріоритету. Код маски записується в мікросхему за допомогою команди СКО1 (слово 1 команди операції) і зберігається там до запису нового коду або до установки мікросхеми у вихідний стан.

КОНТРОЛЬНІ ПИТАННЯ

1. Призначення мікросхеми КР580ВТ57 та її виводів.

2. Назвіть умови при яких виводи ІO/RD та ІO/WR мікросхеми являються входами, і при яких - виходами.

3. Призначення сигналів АЕ та ALE, куди й коли вони подаються.

4. Описати процес роботи контролера ПДП.

5. Що таке режим автозавантаження і які при цьому регістри задіяні.

6. Де в процесі ПДП зберігаються старші 8 біт адреси.

7. Який максимальний обсяг даних може бути переданий без перепрограмування контролера ПДП.

8. Які пріоритети задаються мікросхемі КР580ВТ57.

9. Призначення мікросхеми КР580ВН59 і призначення її виводів.

10. Яке максимальне число об'єктів може обслужити одна КР580ВН59.

11. Яке максимальне число об'єктів можна обслужити використовуючи каскадне з'єднання КР580ВН59.

12. Які виводи використовуються при каскадному з'єднанні, призначення цих виводів.

13. Способи завдання пріоритетів, їхні види й відмінності.

14. Описати процеси, які відбуваються в системі з каскадним з'єднанням після приходу першого, другого та третього ІNTA і які дії виконують провідна та підключена до неї мікросхеми.

15. Яким способом мікросхемі вказується, буде вона провідною чи тією, що підключається до провідної.

16. Режими роботи КР580ВН59.