микросхемотехника

.pdf

20

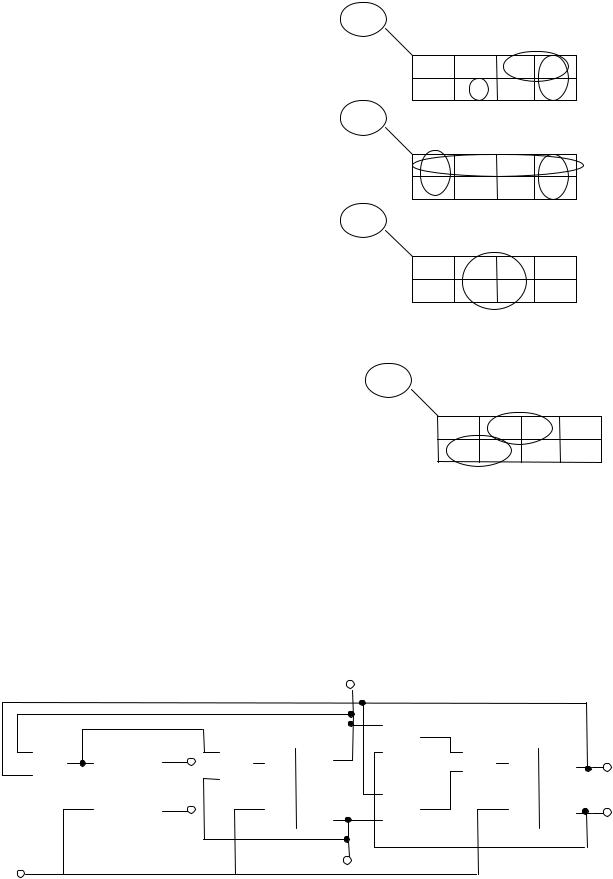

Рис. 3.1. Блок-схема реализации одиночного разряда логического автомата с памятью

|

X |

i |

= |

Ψ |

1i |

( A ,..., A |

,Q n ), |

|

|||

|

|

|

|

|

1 |

m |

i |

(3.1) |

|||

|

Y |

|

|

|

|

|

( A ,..., A |

,Q n ), |

|||

|

i |

|

= |

Ψ |

2i |

|

|||||

|

|

|

|

|

|

1 |

m |

i |

|

||

Заметим, что СУ являются схемами К-типа.

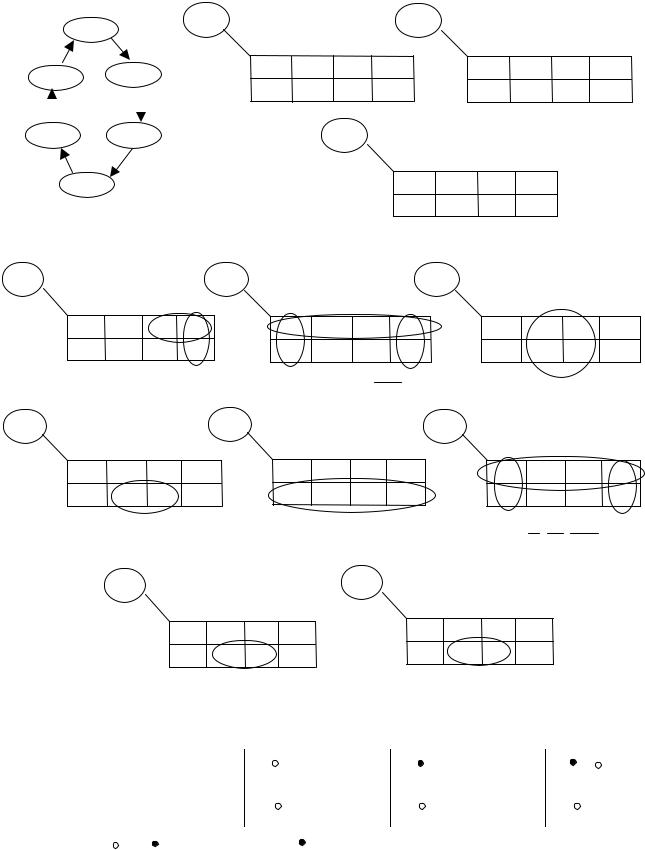

Для примера рассмотрим реализацию трехразрядного кольцевого счетчика (устройство, регистрирующее количество импульсов, поступивших на его вход), вырабатывающего последовательность двоичных эквивалентов чисел 1,2,3,5,6,7. Согласно приведенной на рис. 3.2 таблице состояний (а) и соответствующих карт минтермов (б) система прикладных уравнений будет иметь вид

An+ 1 |

= |

|

|

|

|

|

|

+ |

ABC ] n = [ g1A A + g2 A |

|

] n ; |

g1A = |

|

|

|

; g2 A = BC ; |

||||||

|

|

|

|

|

|

|

|

BC |

||||||||||||||

[ AB |

+ AC |

A |

||||||||||||||||||||

B n+ 1 = [ |

|

+ |

|

] n = [ g1B B + g2B |

|

] n ; |

g1B = |

|

; |

g2B = |

1; |

|||||||||||

B |

C |

B |

C |

|||||||||||||||||||

C n+ 1 = |

[ B ] n = [ g1C C + g2C |

|

] n ; |

g1C = B; |

g2C = |

B. |

||||||||||||||||

C |

||||||||||||||||||||||

Или в обобщенной форме |

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

Qn+1=[g1Q+g2 Q]n, |

|

|

|

|

|

(3.2) |

|||||

т.е. для построения каждого разряда рассматриваемого счетчика необходим запоминающий ЛЭ. Выбирая в качестве такого ЛЭ, например, Т-триггер с

Qn+1=[T Q+ TQ]n; |

(3.3) |

в результате совместного решения прикладного (3.2) и характеристического (3.3) уравнений (рис. 3.2,в) получаем обобщенное уравнение входов Т-триггеров

T= g1Q+g2 Q, |

(3.4) |

из которого поразрядные уравнения входов

TA=BC; |

TB= B+BC; |

TC=B C+ BC=B C. |

(3.4) |

Соответствующая структурная схема проектируемого счетчика представлена на рис. 3.2,г.

Из рассмотренной процедуры видно, что для перехода к другому типу триггера все операции необходимо повторить сначала, т.е. традиционный метод громоздок, плохо поддается автоматизации и затрудняет параллельный обзор вариантов. Указанные недостатки в значительной степени устраняются, если для проектирования использовать разностные карты минтермов, в клетки которых заносятся символы переходов fq выходных переменных, обозначаемых α при переходе 0→ 1, β - при переходе 1→ 0, а также 0 или 1, если при смене такта значения выходной функции остаются неизменными.

21

а) |

|

|

|

|

|

б) |

An+1 |

An Bn |

|

|

||||

|

|

|

|

|

Сn |

00 |

01 |

11 |

10 |

|||||

|

|

|

|

|

|

|

|

0 |

|

|

× |

|

1 |

× |

|

|

|

|

|

|

|

|

1 |

|

|

|

1 |

|

1 |

|

|

Такт n |

|

Такт (n+1) |

|

|

|

|

|

|||||

|

|

|

|

Bn+1 |

|

|

|

|

|

|

||||

|

An |

Bn |

Cn |

An+1 |

Bn+1 |

Сn+1 |

|

An Bn |

|

|

||||

|

0 |

0 |

1 |

0 |

1 |

0 |

|

Сn |

00 |

01 |

11 |

10 |

||

|

0 |

1 |

0 |

0 |

1 |

1 |

|

0 |

|

|

× |

1 |

1 |

× |

|

0 |

1 |

1 |

1 |

0 |

1 |

|

1 |

|

|

1 |

|

1 |

|

|

1 |

0 |

1 |

1 |

1 |

0 |

|

|

|

|

||||

|

|

Сn+1 |

|

|

|

|

|

|

||||||

|

1 |

1 |

0 |

1 |

1 |

1 |

|

A |

n |

B |

n |

|

|

|

|

1 |

1 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

||

|

|

Сn |

00 |

01 |

11 |

10 |

||||||||

|

0 |

0 |

0 |

Избыточные |

|

|||||||||

|

|

0 |

|

|

× |

1 |

1 |

× |

||||||

|

1 |

0 |

0 |

комбинации |

|

|

|

|||||||

|

|

1 |

|

|

|

1 |

1 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

в) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Tn |

g1g2 |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Qn |

|

00 |

|

01 |

11 10 |

|

||

|

g`1 |

g`2 |

|

|

Qn |

Qn+1 |

|

[T Q+ TQ]n=Qn+1 |

Tn |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

1 |

|

|

|

|

0 |

0 |

|

0 |

|

0 |

|

Tn• 1+ Tn• 0=0 |

0 |

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

1 |

1 |

1 |

|

|

|

||||||||||||||

|

0 |

0 |

|

1 |

|

0 |

|

Tn• 0+ Tn• 1=0 |

1 |

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

0 |

1 |

|

0 |

|

1 |

|

Tn• 1+ Tn• 0=1 |

1 |

|

|

|

T= g1Q+g2 Q |

|

||||||||||||

|

0 |

1 |

|

1 |

|

0 |

|

Tn• 0+ Tn• 1=0 |

1 |

|

|

|

|

|||||||||||||

|

1 |

0 |

|

0 |

|

0 |

|

Tn• 1+ Tn• 0=0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

1 |

0 |

|

1 |

|

1 |

|

Tn• 0+ Tn• 1=1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

1 |

1 |

|

0 |

|

1 |

|

Tn• 1+ Tn• 0=1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

1 |

1 |

|

1 |

|

1 |

|

Tn• 0+ Tn• 1=1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

||||||

г) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

C |

|

|

|

|

|

|

|

TA |

T |

|

A |

TA |

T |

|

|

|

|

|

|

TA T |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сp |

|

|

A |

|

|

Сp |

|

|

|

& |

|

|

|

|

|

Сp |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Рис. 3.2. Синтез структурной схемы кольцевого счетчика 1,2,3,5,6,7

22

в характеристическом Т-базисе

22

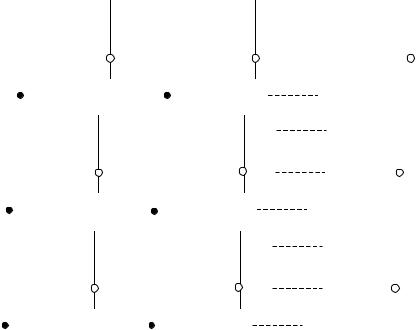

3.2. Метод словарных преобразований разностных карт минтермов

Суть метода заключается в упрощении трудоемкой процедуры решения системы логических уравнений (прикладного и характеристического) для получения уравнения входов. Для этого прикладные уравнения записываются в виде разностных карт минтермов, где разностные символы fq играют роль промежуточной переменной, устранение которой с помощью словаря характеристических базисов (табл. 3.2, рис. 3.3) позволяет сразу получать уравнения входов.

J |

K |

Qn |

Qn+1 |

fq |

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

fq |

J |

K |

||||||

0 |

0 |

1 |

1 |

1 |

|

||||

|

0 |

0 |

× |

||||||

0 |

1 |

0 |

0 |

0 |

|

||||

1 |

× |

0 |

|||||||

0 |

1 |

1 |

0 |

β |

|||||

α |

1 |

× |

|||||||

1 |

0 |

0 |

1 |

α |

|

β |

× |

1 |

|

1 |

0 |

1 |

1 |

1 |

|

||||

1 |

1 |

0 |

1 |

α |

|

|

|

|

|

1 |

1 |

1 |

0 |

β |

|

|

|

|

Рис. 3.3. Образование словаря переходов JK-триггера

Например, использование метода словарных преобразований для проектирования рассмотренного ранее (рис. 3.2) кольцевого счетчика 1, 2, 3, 5, 6, 7 позволяет получить гораздо более оптимальную его структуру (рис. 3.4, а - граф последовательности смены состояний; б - прикладные уравнения в виде разностных карт мимнтермов; в - обзор ва-

Таблица 3.2

fq |

|

|

|

Характеристический базис |

|

|

|

|

|||

D |

T |

|

RS |

JK |

|

|

DV |

||||

|

R |

|

S |

J |

|

K |

D |

|

V |

||

|

|

|

|

|

|

||||||

0 |

0 |

0 |

× |

|

0 |

0 |

|

× |

× |

|

0 |

|

|

0 |

|

× |

|||||||

|

|

|

|

|

|

|

|

|

|

||

1 |

1 |

0 |

0 |

|

× |

× |

|

0 |

× |

|

0 |

|

|

1 |

|

× |

|||||||

|

|

|

|

|

|

|

|

|

|

||

α |

1 |

1 |

0 |

|

1 |

1 |

|

× |

1 |

|

1 |

β |

0 |

1 |

1 |

|

0 |

× |

|

1 |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

риантов уравнений входов для различных триггеров; г - структурная схема). Заметим, что при проектировании П-устройств в произвольной элементной базе вначале проверяют целесообразность применения одновходовых триггеров, а затем двухвходовых (обычно JK-триггера, как наиболее универсального).

3.3. Многоразрядные субсистемы на основе регистров сдвига

Весьма эффективным при построении логических устройств П-типа является использование ИС регистров сдвига (РС) ввиду простоты их внутренней структуры и

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а) |

|

|

|

0α β |

|

б) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

001 |

|

|

An+1 |

|

An Bn |

|

|

|

|

Bn+1 |

|

|

An Bn |

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

01 11 10 |

||||||||||||||||||||||||

ββ 1 |

|

|

|

|

|

01α |

|

|

|

С |

n |

|

|

00 |

|

01 11 10 |

С |

n |

00 |

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

0 |

|

|

× |

|

0 |

|

1 |

× |

|

0 |

|

× |

|

1 |

|

|

1 |

× |

|||||||||||||

111 |

|

|

010 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

1 |

|

|

0 |

|

α |

|

β |

1 |

|

|

1 |

|

α |

β |

β |

α |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

11α |

|

|

|

|

|

|

|

α |

β |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

110 |

|

|

011 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Сn+1 |

An Bn |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Сn |

00 |

|

01 |

|

11 |

10 |

|

|

|

|

|

|

|||||

|

|

101 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

× |

|

|

α |

α |

× |

|

|

|

|

|

|

||||||

|

|

|

1α |

β |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

β |

|

|

1 |

|

1 |

β |

|

|

|

|

||||||||

в) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DA |

A B |

|

|

|

|

|

|

|

|

DB |

|

|

A B |

|

|

|

|

|

DС |

|

|

A B |

|

|

|

|

|

|

|

||||||||||

С |

00 01 11 10 |

|

С |

|

|

00 |

|

01 11 10 |

|

С |

00 |

01 11 10 |

|||||||||||||||||||||||||||

0 × |

|

|

|

|

|

1 |

× |

|

|

|

|

|

0 |

|

× |

|

1 1 |

× |

|

|

0 |

|

× |

1 1 |

× |

||||||||||||||

1 |

|

|

1 |

|

|

1 |

|

|

|

|

1 |

|

1 |

|

|

|

1 |

|

|

1 |

|

|

|

1 |

1 |

|

|||||||||||||

|

|

DA=A C+A B+ ABC |

|

|

|

|

DB= |

B+ C=BC |

|

|

|

|

|

|

|

DC=B |

|

||||||||||||||||||||||

TA |

A B |

|

|

|

|

|

|

|

|

TB |

|

|

A B |

|

|

|

|

|

TС |

A B |

|

|

|

|

|

|

|

||||||||||||

С |

00 01 11 10 |

|

С |

00 01 11 10 |

|

|

С |

00 01 11 10 |

|||||||||||||||||||||||||||||||

0 |

× |

|

|

|

|

|

|

× |

|

|

|

|

0 |

|

× |

|

|

|

× |

|

|

0 |

× |

1 |

1 |

× |

|||||||||||||

1 |

|

|

|

1 |

|

1 |

|

|

|

|

|

|

1 |

|

1 |

|

1 |

1 |

1 |

|

|

1 |

1 |

|

|

|

|

|

|

1 |

|||||||||

|

|

|

TA=BC |

|

|

|

|

|

|

|

|

|

|

|

|

TB=C |

|

|

|

|

|

|

|

|

DB=B+C=BC |

|

|||||||||||||

|

|

|

|

|

|

JA |

A B |

|

|

|

|

|

|

|

|

|

KA |

|

|

A B |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

С |

|

00 01 11 10 |

|

С |

00 01 11 10 |

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

0 |

× |

|

|

|

|

|

× |

|

× |

|

|

|

0 |

× |

|

× |

|

|

|

× |

|

|

|

|

|

|

||||||||

|

|

|

|

|

1 |

|

|

|

|

1 |

|

|

× |

|

× |

|

|

|

1 |

× |

|

× |

|

1 |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

JA=BC |

|

|

|

|

|

|

|

|

|

|

|

KA=BC |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

TA |

|

T |

|

|

|

|

TB |

T |

|

|

|

|

|

|

TC |

|

T |

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

Вход |

|

|

|

|

|

|

СP |

|

|

A |

|

|

СP |

|

B |

|

|

|

|

СP |

|

|

С |

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

Рис. 3.4. Синтез кольцевого счетчика 1,2,3,4,5,6,7 методом |

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

словарных преобразований разностных карт минтермов |

|

|

|

|

|||||||||||||||||||||||||||||

24

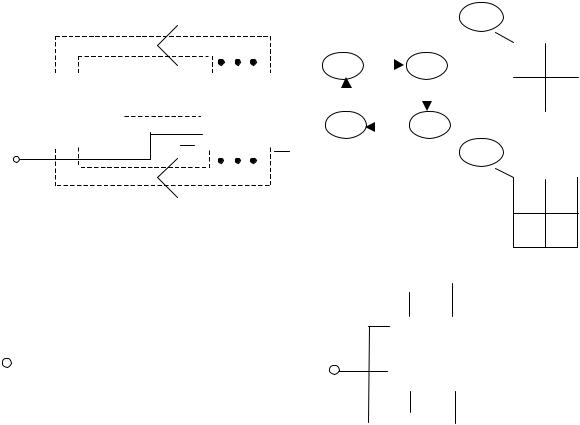

единственности схемы управления. Регистром сдвига или последовательной памятью называется запоминающее устройство, в котором при поступлении каждого тактового сигнала осуществляется сдвиг поступающей на вход информации на один разряд в одну сторону, т. е. A → B → C → ... → M → N. Анализ многоразрядного РС показывает, что в некоторых характеристических базисах законы управления входами триггерных ЛЭ оказываются такими (3.5), (3.6), (3.7), что обеспечивают максимальную простоту их внутреннего строения (рис. 3.5).

D-базис: |

D A |

= X ; D B = A ; D C = B ;... D N = M ; |

(3.5) |

||||||||||||||||

|

|

|

S A = |

X ; S B = |

A ; S C = |

B ;... S N = |

M ; |

||||||||||||

|

|

|

|||||||||||||||||

RS-базис: |

|

|

R A = |

X ; R B = |

|

|

|

; R C = |

|

|

|

|

;... R N = |

|

|

|

(3.6) |

||

|

|

|

|

A |

|

|

B |

|

|

M |

; |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J |

A = |

X ; J B = A ; J C = B ;... J N = M ; |

|||||||||||||||

|

|

||||||||||||||||||

JK-базис: |

|

|

|

A = |

X ; K B = |

|

|

; K C = |

|

|

|

|

;... K N = |

|

|

(3.7) |

|||

|

|

K |

A |

|

|

B |

|

|

M |

; |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Использование простого РС в качестве базисного ЛЭ продемонстрировано на примере реализации счетчика - делителя частоты на 4 (рис. 3.6). Видно, что при любом числе разрядов устройства (в данном случае n=2) необходима одна схема управления (СУ), только граф последовательности смены состояний должен удовлетворять условиям функционирования РС.

а) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

N |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

DA |

T |

|

|

|

|

|

|

DB |

T |

|

|

|

|

|

|

DN |

|

T |

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

СP |

|

|

|

|

A |

|

|

|

|

|

СP |

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

СP |

|

|

|

|

N |

||||||||||||||||||

|

|

СP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

N |

|

||||||||||||||

б) |

|

|

|

|

|

|

|

|

|

|

|

SA |

|

T |

|

|

|

|

|

SB |

|

T |

|

|

|

|

|

SN |

|

T |

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

СP |

|

|

A |

|

|

|

|

СP |

|

B |

|

|

|

|

СP |

|

|

|

N |

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

RA |

|

|

|

|

|

|

|

|

|

|

|

|

RB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RN |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

СP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

N |

||||||||||||||||

в) |

|

|

|

|

|

|

|

|

|

|

|

JA |

|

|

T |

|

|

|

|

|

|

|

JB |

|

|

T |

|

|

|

|

|

|

|

|

JN |

|

|

T |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

СP |

|

|

A |

|

|

|

|

СP |

|

|

B |

|

|

|

|

СP |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

N |

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

KA |

|

|

|

|

|

|

|

|

|

|

|

|

KB |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

KN |

|

|

|

|

|

|

|

|

|

|

|

||||||

|

СP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||

|

Рис. 3.5. Структурные схемы РС на основе D-, RS- и JK-триггеров |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

25

а) |

|

|

|

б) |

|

|

|

|

|

в) Аn+1 An |

1 |

|||

|

|

|

|

|

α 0 |

|

|

|

1α |

Bn |

0 |

|||

|

|

|

|

|

|

|

|

|

|

|||||

|

|

А |

|

N |

00 |

|

|

10 |

0 |

α |

1 |

|||

|

|

|

|

|

||||||||||

|

СУ |

А |

РC |

1 |

0 |

β |

||||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

||||||

|

|

01 |

|

|

|

11 |

|

|

|

|||||

|

|

|

Cp |

|

|

|

n+1 |

|

|

|||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

0β |

|

|

|

β 1 |

|

|

|||

|

|

А |

N |

|

|

|

|

|

Bn An0 |

1 |

||||

Cp |

|

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

α |

|||

|

|

|

|

|

|

|

|

|

|

|

|

0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

β |

1 |

г) DA= B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

д) JA=B; KA=B |

|

|

|

|

|

||||||||

|

|

|

A |

|

|

|

|

B |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

B |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

DA |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

Вход |

|

|

|

|

|

|

|

JA |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

РC |

|

|

Вход |

|

|

|

KA |

РC |

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

Cp |

|

|

|

|

|

|

Cp |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

A |

|

|

|

|

|

|

B |

|

|

|

|

A |

|

|

|

B |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 3.6. Реализация счетчика-делителя частоты на 4 на основе структуры простого РС

3.4. Задания для самостоятельного проектирования логических устройств П-типа

3.4.1. На основе триггера Т1 в произвольной элементной базе определить структурную схему триггера Т2 (номера вариантов приведены в табл. 3.3):

|

|

|

|

|

|

|

|

|

|

Таблица 3.3 |

|

T1 \ T2 |

D |

T |

RS |

|

|

|

JK |

DV |

|

||

RS |

|||||||||||

|

T |

1 |

- |

2 |

|

3 |

|

4 |

5 |

|

|

RS |

6 |

7 |

- |

|

8 |

|

9 |

10 |

|

||

|

|

|

11 |

12 |

13 |

|

- |

|

14 |

15 |

|

|

RS |

|

|

|

|||||||

JK |

16 |

17 |

18 |

|

19 |

|

- |

20 |

|

||

DV |

21 |

22 |

23 |

|

24 |

|

25 |

- |

|

||

3.4.2. Методом словарных преобразований разностных карт минтермов в произвольном характеристическом базисе получить оптимальную структурную схему трехразрядного кольцевого счетчика, реализующего последовательность П двоичных

эквивалентов чисел (табл. 3.4):

3.4.3. На основе структуры простого РС реализовать оптимальную схему счетчика-делителя частоты на N (табл. 3.5):

26

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 3.4 |

||

N варианта |

1 |

|

|

2 |

3 |

4 |

|

|

5 |

6 |

|

||||

П |

0,1,2,3,4,5 |

0,2,3,4,5,6 |

0,3,4,5,6,7 |

0,1,3,4,5,6 |

0,1,3,5,6,7 |

0,1,4,5,6,7 |

|

||||||||

N варианта |

7 |

|

|

8 |

9 |

10 |

|

|

11 |

12 |

|

||||

П |

1,2,3,4,5,6 |

1,3,4,5,6,7 |

1,2,4,5,6,7 |

1,2,3,4,6,7 |

1,2,3,4,6,0 |

1,2,4,5,7,0 |

|

||||||||

N варианта |

13 |

|

|

14 |

15 |

16 |

|

|

17 |

18 |

|

||||

П |

2,1,4,3,7,6 |

2,3,4,5,6,7 |

2,4,6,5,7,0 |

2,3,6,7,5,0 |

2,5,4,7,6,0 |

2,6,7,0,1,3 |

|

||||||||

N варианта |

19 |

|

|

20 |

21 |

22 |

|

|

23 |

24 |

|

||||

П |

3,4,5,6,7,0 |

3,5,7,0,2,4 |

3,5,4,6,7,0 |

3,4,6,0,2,1 |

3,6,5,7,1,0 |

3,7,2,1,0,6 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 3.5 |

||

N варианта |

1 |

|

2 |

|

3 |

|

4 |

5 |

|

6 |

|

7 |

|

8 |

|

N |

5 |

|

6 |

|

7 |

|

8 |

9 |

|

10 |

|

11 |

|

12 |

|

N варианта |

9 |

|

10 |

|

11 |

|

12 |

13 |

|

14 |

|

15 |

|

16 |

|

N |

13 |

|

14 |

|

15 |

|

16 |

18 |

|

20 |

|

21 |

|

22 |

|

N варианта |

17 |

|

18 |

|

19 |

|

20 |

21 |

|

22 |

|

23 |

|

24 |

|

N |

24 |

|

26 |

|

28 |

|

30 |

33 |

|

35 |

|

39 |

|

55 |

|

4. ПРОЕКТИРОВАНИЕ ЦИФРОВЫХ АВТОМАТОВ С ОГРАНИЧЕНИЯМИ НА ВЫХОДНЫЕ ПАРАМЕТРЫ

На практике любое техническое задание на проектирование содержит, помимо функциональных требований, ряд ограничений на выходные параметры устройства, касающихся быстродействия, потребляемой мощности, помехоустойчивости, технологичности и т. п. Поскольку в основе любой, сколь угодно сложной цифровой структуры лежат простейшие ключевые ЛЭ, реализующие базовый набор функций (И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ), их свойства и будут определять выходные характеристики синтезируемых схем.

4.1. Сравнительный анализ транзисторных логик.

Все ЛЭ характеризуются определенным набором параметров, позволяющих однозначно описывать и сравнивать различные типы логических ИС. Наиболее употребительными из них являются:

1) потребляемая мощность P = Pст + Pдин, равная сумме статического и динамического компонентов;

2)быстродействие, определяемое временем задержки распространения сигнала τ з;

3)энергия (работа) единичного переключения А = P•τ з;

4) помехоустойчивость как допустимый уровень помехи (чаще статической

Uстп );

5)коэффициент объединения по входу Kоб - число логических входов ЛЭ;

6)коэффициент разветвления по выходу Кразв - допустимое число подключаемых

квыходу нагрузок

Типовые параметры ЛЭ основных транзисторных логик приведены в табл. 4.1. Видно, что максимальным быстродействием обладает ТТЛШ- и ЭСЛ-схемы, наиболее

27

экономичны И2Л- и КМОП-структуры, а самую высокую помехоустойчивость обеспечивает применение МДП-логик.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 4.1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Тип |

|

P |

τ з (нс) |

А (пДж) |

|

Uст (В) |

K об |

Kразв |

|

Базовый |

|||||||||||||

|

|

логики |

|

(мВт/ис) |

|

|

набор ЛЭ |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

п |

|

|

|

||||||||||

|

Диодная |

|

|

2…20 |

|

1…10 |

|

20…50 |

|

0,3...0,4 |

|

2…5 |

5 |

|

И, ИЛИ |

|

|||||||||

|

|

ТТЛ |

|

|

|

1,2...1,5 |

|

|

И − НЕ, НЕ |

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

ТЛНС |

|

1…10 |

|

2…5 |

|

10…20 |

0,5 |

|

|

2…5 |

10 |

|

ИЛИ-НЕ |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

ТТЛ |

|

|

1…10 |

|

2...10 |

|

|

|

20...50 |

|

|

|

0,8...1,0 |

|

2…5 |

10 |

|

И-НЕ |

|||||

|

|

ТТЛШ |

|

1...5 |

|

|

10...20 |

|

|

0,5...0,8 |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

ТЛЭС |

10…20 |

0,5…1,0 |

10…20 |

0,2…0,3 |

2…5 |

10…20 |

|

ИЛИ, |

|||||||||||||||

|

|

(ЭСЛ) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ИЛИ_НЕ |

|||

|

|

И2Л |

0,01…0,1 |

|

10…50 |

|

0,1…1,0 |

0,02…0,05 |

1 |

3…5 |

|

ИЛИ-НЕ |

|||||||||||||

|

МДПТЛ |

|

0,5...5,0 |

|

|

10...50 |

|

|

5...20 |

|

2...3 |

|

2…5 |

100… |

|

И-НЕ, |

|||||||||

|

КМДПТЛ |

0,01...0,1 |

20...100 |

|

|

|

|

||||||||||||||||||

|

|

0,2...2,0 |

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

1...2 |

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

200 |

|

ИЛИ-НЕ |

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.2. Контрольные задания и методические указания по их выполнению

4.2.1. В элементной базе ИС выполнить разработку полного вычитателя (вычитателя трех двоичных цифр с образованием разности R и заема Z из старшего разряда), обеспечивающего:

а) высокое быстродействие при сравнительно низкой потребляемой мощности; б) максимальную защиту от статических помех при хорошем быстродействии и

высокой нагрузочной способности; в) максимальное быстродействие, малую энергию единичного переключения и

хорошую нагрузочную способность; г) минимальную энергию единичного переключения.

4.2.2. Построить простейший обнаружитель ошибок цифрового десятичного кода N в виде ИС с указанными требованиями (табл. 4.2):

Таблица 4.2

N варианта |

Код N |

Ограничения на выходные параметры |

|

1 |

+1 |

Максимальная помехоустойчивость |

|

2 |

+5 |

Высокая помехоустойчивость и минимальная потребляемая |

|

мощность |

|||

|

|

||

3 |

+9 |

Высокое быстродействие и низкая потребляемая мощность |

|

4 |

+11 |

Минимальная энергия единичного переключения |

|

5 |

+13 |

Высокое быстродействие, биполярная технология |

|

6 |

2 из 5 |

Высокое быстродействие, униполярная технология |

|

7 |

3 из 5 |

A = Amin, биполярная технология |

|

8 |

Джонсона |

Минимальное число транзисторов при практической |

|

|

|

реализации |

28

4.2.3. Построить оптимальную схему преобразователя кода N1 в код N2, обеспечивающую в элементной базе ИС (табл. 4.3):

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Таблица 4.3 |

|||

NN вариантов |

Код N1 |

|

Код N2 |

|

|

Ограничения на выходные параметры |

|

||||||||||||||||

1 |

+4 |

|

|

|

|

|

БК |

|

Максимальное быстродействие при P = Pmin |

|

|||||||||||||

2 |

+2 |

|

|

|

|

3 из 5 |

|

Минимум |

транзисторов |

при |

практической |

|

|||||||||||

|

|

|

|

|

реализации |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

3 |

|

БК |

|

3 из 5 |

|

P = Pmin при A = Amin |

|

|

|

|

|

||||||||||||

4 |

Грея |

|

3 из 5 |

|

Высокая помехоустойчивость при P = Pmin |

|

|||||||||||||||||

5 |

+3 |

|

|

|

|

3 из 5 |

|

Высокое быстродействие, биполярная технология |

|

||||||||||||||

6 |

Айкена |

|

3 из 5 |

|

Высокое быстродействие, униполярная технология |

|

|||||||||||||||||

7 |

+4 |

|

|

|

|

+2 |

|

|

A = Amin |

|

|

|

|

|

|

||||||||

8 |

+4 |

|

|

|

|

Грея |

|

P = Pmin, высокая нагрузочная способность |

|

||||||||||||||

|

|

4.2.4. На основе триггера T1 выполнить проектирование триггераT2, в элементной |

|||||||||||||||||||||

базе ИС обеспечивающего (табл. 4.4): |

|

|

Таблица 4.4 |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

NN вариантов |

|

T1 |

|

|

|

|

|

T2 |

|

|

|

Ограничения на выходные параметры |

|

||||||||||

1 |

|

T |

|

|

|

|

|

WI |

|

Максимальное быстродействие при P = Pmin |

|

||||||||||||

2 |

|

RS |

|

|

|

|

|

|

|

|

P = Pmin, высокая нагрузочная способность |

|

|||||||||||

|

|

|

WI |

|

|

||||||||||||||||||

3 |

|

JK |

|

|

|

|

|

WI |

|

A = Amin |

|

|

|

|

|

|

|||||||

4 |

DV |

|

|

|

|

|

|

|

|

Минимум |

транзисторов |

при |

практической |

|

|||||||||

|

|

|

WI |

|

|

||||||||||||||||||

|

|

|

реализации |

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

5 |

|

WI |

|

|

|

T |

|

P = Pmin при A = Amin |

|

|

|

|

|

||||||||||

6 |

|

|

|

|

|

|

|

RS |

|

Высокое быстродействие, униполярная технология |

|

||||||||||||

|

WI |

|

|

|

|

|

|||||||||||||||||

7 |

|

WI |

|

|

|

JK |

|

Максимальная помехоустойчивость |

|

|

|

|

|||||||||||

8 |

|

|

|

|

|

|

|

DV |

|

Высокое быстродействие, биполярная технология |

|

||||||||||||

|

WI |

|

|

|

|

|

|||||||||||||||||

|

|

Примечание. |

|

|

Характеристическое уравнение WI-триггера Qn+ 1 = |

[W |

|

+ IQ]n , а |

|||||||||||||||

|

|

I |

|||||||||||||||||||||

|

|

-триггера - Qn+ 1 = |

[ |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

WI+ |

IQ]n . |

|

|

|

|

|

|

||||||||||||||

WI |

|

|

|

|

|

|

|||||||||||||||||

|

|

4.2.5. Спроектировать оптимальную структурную схему кольцевого счетчика с |

|||||||||||||||||||||

последовательностью N, которую отличает (табл. 4.5): |

|

Таблица 4.5. |

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

NN вариантов |

Последовательность N |

|

Ограничения на выходные параметры |

|

|||||||||||||||||||

1 |

|

|

5,0,2,7,4,6 |

|

|

Минимум транзисторов при реализации |

|

||||||||||||||||

2 |

|

|

5,1,3,4,7,6 |

|

|

P = Pmin при A = Amin |

|

|

|

|

|

||||||||||||

3 |

|

|

5,7,6,4,2,3 |

|

|

P = Pmin, максимальный Kразв |

|

|

|

|

|||||||||||||

4 |

|

|

5,6,2,0,4,1 |

|

|

Ипст = Ипст max при P = Pmin |

|

|

|

|

|||||||||||||

5 |

|

|

6,0,7,3,2,5 |

|

|

τ p = τ p ьшт, биполярная технология |

|

||||||||||||||||

6 |

|

|

6,1,7,3,5,2 |

|

|

τ p = τ p ьшт, униполярная технология |

|

||||||||||||||||

7 |

|

|

6,2,3,5,7,1 |

|

|

A = Amin |

|

|

|

|

|

||||||||||||

8 |

|

|

6,3,2,4,7,0 |

|

|

Максимальное быстродействие при P = Pmin |

|

||||||||||||||||