- •Введение.

- •Цели и задачи дисциплины.

- •Связь с другими дисциплинами и необходимый уровень подготовки.

- •Кодирование логической и двоичной информации электрическими сигналами.

- •Характеристики электрических сигналов.

- •Простейшие логические операции и их схемотехническая реализация (диодные схемы).

- •Ттл элемент, работа схемы, основные характеристики.

- •Разновидности логических элементов и серии интегральных микросхем.

- •Соединения логических элементов и радиокомпонентов.

- •Схемотехника функциональных устройств.

- •Схемотехника последовательностных устройств.

- •Триггеры.

- •Счётчики.

- •Двоичные счетчики.

- •Недвоичные счетчики.

- •Регистры.

- •Параллельные регистры.

- •Последовательные (сдвиговые) регистры.

- •Комбинационные устройства.

- •Дешифраторы.

- •Линейный дешифратор.

- •Матричный дешифратор.

- •Пирамидальный дешифратор.

- •Дешифраторы интегрального исполнения.

- •Мультиплексор и демультиплексор.

- •Мультиплексоры интегрального исполнения.

- •Сумматоры.

- •Одноразрядные комбинационные сумматоры.

- •Многоразрядные сумматоры.

- •Последовательный многоразрядный сумматор.

- •Параллельный многоразрядный сумматор.

- •Ускоренный перенос.

- •Арифметико-логическое устройство.

- •Устройства памяти.

- •Статические элементы оперативных запоминающих устройств.

- •Запоминающий элемент на биполярных транзисторах.

- •Запоминающий элемент на полевых транзисторах.

- •Динамический запоминающий элемент оперативных запоминающих устройств.

- •Запоминающие элементы пзу.

- •Организация бис зу.

- •Построение запоминающих устройств эвм.

- •Программируемые логические матрицы.

- •Формирователи.

- •Определение интервала времени по заданным уровням сигналов в цепях первого порядка.

- •Формирователи периодических сигналов.

- •Несимметричный мультивибратор на логических элементах.

- •Формирователь фронтов (спадов) — триггер Шмитта.

- •Формирователи импульсов.

- •Формирователь на интегрирующей rc цепи.

- •Одновибратор с дифференцирующей rc цепью.

- •Одновибраторы интегрального исполнения.

- •Интерфейсные устройства.

- •Буферные устройства.

- •Передача сигналов по линиям связи.

- •Несимметричные линии связи.

- •Согласование линий связи.

- •Симметричные линии связи.

- •Цифро-аналоговые и аналого-цифровые преобразователи.

- •Цифро-аналоговые преобразователи (цап).

- •Цифро-аналоговый преобразователь на суммировании токов.

- •Цифро-аналоговый преобразователь на матрице r-2r.

- •Аналого-цифровые преобразователи (ацп).

- •Параллельный ацп.

- •Ацп последовательного приближения (последовательные ацп).

- •Ацп двойного интегрирования.

- •Системы индикации.

- •Индикация состояния логического элемента.

- •Индикация состояния шин.

Схемотехника функциональных устройств.

Электронные устройства, блоки и узлы ЭВМ по функциональному назначению обладают большим разнообразием. Среди них можно выделить: автоматы и комбинационные устройства. Автоматы─ функциональные электронные устройствасостояниевыходов,которых в любой момент времениопределяетсясостояниемвходовипредыдущимсостояниемустройства. Из определения понятно, что автоматы ─ устройства обладающие памятью. В литературе часто автоматы называют последовательностными устройствами.Комбинационныеустройства─ это устройствасостояниевыходов,которых влюбоймоментвремениоднозначно определяется состоянием входов, т.е. комбинационные устройства не имеют памяти.

Схемотехника последовательностных устройств.

Триггеры.

Т

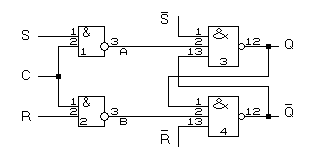

Рис.17. Асинхронный RS триггер.

![]() .

При нормальной работе устройства выходы

должны находиться в противоположных

состояниях, т.е. если Q=1, то

.

При нормальной работе устройства выходы

должны находиться в противоположных

состояниях, т.е. если Q=1, то![]() =0.

Рассмотрение схемотехники и работы

триггеров начнем с самой простой схемы

─асинхронныйRSтриггер. На

рис. 17а показана принципиальная схема

этого триггера в базисе И-НЕ, а на рисунке

17б ─ временная диаграмма его работы.

Для анализа работы схемы составленной

из логических элементов существуют

стандартные методы: начинать анализ

нужно с того элемента, на входе которого

изменилось состояние переменной, перед

анализом нужно определить начальное

состояние схемы и возможные значения

входных и управляющих переменных.

=0.

Рассмотрение схемотехники и работы

триггеров начнем с самой простой схемы

─асинхронныйRSтриггер. На

рис. 17а показана принципиальная схема

этого триггера в базисе И-НЕ, а на рисунке

17б ─ временная диаграмма его работы.

Для анализа работы схемы составленной

из логических элементов существуют

стандартные методы: начинать анализ

нужно с того элемента, на входе которого

изменилось состояние переменной, перед

анализом нужно определить начальное

состояние схемы и возможные значения

входных и управляющих переменных.

Исходя из этих рекомендаций ясно, что

переменные S и R в статическом состоянии

триггера должны быть равны -”1”. Так

как , если обе переменные будут равны

“0”, то оба выхода схемы должны иметь

единичное значение, чего быть не должно,

исходя из понятия триггера. Триггер --

устройство с памятью и поэтому необходимо

задаться состоянием выходов, выберем

нулевое -- Q=0. Таким образом начальное

состояние: R=S=1, Q=0,

![]() =1.

=1.

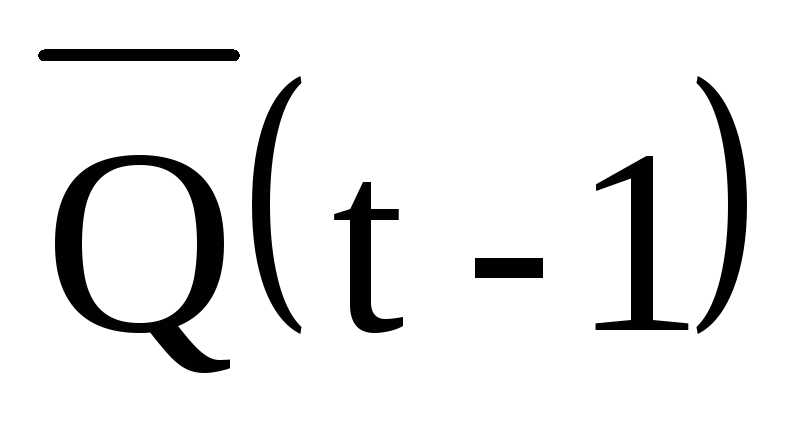

Возможные состояния асинхронного RS триггера, определяемые значениями входных переменных R и S, приведены в таблице 4.

Таблица 4.

-

R

S

Q

Режим

0

0

1

1

Запрещённое сост

1

0

1

0

Запись “1”

0

1

0

1

Запись “0”

1

1

Q(t─1)

Хранение

Из

таблицы видно, что триггер управляется

только на запись и хранение двумя

переменными S и R, причем если одна из

переменных принимает нулевое значение

состояние триггера изменяется. Поэтому

говорят, что входные переменные активны

низким уровнем. Время переключения

триггера равно двум интервалам задержки

логического элемента -- ![]() .

Триггер называется асинхронным так как

он реагирует на любые изменения входных

переменных. К недостаткам триггера

необходимо отнести: - входная информация

должна в обязательном порядке подаваться

в парафазном коде (по двум проводникам),

что приводит к существенному усложнению

плат печатного монтажа; при проектировании

сложных узлов необходимо следить, чтобы

входные переменные не принимали

запрещенного состояния.

.

Триггер называется асинхронным так как

он реагирует на любые изменения входных

переменных. К недостаткам триггера

необходимо отнести: - входная информация

должна в обязательном порядке подаваться

в парафазном коде (по двум проводникам),

что приводит к существенному усложнению

плат печатного монтажа; при проектировании

сложных узлов необходимо следить, чтобы

входные переменные не принимали

запрещенного состояния.

Лекция 9.

Рис.18. Принципиальная схема синхронного

RS триггера.

![]() .

Управляющий вход С называют синхронизирующим.

Если С=0, то независимо от переменных R

и S промежуточные переменные А и В равны

единице, следовательно триггер не

воспринимает изменения информационных

переменных R и S.

.

Управляющий вход С называют синхронизирующим.

Если С=0, то независимо от переменных R

и S промежуточные переменные А и В равны

единице, следовательно триггер не

воспринимает изменения информационных

переменных R и S.

Важно отметить, что А=В=1 -- это режим хранения для асинхронного RS триггера. Дальнейший анализ работы триггера целесообразен только при С=1, и для этого условия будем строить временную диаграмму, приведенную на рис.19.

Исходное состояние: S=R=0, тогда будем

иметь А=В=1 и по выходу выбираем нулевое

состояние Q=0,

![]() =1.

=1.

В

момент времени t1 переменной S даем

значение “1” и через один интервал

задержки переменная А=0, что является

активным уровнем для асинхронного RS

триггера на 3 и 4 элементах. Через два

интервала задержки переменная Q =1 и

через три интервала

В

момент времени t1 переменной S даем

значение “1” и через один интервал

задержки переменная А=0, что является

активным уровнем для асинхронного RS

триггера на 3 и 4 элементах. Через два

интервала задержки переменная Q =1 и

через три интервала![]() =

0. Следовательно, начиная от момента t1

в течении трех интервалов задержки

проходит процесс записи “1” в триггер.

=

0. Следовательно, начиная от момента t1

в течении трех интервалов задержки

проходит процесс записи “1” в триггер.

А

Рис. 20. Временная диаграмма работы

синхронного RSтриггера.

![]() .

.

Возможные состояния RS триггера приведены в таблице 5

Таблица 5.

|

R |

S |

Q |

|

Режим |

|

0 |

0 |

Q(t-1) |

|

Хранение |

|

0 |

1 |

1 |

0 |

Запись “1” |

|

1 |

0 |

0 |

1 |

Запись “0” |

|

1 |

1 |

1 |

1 |

Запрещённое состояние |

Асинхронный RS триггер имеет дополнительные

входы

![]() и

и![]() ,активные низким уровнем. Они предназначены

для независимой (предварительной)

установки триггера.

,активные низким уровнем. Они предназначены

для независимой (предварительной)

установки триггера.

Основным недостатком синхронного RS триггера является необходимость представления информации в парафазном коде. Поэтому дальнейшие разработки связаны с изменением формы представления информации. Так можно объяснить появление D триггеров.

Р ассмотрим

схемотехнику и работу D триггера.Принципиальная схема D триггера

приведена на рис. 21. Основой для построения

схемы D триггера является асинхронный

RS триггер (3 и 4 элементы). На 1 и 2 элементах

собрана схема управления (входная

логика), имеется два входа: D -- информационный

вход, С -- вход синхронизации. Входные

элементы -- 2И-НЕ и поэтому, когда С=0

А=В=1 независимо от состояния переменной

D, а это режим хранения для RS триггера

на 3 и 4 элементах.

ассмотрим

схемотехнику и работу D триггера.Принципиальная схема D триггера

приведена на рис. 21. Основой для построения

схемы D триггера является асинхронный

RS триггер (3 и 4 элементы). На 1 и 2 элементах

собрана схема управления (входная

логика), имеется два входа: D -- информационный

вход, С -- вход синхронизации. Входные

элементы -- 2И-НЕ и поэтому, когда С=0

А=В=1 независимо от состояния переменной

D, а это режим хранения для RS триггера

на 3 и 4 элементах.

Рассмотрим работу схемы, временная диаграмма приведена на рис.22.

Д

Рис.21. Принципиальная схема D триггера

- защелки.

При этом промежуточные переменные А=В=1, что соответствует режиму хранения для асинхронного RS триггера на 3 и 4 элементах.

Рис.22. Временная диаграмма работы D триггера - защелки.

При записи “0” время переключения триггера равно четырем интервалам задержки, а при записи “1” -- трем интервалам задержки (на временной диаграмме задержки помечены штрихами).

В момент времени t7 переменной С даем нулевое значение при D=1. Через один интервал задержки А=1, т.е. триггер перешел в режим хранения информации, записанной в триггер начиная с момента t6. Изменение D=0 в момент t8 не вызовет никаких изменений, так как С=0. В момент времени t9 С=1 и D=0, происходит процесс записи “0” в триггер, на который затрачивается три интервала задержки. В момент t10 С=0 переводит триггер в режим хранения.

Анализ временной диаграммы позволяет

оценить максимальное время переключения

D триггера --

![]() .

Возможные состояния D триггера определяются

таблицей состояний (табл.6).

.

Возможные состояния D триггера определяются

таблицей состояний (табл.6).

Таблица 6.

-

D

C

Q

Режим

0

0

Q(t-1)

(t-1)

(t-1)Хранение

1

0

Q(t-1)

(t-1)

(t-1)Хранение

0

1

0

1

Запись ”0”

1

1

1

0

Запись “1”

Как видно из таблицы состояний D триггера в отличие от ранее рассмотренных схем у этого триггера отсутствует запрещенное состояние, при С=0 не зависимо от значения D триггер находится в режиме хранения, при С=1 выходная переменная Q повторяет все изменения входной переменной D. Запоминается та информация которая была на входе в момент перехода С из единичного в нулевое состояние. Поэтому часто этот триггер называют D триггер - защелка.

а б

Рис.23. D триггер - защелка, рекомендуемые изображения.

На рис. 23 приведены изображения D триггера - защелки на принципиальных электрических схемах устройств в соответствии с требованиями ГОСТ. На рис.23а показана микросхема К155ТМ7, в состав которой входят четыре D триггера - защелки. В этой микросхеме каждые два триггера имеют общее управление -- общий вход С, обозначаемые соответственно С12 и С34, каждый триггер имеет два выхода прямой и инверсный. На рис.23б приведено изображение одиночного D триггера - защелки.

Лекция 10.

Триггеры с динамическим управлением.

О собенность

триггеров со статическим управлением

состоящая в том , что при С=1 вся изменяющаяся

информация на входе передается на

выход, требует учитывать все изменения

состояния входов. Это существенно

усложняет процесс проектирования.

Желательно иметь триггер, который бы

записывал информацию имеющуюся на входе

в конкретный момент времени. Мы рассмотрим

две схемы триггеров, удовлетворяющих

этому требованию.

собенность

триггеров со статическим управлением

состоящая в том , что при С=1 вся изменяющаяся

информация на входе передается на

выход, требует учитывать все изменения

состояния входов. Это существенно

усложняет процесс проектирования.

Желательно иметь триггер, который бы

записывал информацию имеющуюся на входе

в конкретный момент времени. Мы рассмотрим

две схемы триггеров, удовлетворяющих

этому требованию.

D триггер с динамической блокировкой входов. Схема D триггера с динамической блокировкой входов приведена на рис. 24.

Рассматриваемый триггер построен на шести элементах 3И-НЕ; 1,2,3 и 4 элементы реализуют входную логику а на 5 и 6 элементах реализован асинхронный RS триггер, являющийся основой. Можно к анализу схемы подойти по другому; на 2,3,5 и 6 элементах реализован D триггер-защёлка, а 1 и 4 элементы формируют входную логику, исключающую срабатывание триггера по уровню.

Д

Рис.24. D триггер с динамической блокировкой

входов.

![]() =1,

=1,![]() =1.

Работа схемы отображается временной

диаграммой, которая приведена на рис.25.

=1.

Работа схемы отображается временной

диаграммой, которая приведена на рис.25.

Рис.25. Временная диаграмма работы D триггера с динамической блокировкой входов.

Анализируя временную диаграмму, определим

время задержки переключения

![]() .

Возможные состояния триггера показаны

в таблице 7.

.

Возможные состояния триггера показаны

в таблице 7.

Таблица 7

|

D |

C |

R |

S |

Q |

|

Режим |

|

* |

* |

0 |

1 |

0 |

1 |

Установка в “0” |

|

* |

* |

1 |

0 |

1 |

0 |

Установка в “1” |

|

0 |

0 |

1 |

1 |

Q(t-1) |

|

Хранение |

|

0 |

|

1 |

1 |

0 |

1 |

Запись “0” |

|

1 |

|

1 |

1 |

1 |

0 |

Запись “1” |

Примечание. В таблице приняты обозначения:

* ─ безразличное состояние переменной;

![]() --

фронт сигнала (переход 0-1).

--

фронт сигнала (переход 0-1).

D триггер с динамической блокировкой входов является основой построения многих функциональных устройств. Как отдельный функциональный элемент он входит в состав микросхемы К155ТМ2. Изображения этого триггера, рекомендуемые ГОСТ приведены на рис.26.

На рисунке показано изображение одного из двух триггеров, входящих в микросхему К155ТМ2, на правой части рисунка приведено изображение триггера не привязанное к какой-либо микросхеме

Рис.26. Рекомендуемые изображения D триггера с динамической блокировкой входов.

Управляющий вход активный переходом (фронтом или спадом) называют динамическим и для его обозначения рекомендуется треугольник или косая черта.

Лекция 11.

К триггерам с динамическим управлением относится и универсальный JK триггер. Принципиальная электрическая схема JK триггера приведена на рисунке 27.

Универсальный JK триггер построен по принципу “ведущий - ведомый”, т.е. состоит из двух триггеров и работает как двухтактный триггер. Под тактностью триггерных устройств будем понимать количество синхронизирующих последовательностей необходимых для нормального функционирования устройства. В данном устройстве одна последовательность - С подается на 1 и 2 элементы, а вторая ─ на 6 и 7 элементы. Однако в большинстве случаев эти последовательности должны находится в противофазе, и вторая последовательность может быть получена из первой ее инвертированием (элемент 3).

Рис.27. Принципиальная электрическая схема

универсального JK триггера.

П ервый

триггер ведущий выполнен на 4 и 5 элементах,

а второй на элементах 8 и 9. Сущность

работы состоит в том, что информация,

имеющаяся на входахJиK, сначала записывается

в первый (ведущий) триггер а затем

переписывается во второй (ведомый)

триггер то есть появляется на выходах

триггера. Для исключения срабатывания

триггера по уровню введены обратные

связи. Временная диаграмма работыJKтриггера приведена на рис.28.

ервый

триггер ведущий выполнен на 4 и 5 элементах,

а второй на элементах 8 и 9. Сущность

работы состоит в том, что информация,

имеющаяся на входахJиK, сначала записывается

в первый (ведущий) триггер а затем

переписывается во второй (ведомый)

триггер то есть появляется на выходах

триггера. Для исключения срабатывания

триггера по уровню введены обратные

связи. Временная диаграмма работыJKтриггера приведена на рис.28.

Рассмотрим работу JKтриггера. Исходное состояние:J=K=C= 0, при этом промежуточные переменные А = В = 1, а это режим хранения для асинхронногоRSтриггера на 4 и 5 элементах. выбираем исходное состояние первого триггера нулевое, то естьQ1 = 0. Анализируя состояние остальных переменных, получимA1 = 1,B1 =Q= 0.

При t=t5K= 1, и приt=t6J= 1, эти изменения входных переменных не приведут к изменениям состояния внутри схемы, так как С = 0. В моментt7 переменная С принимает единичное значение , и соответственно через один интервал В = 0 и А1 = 1. Сигнал В = 0 ─ активный уровень на входе первогоRSтриггера и он переключается, через два интервала отt7 инверсияQ1 = 1 и через три интервалаQ1 = 1.

П

Рис. 28. Временная диаграмма работы

триггера.

При t=t9C= 1, и через один интервал А = 0, через два интервала В1 = 1 иQ1 = 1, через три интервала инверсияQ1 = 0. В моментt10 при С = 0 происходит перезапись содержимого первого триггера во второй с соответствующими задержками, и на выходах получаемQ= 1 и инверсияQ= 0. В триггер записалась «1» приJ=K= 1, то есть в триггер записалось значение пртивоположное предыдущему, что характерно для счетного режима. В моментt11 при К = 1 и С = 0Jпринимает нулевое значение, но остальные переменные своих значений не меняют. На интервалеt12 ÷t13 показан процесс записи «0» в триггер.

Таким образом, временная диаграмма отображает следующие режимы работы JKтриггера:

интервал t2 –t4 ─ запись единицы в триггер;

интервал t7 –t10 – счетный режим;

интервал t12 –t13 – запись нуля в триггер;

при С = 0 и J=K= 0 ─ режим хранения.

Анализ временной диаграммы и таблицы состояний позволяет сделать следующие выводы:

Входная информация должна подаваться в парафазном коде.

Установочные входы SиRактивны низким уровнем.

По фронту сигнала С информация записывается в первый (ведущий) триггер, а по спаду сигнала С информация переписывается во второй (ведомый) триггер и появляется на выходах триггеров, поэтому принято считать, что сигнал С активен спадом.

При J=K= 1 триггер работает как одноразрядный счетчик, у которого счетный сигнал подается на вход С.

При С = 0 и/или J=K= 0 триггер находиться в режиме хранения ранее записанной информации.

Время задержки переключения триггера tпер= 4*tздперср.

Возможные состояния JKтриггера отображены в таблице 8.

Таблица 8.

-

J

K

C

S

R

Q

Режим

*

*

*

0

1

1

0

Установка в «1»

*

*

*

1

0

0

1

Установка в «0»

*

*

0

1

1

Q(t – 1)

Хранение

0

0

*

1

1

Q(t – 1)

Хранение

0

1

↓

1

1

0

1

Запись «0»

1

0

↓

1

1

1

0

Запись «1»

1

1

↓

1

1

Q(t – 1)

Счетный

Р екомендуемые

ГОСТом изображенияJKтриггера для принципиальных электрических

схем блоков и узлов ЭВМ приведены на

рис. 29.

екомендуемые

ГОСТом изображенияJKтриггера для принципиальных электрических

схем блоков и узлов ЭВМ приведены на

рис. 29.

Н

Рис. 29. Рекомендуемые изображения JKтриггера.

Лекция 12.

Счетный триггер.

Счетный триггер ─ устройство выполняющее микрооперацию счета. Микрооперация счета состоит в том, что по приходу каждого счетного сигнала выходы триггера меняют свое состояние на противоположные.

С четный

триггер может быть синхронным или

асинхронным. Синхронный триггер для

выполнения микрооперации счета требует

активного сигнала синхронизации.

Асинхронный триггер выполняет операцию

счета по приходу каждого сигнала. Счетный

сигнал является импульсом, и необходимо

четко различать фронтом или спадом он

активен.

четный

триггер может быть синхронным или

асинхронным. Синхронный триггер для

выполнения микрооперации счета требует

активного сигнала синхронизации.

Асинхронный триггер выполняет операцию

счета по приходу каждого сигнала. Счетный

сигнал является импульсом, и необходимо

четко различать фронтом или спадом он

активен.

На рис. 30а приведено изображение синхронного счетного триггера. Вход синхронизирующей переменной ─ СЕ, а асинхронные установочные входы ─ SиR. Счетный сигнал активен фронтом.

На рис. 30б изображен триггер асинхронный, у котрого счетный сигнал активен спадом.

О

Рис. 30. Рекомендуемые изображения

счетного триггера.

Схемотехническая реализация счетного триггера на Dтриггере показана на рис. 31.

Как видно из рисунка для реализации счетного режима на D триггере необходимо выполнить соединение: инверсный выход соединить с информационным D входом. Счётная переменная X подается на синхронизирующий вход D триггера. Счётный вход активен фронтом сигнала X. Выходной сигнал Q имеет частоту в два раза меньшую чем счетный сигнал.

Наиболее просто счетный триггер реализуется на универсальном JK триггере. Для этого достаточно подать на J и K входы высокий уровень, а счетный сигнал подавать на С вход.