- •Введение.

- •Цели и задачи дисциплины.

- •Связь с другими дисциплинами и необходимый уровень подготовки.

- •Кодирование логической и двоичной информации электрическими сигналами.

- •Характеристики электрических сигналов.

- •Простейшие логические операции и их схемотехническая реализация (диодные схемы).

- •Ттл элемент, работа схемы, основные характеристики.

- •Разновидности логических элементов и серии интегральных микросхем.

- •Соединения логических элементов и радиокомпонентов.

- •Схемотехника функциональных устройств.

- •Схемотехника последовательностных устройств.

- •Триггеры.

- •Счётчики.

- •Двоичные счетчики.

- •Недвоичные счетчики.

- •Регистры.

- •Параллельные регистры.

- •Последовательные (сдвиговые) регистры.

- •Комбинационные устройства.

- •Дешифраторы.

- •Линейный дешифратор.

- •Матричный дешифратор.

- •Пирамидальный дешифратор.

- •Дешифраторы интегрального исполнения.

- •Мультиплексор и демультиплексор.

- •Мультиплексоры интегрального исполнения.

- •Сумматоры.

- •Одноразрядные комбинационные сумматоры.

- •Многоразрядные сумматоры.

- •Последовательный многоразрядный сумматор.

- •Параллельный многоразрядный сумматор.

- •Ускоренный перенос.

- •Арифметико-логическое устройство.

- •Устройства памяти.

- •Статические элементы оперативных запоминающих устройств.

- •Запоминающий элемент на биполярных транзисторах.

- •Запоминающий элемент на полевых транзисторах.

- •Динамический запоминающий элемент оперативных запоминающих устройств.

- •Запоминающие элементы пзу.

- •Организация бис зу.

- •Построение запоминающих устройств эвм.

- •Программируемые логические матрицы.

- •Формирователи.

- •Определение интервала времени по заданным уровням сигналов в цепях первого порядка.

- •Формирователи периодических сигналов.

- •Несимметричный мультивибратор на логических элементах.

- •Формирователь фронтов (спадов) — триггер Шмитта.

- •Формирователи импульсов.

- •Формирователь на интегрирующей rc цепи.

- •Одновибратор с дифференцирующей rc цепью.

- •Одновибраторы интегрального исполнения.

- •Интерфейсные устройства.

- •Буферные устройства.

- •Передача сигналов по линиям связи.

- •Несимметричные линии связи.

- •Согласование линий связи.

- •Симметричные линии связи.

- •Цифро-аналоговые и аналого-цифровые преобразователи.

- •Цифро-аналоговые преобразователи (цап).

- •Цифро-аналоговый преобразователь на суммировании токов.

- •Цифро-аналоговый преобразователь на матрице r-2r.

- •Аналого-цифровые преобразователи (ацп).

- •Параллельный ацп.

- •Ацп последовательного приближения (последовательные ацп).

- •Ацп двойного интегрирования.

- •Системы индикации.

- •Индикация состояния логического элемента.

- •Индикация состояния шин.

Соединения логических элементов и радиокомпонентов.

При построении принципиальных электрических схем электронных вычислительных устройств необходимо выполнять самые разнообразные соединения, наиболее часто соединять логические элементы и функциональные устройства и реже соединять логические элементы и радиокомпоненты (резисторы, конденсаторы, транзисторы и т.п.). Поэтому необходимо знать как правильно выполнять такие соединения.

Соединение логических элементов. При построении принципиальных электрических схем блоков и узлов ЭВМ необходимо выполнять соединение входов и выходов микросхем (входов и выходов логических элементов). Для правильного выполнения соединений нужно руководствоваться рекомендациями изготовителей микросхем.

Таблица 3

-

Нагружаемый

выход

К155

К531

К555

К1531

К1533

К155

10

8

40

25

80

К531

12

10

50

30

100

К555

5

4

20

12

40

К1531

12

10

50

10

100

К1533

2

2

10

6

20

Прежде всего необходимо учитывать нагрузочную способность элементов. Под нагрузочной способностью понимается максимальное количество входов, которое можно подключить к выходу элемента, чтобы при этом электрические и временные параметры сигналов остались в допустимых пределах. Нагрузочная способность внутри серий элементов имеет следующие значения: К155, К531, КР1531 - 10; К555, 1533 -20. Нагрузочная способность элементов при электрическом соединении элементов различных серий приведена в таблице 3.

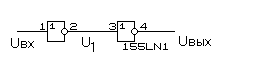

Рис. 13. Последовательное соединение элементов.

Широко используется последовательное соединение элементов (рис.13) для получения дополнительной задержки прохождения сигнала. На выходе последовательной цепочки элементов крутизна фронтов и спадов резко возрастает, а время задержки сигнала будет равно произведению среднего времени задержки одного элемента на количество элементов.

Однако нужно учитывать, что если количество элементов нечетно на выходе цепочки получим инверсный сигнал.

На рис. 13 приведена схема последовательного соединения логических элементов и показано построение графика зависимости Uвых = f(Uвх) для всей схемы.

Из графика видно, что для изменения выходного напряжения в том же диапазоне у соединения элементов необходимо значительно меньшее изменение входного напряжения -- U2вх - U1вх. Следовательно крутизна фронтов и спадов сигналов на выходе последовательной цепочки элементов будет значительно большей, чем у одиночного элемента.

Рис.14. Рис.15

Параллельное соединение Объединение выходов

элементов. элементов.

На рис.14 показано параллельное соединение элементов. По рекомендации изготовителей интегральных микросхем подобное соединение не рекомендуется, но допускается. Соединение, показанное на рис.15 (объединение выходов элементов) недопустимо, так как приводит к появлению тока короткого замыкания, при различных состояниях выходов логических элементов, а это в свою очередь может привести к аварии одного из элементов.

С оединение

логического элемента и пассивных

радиокомпонентов. При построении

принципиальных схем часто используют

подключение к логическому элементу

резисторов и конденсаторов. Для повышения

помехоустойчивости неиспользуемые

входы логических элементов рекомендуется

подключать через резистор к шине питания.

Через резистор величиной 1кОм можно

подключить 20 различных входов элементов

серии К155.

оединение

логического элемента и пассивных

радиокомпонентов. При построении

принципиальных схем часто используют

подключение к логическому элементу

резисторов и конденсаторов. Для повышения

помехоустойчивости неиспользуемые

входы логических элементов рекомендуется

подключать через резистор к шине питания.

Через резистор величиной 1кОм можно

подключить 20 различных входов элементов

серии К155.

Включение резистора между входом элемента и общей шиной используется при построении различных формирователей и на величину резистора накладывается ограничение сверху: резистор должен иметь величину не более 2 кОм. Действительно, при таком включении входное напряжение элемента определяется как падение напряжения на Rd от входного тока элемента. Но напряжение на базе VTM не может быть больше 2,1В. Увеличение резистора приводит к увеличению входного напряжения, при достижении примерно 1,4В базово-эмиттерный переход закрывается, что эквивалентно подаче на вход высокого уровня наряженная. Входное напряжение 1.4В формируется на Rd при его величине большей 2кОм. Включение резистора между выходом элемента и шиной питания обязательно если используется элемент с открытым коллектором. Величина резистора в этом случае определяется нагрузкой, подключенной к выходу элемента. Подобное включение при использовании стандартного элемента применяется с целью повышения выходного напряжения.

Ш

Рис.16. Подключение резистора к

логическому элементу.

Для уменьшения влияния указанного явления рекомендуется на шины питания подключать блокировочные конденсаторы емкостью не менее 1мкФ из расчета один конденсатор на каждые пять-десять интегральных микросхем. С целью уменьшения влияния высокочастотных помех параллельно питанию микросхем рекомендуется устанавливать блокировочные конденсаторы (лучше керамические) из расчета один конденсатор на 10 микросхем. Величина емкости определяется из расчета 0,002 - 0,001мкФ на одну интегральную схему.

Лекция 8.