УСО и МК 2010

.pdf

|

|

|

21 |

|

|

|

|

|

|

|

|

|

|

|

|

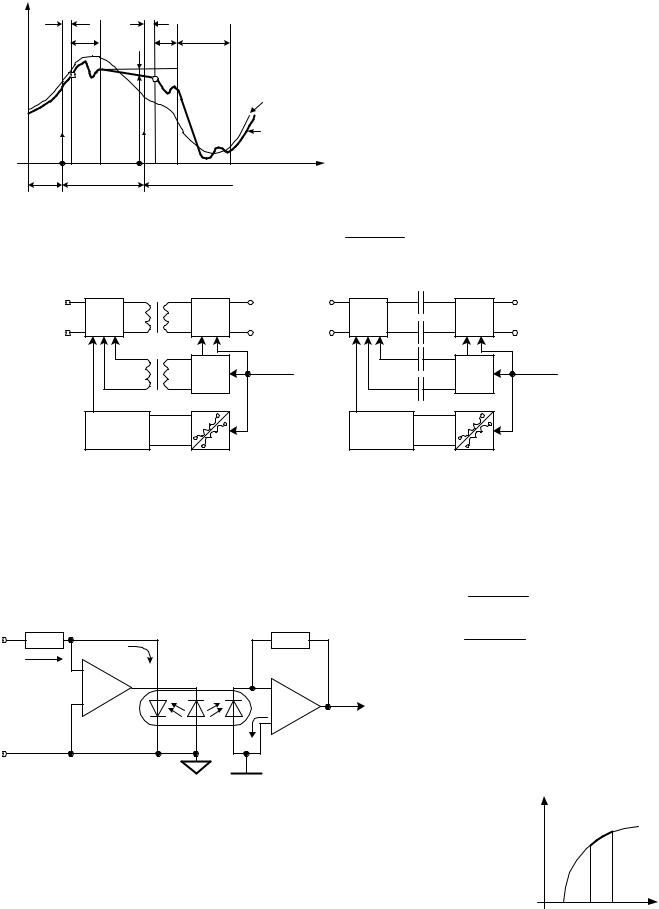

tА – апертурное время – время от выдачи сигна- |

|||||

U |

tА |

t А |

|

ла |

управления |

до |

замыкания |

(размыкания) |

ключа |

|

|

(десятки – сотни нс); |

|

|

|

||||||

|

tПЕР |

tПЕР |

t УСТ |

|

|

|

||||

|

|

tПЕР – время переходного процесса, вызванного |

||||||||

|

UВЫХ |

|

|

|

||||||

|

|

|

проникновением части управляющего сигнала в инфор- |

|||||||

|

|

|

|

мационную цепь через паразитную емкость; такое про- |

||||||

|

|

|

входной |

никновение приводит не только к колебаниям, но и к |

||||||

|

|

|

смещению запомненного сигнала; |

|

|

|||||

|

|

|

сигнал |

|

tУСТ – время установления выходного сигнала |

|||||

|

|

|

выходной |

равным входному (с заданной точностью) – это время |

||||||

t ХР |

t ИЗМ |

|

сигнал УВХ t |

от момента окончания переходного процесса до равен- |

||||||

выб. |

хранение |

выборка |

ства выходного напряжения входному. Так как это вре- |

|||||||

мя зависит от входного сигнала, то в паспортах приво- |

||||||||||

|

|

|

|

|||||||

|

|

|

|

дят максимальное значение tУСТ. |

|

|

||||

Режим хранения характеризуется скоростью изменения выходного напряжения (например, 5В/с).. |

|

|||||||||

|

|

|

|

|

|

vИЗМ = |

U |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tИЗМ |

− tХР |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

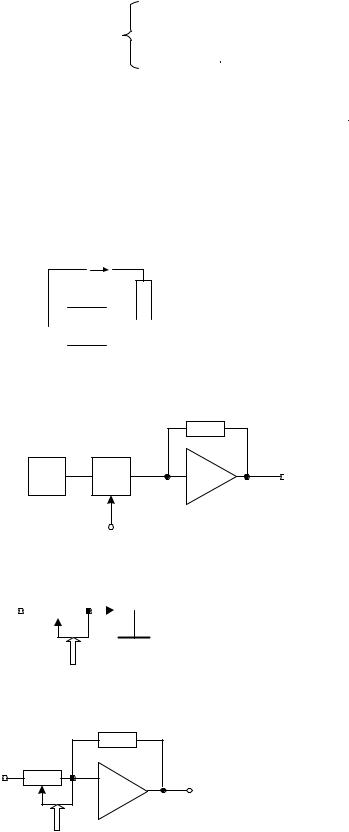

9.16 ИЗМЕРИТЕЛЬНЫЕ УСИЛИТЕЛИ С ГАЛЬВАНИЧЕСКОЙ РАЗВЯЗКОЙ |

|

|

|

|

|

|

||||||||||||

|

|

вх |

М |

ДМ |

вых |

вх |

М |

|

|

ДМ |

вых |

|

|

|

|

|

|

|

|

|

|

|

Г |

U |

П.ВЫХ |

|

|

|

|

Г |

U П.ВЫХ |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

U П.ВХ |

|

|

|

U П.ВХ |

|

|

|

|

|

|

|

|

|

|

|

|

|

В+Ф+СТ |

DC |

|

|

В+Ф+СТ |

DC |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

DC |

|

|

|

|

|

|

DC |

|

|

|

|

|

|

|

Гальваническое разделение аналоговых сигналов входа и выхода осуществляют с помощью оптоэлектронных |

||||||||||||||||||

схем, а также с помощью конденсаторов или трансформаторов, когда применяется структура с МДМ. |

|

|

|

|

||||||||||||||

9.17 ИЗОЛИРУЮЩИЕ УСИЛИТЕЛИ |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

DC/DC конвертор – преобразователь постоянного напряжения в постоянное. |

|

|

|

|

|

|

|

|||||||||||

Информационные, управляющие и питающие сигналы в такой схеме разделяют с помощью трансформаторов |

||||||||||||||||||

или конденсаторов. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Применяя согласованные оптопары, можно построить изолирующий усилитель без преобразования сигнала. |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

UВХ |

± U01 |

|

|

( |

) |

|

|

|

|

|

|

|

|

|

|

|

UВЫХ = R1 |

|

|

− I1 |

|

+ I2 |

± U02 |

||||

|

|

|

|

|

|

|

|

|

R |

|

± I0 |

1 + |

|

|||||

|

|

|

|

|

|

|

|

|

|

ВН |

|

|

|

|

|

|

||

R1 |

|

|

|

|

R 2 |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

UВХ ± U01 |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

IВХ |

= |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

R ВН |

|

|

|

|

|

|

|||

|

|

_ |

I1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

||

I |

|

|

|

|

|

U01, U02 – напряжения смещения усилителей |

||||||||||||

ВХ |

А1 |

|

|

|

|

|||||||||||||

|

|

|

|

|

_ А2 |

|

А1 и А2. |

|

|

|

|

|

|

|

|

|

|

|

U ВХ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

+ |

|

|

I |

|

|

I1, I2 – токи смещения усилителей А1 и А2. |

|||||||||||

|

|

|

|

2 |

|

I0 – суммарный ток смещения изолирующего |

||||||||||||

|

|

|

|

|

|

+ |

|

|||||||||||

|

|

|

|

|

|

|

усилителя. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- погрешность коэффициента передачи изо- |

||||||||||

|

|

|

|

|

|

|

|

лирующего усилителя. |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

RВН – входное сопротивление усилителя А1. |

||||||||||

Линейность изолирующего усилителя при нелинейной характеристике оптопары |

|

|

|

|

|

|

||||||||||||

обеспечивается глубокой отрицательной обратной связью, то есть светодиод работает в уз- |

|

IВЫХ |

|

|

|

|

||||||||||||

ком диапазоне токов IР, и тогда его передаточная характеристика практически линейна. При |

|

|

|

|

|

|

||||||||||||

погрешности линейности 0,1%, усилитель (без DC/DC конвертора) стоит 10$. |

|

|

|

|

|

|

|

|

|

|

||||||||

IР

IР

I ВХ

22

10 АНАЛОГО-ЦИФОРОВЫЕ ЭЛЕМЕНТЫ УСО

Кроме АЦП и ЦАП существует множество аналого-цифровых устройств для выполнения различных функциональных преобразований (например, перемножители напряжения и кода).

11 ЦИФРО-АНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ

UВЫХ=Е0 (К1 2-1+К2 2-2+… +Кn 2-n), где К={0, 1}

E0 – опорное напряжение

|

ЦАП с параллельным |

ЦАП с последовательным |

||||||||||||||

|

|

|

интерфейсом |

|

|

|

интерфейсом |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x 0 |

DAC |

U |

REF |

|

|

|

|

|

DIN |

DAC |

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

||||||||||||

|

|

|

x1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

цифровые |

|

|

|

R 0 |

|

|

|

|

|

DOUT |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

выход |

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

||||||

входы |

|

|

: |

|

OUT |

|

|

|

CLOCK |

|

OUT |

|

|

|||

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

||||||||||||

|

|

|

x n |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

U |

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

cc |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ucc− |

|

|

|

|

|

CS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

GND |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11.1 СИГМА-ДЕЛЬТА ЦАП (ΣΔ ЦАП)

Сигма-дельта ЦАП использует принцип цифро-аналогового преобразования на коммутируемых конденсаторах. Принцип действия заключается в формировании заряда выходного конденсатора из маленьких порций зарядов, передаваемых от эталонного источника в зависимости от весов разрядов входного кода.

Микросхемы ЦАП выпускаются:

1)с ненормированным токовым выходом (К572ПА1);

2)с нормированным токовым выходом (AD420, AD421);

U П

U П

R Н

ЦАП

ЦАП

Нормированный токовый выход (0-5мА; 0-20мА; 4-20мА) необходим для передачи аналоговых управляющих сигналов на большие расстояния (до нескольких сотен метров). Нормированный токовый сигнал формируется специальными схемами, состоящими из токового зеркала и дифференциального усилителя.

3) с выходом в форме напряжения (со встроенным выходным усилителем) (MAX505).

|

|

2R |

ИОН |

E 0 Сетка I ВЫХ |

U ВЫХ |

R-2R |

|

|

|

|

код

Резистивные сетки в ЦАП применяются по номиналам с целью обеспечения точного соотношения номиналов резисторов, а не их абсолютного базиса.

Фактически ЦАП представляет из себя переменный резистор, управляемый кодом.

UОП |

R |

IВЫХ |

N |

||

|

|

|

|

I ВЫХ = U ОП |

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|||

|

|

|

|

|

|

R - базовый резистор

код Выпускаются специальные ЦАП, имеющие название цифровой потенциометр. У них свободны все три вывода

резистивной сетки, а аналоговые ключи обеспечивают работу ЦАП при любых потенциалах на выводах потенциомет-

|

~R |

|

|

~R |

U ВЫХ = U ОП N |

UОП |

|

|

_ |

U ВЫХ |

|

|

|

|

|

+ |

|

|

код N |

|

23

ра (в пределах напряжения питания). Выходной ток имеет такой же разброс, как и базовый номинал R. Наименьшая величина выходного тока обычно 1мА и менее. Для обеспечения независимости выходного сигнала от базового номинала R применяют выходной усилитель с резистором в обратной связи пропорциональным базовому номиналу. В этом случае выходное напряжение не будет зависеть от базового номинала R.

Для получения выходного тока нормированного диапазона (0-5мА, 0-20мА, 4-20мА) применяют специальную схему, содержащую токовое зеркало или усилитель мощности. Схема с токовым зеркалом позволяет иметь заземленную нагрузку. В случаях, когда нагрузку заземлять не обязательно, применяют простую схему с датчиком тока – шунтом.

|

|

~R |

|

UОП |

~R |

_ |

|

|

I ВЫХ |

||

|

|

|

|

|

|

+ |

R Н |

|

|

|

|

|

код N |

|

|

R Ш

ЦАП выпускают с параллельным или с последовательным вводом кода.

ввод |

|

|

данных RG1 |

RG2 |

ЦАП |

Упр

Упр

Упр

Современные кристаллы ЦАП кроме резистивной сетки (непосредственно ЦАП) обязательно содержат параллельный регистр RG2, а некоторые ЦАП еще и приемный регистр RG1. Приемный регистр может быть параллельным или сдвигающим. Соответственно вводится информация в параллельном или последовательном коде. ЦАП с параллельным вводом информации и быстродействующими аналоговыми ключами применяют в быстродействующих системах, требующих время установления меньше 1 мкс. В применениях, не требующих высокого быстродействия, применяют дешевые технологии и медленный принцип преобразования (ΣΔЦАП) в сочетании с последовательным вводом. При последовательном вводе число линий связи уменьшается до трех или даже до двух. Сокращение числа линий связи значительно удешевляет гальваническую развязку, повышает надежность соединений, упрощает разводку плат и уменьшает число кабелей.

11.2 ЦАП С ДЕКОДИРУЮЩЕЙ СЕТКОЙ R-2R ДЛЯ СУММИРОВАНИЯ ТОКОВ

I1 |

S4 |

d |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

Допустим: |

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1) внутреннее сопротивление источ- |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- |

|

|

|

|

|

|

|

|

|

|

ников тока I1…I4 очень большое, то есть |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

при одновременном замыкании несколь- |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

S3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R 2 |

|

|

|

|

|

|

|

ких |

коммутаторов, они |

не |

оказывают |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

c |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

I 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

влияния друг на друга; |

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U ВЫХ |

|

2) все |

|

источники тока |

одинаковые |

|||||||

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

UΣ |

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I1=I2=I3=I4=I |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

S2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

При |

|

|

|

замыкании |

ключа |

S4: |

|||||||||

I3 |

b |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

2 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U |

d 4 |

= |

20 |

|

|

|

I R ; |

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

S1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

I 4 |

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

R |

|

|

|

2R |

|

|

2R |

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

I |

|

d |

|

|

|

|

|

|

|

|

|

|

|

|

|

Ud |

|

|

I |

|

|

|

|

|

|

|

|

d |

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U d |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

(R + R) 2R |

= R |

c |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

R |

|

||||||||||||||||

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

(R + R) + 2R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

= I |

2R R |

= I |

2 |

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U |

|

R |

||||||||||||||||

(R + R) 2R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d |

2R + R |

|

|

||||||||||||||||||||

= |

|

R |

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|||||||||||||||||||||

(R + R) + 2R |

|

|

|

|

R |

|

|

|

2R |

|

|

|

2R |

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Ud3 |

= |

|

|

|

|

I R ; |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

При замыкании ключа S3: |

|

|

2 |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

d |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U d |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

c |

|

|

|

|

|

R |

|

d |

|

R |

|

|

|

|||||

|

|

|

|

|

|

|

|

I |

|

c |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(R + R) 2R |

= R |

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

(R + R) + 2R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

b |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

U |

|

= |

2R R |

|

I = |

2 |

I R |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||

(R + R) 2R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

c |

2R + R |

|

|

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|||||||||||||||

= |

R |

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

(R + R) + 2R |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

1 |

2 |

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

R |

|

|

|

2R |

|

|

|

2R |

|

|

|

|

R |

|

|

U d |

= U c |

|

|

|

|

|

= |

|

|

|

|

|

I R |

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2R |

2 |

|

|

|

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

2 |

|

|

= |

1 |

|

|

2 |

I |

|

|

|

||||

Ud |

|

= |

|

|

|

I R |

Ud1 |

|

|

|

|

|

|

R |

|

|

|||

|

22 |

|

2 |

3 |

|

3 |

|

|

|||||||||||

Аналогично, при замыкании ключа S2 |

2 |

|

3 |

|

, а при замыкании ключа S1 |

|

|

|

|

|

|

|

. |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

n −1 |

|

1 2 |

|

|

|

||||||

|

|

|

|

|

|

|

Ud = |

|

|

|

|

|

|

|

|

I R |

|

||

|

|

|

|

|

|

|

∑ |

|

|

|

|

|

|||||||

При замыкании нескольких ключей Ud равно сумме найденных ранее напряжений: |

2n 3 |

|

|

. |

|||||||||||||||

i=0 |

|

|

|

|

|

|

|

|

|

||||||||||

11.3 ЦАП С РЕЗИСТОРНОЙ СЕТКОЙ С ДВОИЧНО-ВЗВЕШЕННЫМИ СОПРОТИВЛЕНИЯМИ ДЛЯ СУММИРОВАНИЯ ТОКОВ.

|

|

|

|

|

|

R OC = R |

UOП |

R |

S4 |

I4 |

IΣ |

IОС |

I |

|

|

|

|

|

|

- |

|

2R |

S3 |

I3 |

|

Ud |

|

|

|

|

|

+ |

||

|

|

|

|

|

|

|

|

4R |

S2 |

I2 |

|

|

|

|

|

|

|

|

||

|

8R |

|

|

|

|

U ВЫХ |

|

S1 |

I1 |

|

|

|

|

|

|

|

|

|

||

|

|

Регистр |

S |

|

|

|

|

|

|

|

|

||

Положим, что все ключи замкнутые, ключ S разомкнут. Схема работает в линейном режиме как сумматор.

IΣ = I4 = I3 = I2 = I1 .

Опираясь на замечательные свойства операционного усилителя, будем считать, что I→ 0, Ud→ 0.

UОП − Ud |

+ |

UОП − Ud |

+ |

|

UОП − Ud |

+ |

UОП − Ud |

= I |

Σ |

= I |

ОС |

+ I ; |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

R |

|

|

2R |

|

4R |

8R |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||

I |

ОС |

= |

UОП |

+ |

UОП |

+ |

UОП |

|

+ |

UОП |

; |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

R |

|

|

2R |

|

|

|

4R |

|

8R |

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

I |

ОС |

= Ud - UВЫХ |

− UВЫХ ; |

|

|

|

|

|

|

||||||||||||||||

|

|

|

RОС |

+ R |

|

|

|

|

R |

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

25

|

|

1 |

|

1 |

|

1 |

|

|

UВЫХ = −UОП 1 |

+ |

|

+ |

|

+ |

|

; |

|

2 |

4 |

8 |

||||||

|

|

|

|

|

Если замкнут один или несколько ключей, то сигнал UВЫХ определяется соответствующей суммой. Схема сумматора проста, и это достоинство, но характеризуется сложностью в исполнении, так как резисторы крайних разрядов сильно отличаются сопротивлениями. На практике сложно подобрать с высокой точностью резисторы с двоич- но-взвешенными номиналами сопротивлений. В рассмотренном случае:

R = 10 кОм ± 10%, то есть ± 100 Ом;

R = 80 кОм ± 10%, то есть ± 800 Ом.

Кроме того, резисторы характеризуются температурным коэффициентом сопротивления (ТКС), а резисторы с малым ТКС дороги.

12 АНАЛОГО-ЦИФРОВЫЕ ПРЕОБРАЗОВАТЕЛИ (АЦП)

По принципу преобразования АЦП .(Analog-to-Digital Converters или ADC) разделяют на 3 класса:

1)прямого преобразования;

2)уравновешивающего преобразования;

3)развертывающего преобразования.

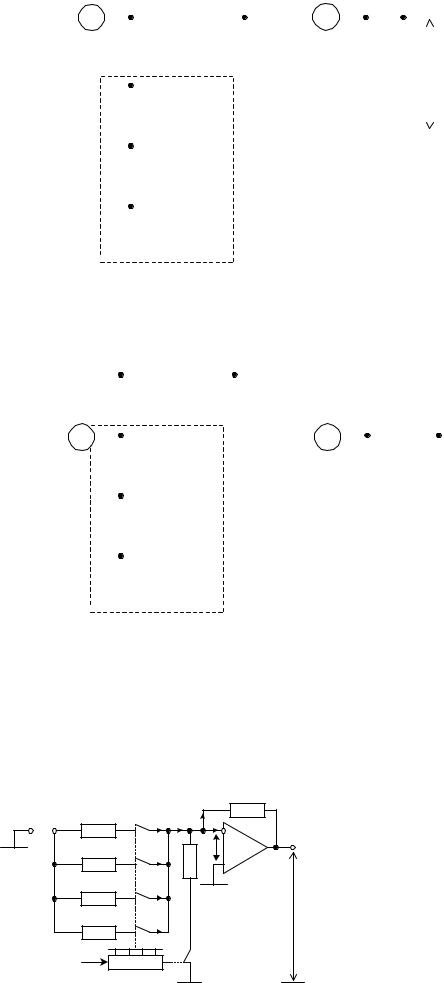

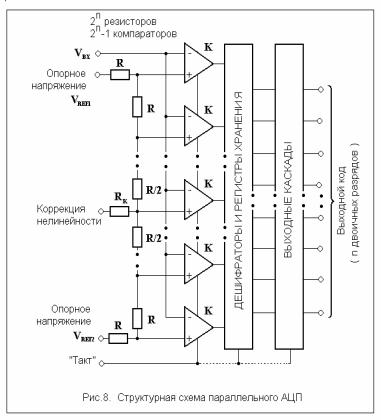

12.1АЦП ПРЯМОГО ПРЕОБРАЗОВАНИЯ (ПАРАЛЛЕЛЬНЫЕ АЦП).

Параллельные АЦП в основном состоят из следующих узлов: делитель опорных напряжений, выполненный на резисторах R; набор компараторов напряжения; дешифратор; выходные каскады. Для получения более высокой полосы пропускания, при сохранении чувствительности, компараторы делают стробируемыми (рис.8). Возможно стробирование и других блоков.

АЦП работает по следующему принципу: входное напряжение одновременно подается на неинвертирующие входы компараторов, которые производят сравнение этого сигнала с напряжениями, поступающими с резистивного делителя напряжений на инвертирующие входы, в момент подачи стробирующего сигнала на тактовый вход. Дешифратор преобразует код, поступающий с выходов компараторов в двоичный код. Код с выхода дешифратора поступает на выходные каскады, которые преобразуют внутрисхемные уровни в стандартные уровни ЭСЛ, ТТЛ или КМОП. Также выходные каскады могут содержать интерфейсные схемы для связи с микропроцессорами.

Главное преимущество: самое высокое быстродействие (время преобразования измеряется единицами нс).

Частота преобразования: 100 Msps (Million samples per second).

Недостатками являются:

•самая высокая сложность схемотехники (например, для 12-разрядного АЦП требуется 212 компараторов, 212 источников опорного напряжения (ИОН), а также сложная комбинационная схема шифратора (212 входов и 12 выходов), выполненная на сверхбыстродействующей логике ЭСЛ и ВКМОП);

•самое высокое энергопотребление (несколько Вт).

Опомехоустойчивости речи не ведется, так как АЦП прямого преобразования не допускает никаких задерживающих (фильтрующих) элементов.

Сфера применения: цифровое телевидение, радиолокация.

26

12.2 АЦП УРАВНОВЕШИВАЮЩЕГО ПРЕОБРАЗОВАНИЯ.

Принцип действия таких АЦП основан на последовательном подборе образцовых напряжений до момента равенства измеряемому напряжению. Таким образом, АЦП должен содержать такое количество образцовых напряжений, какое количество уровней измеряемого напряжения он должен различать. 10-разрядный АЦП должен иметь 210 образцовых напряжений. Отличие АЦП уравновешивающего преобразования от АЦП прямого преобразования заключается в том, что образцовые напряжения нужны не одновременно, а по очереди. Это позволяет использовать один источник опорного напряжения и ЦАП для последовательного получения частей этого опорного напряжения. Основной представитель такого класса АЦП – это АЦП поразрядного уравновешивания, в состав которого входит ЦАП (разрядность которого соответствует требуемой разрядности АЦП), компаратор напряжений и регистр, реализующий алгоритм последовательных приближений, а также тактовый генератор. Быстродействие АЦП последовательного приближения ближе к АЦП прямого преобразования и составляет от 10 Ksps до 10 Msps. Главным требованием правильной работы таких АЦП является неизменность входного сигнала в течение всего времени преобразования. Поэтому обязательным является включение УВХ на входе такого АЦП. Лучше выбирать кристалл АЦП со встроенным УВХ.

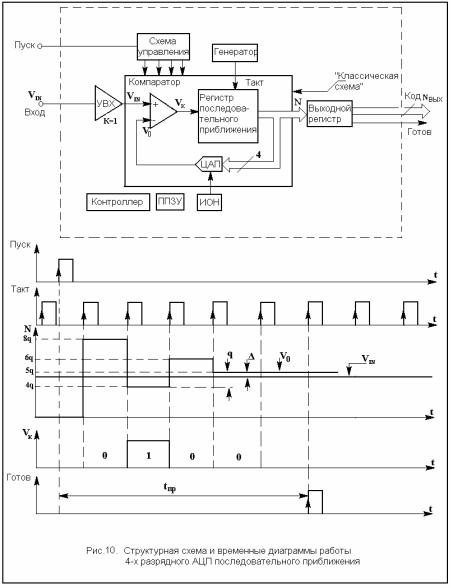

12.2.1 АЦП ПОСЛЕДОВАТЕЛЬНОГО ПРИБЛИЖЕНИЯ (ПОРЯЗРЯДНОГО УРАВНОВЕШИВАНИЯ) В литературе могут

называться также АЦП поразрядного уравновешивания, кодоимпульсные АЦП. Рассмотрим принцип работы АЦП последовательного приближения на примере классической структуры (рис.10) четырехразрядного преобразователя, состоящего из трех основных блоков: компаратора, регистра последовательного приближения (РПП) и цифроаналогового преобразователя (ЦАП). После подачи команды “пуск” с приходом первого тактового импульса РПП принудительно задает на вход ЦАП код, соответствующий половине его шкалы (для 4-разрядного АЦП это 8q). Входное напряжение подается на один из входов компаратора, сравнивается с выходным напряжением ЦАП, поступающим на другой вход компаратора. Вырабатываемый при этом на выходе компаратора сигнал (“0” или “1”) показывает, увеличивать или уменьшать код,

подаваемый с РПП на ЦАП, причем каждый раз подается код, в два раза отличающийся от предыдущего. Количество шагов приближения соответствует количеству двоичных разрядов.

Точность и быстродействие таких АЦП определяется в основном метрологическим характеристиками ЦАП и технологией производства.

Наиболее существенным недостатком АЦП, выполненных по простейшей (классической) схеме (см. рис.10), является большая апертурная неопределенность, равная примерно времени цикла кодирования, что резко ограничивает частотный диапазон входных сигналов АЦП. Апертурная неопределенность уменьшается на 2 - 4 порядка при применении УВХ на входе АЦП, что попутно существенно увеличивает входное сопротивление. Классическая структура также может дополняться встроенными источниками опорного напряжения, генераторами тактовых импульсов, выходными трехстабильными буферными регистрами, схемами памяти и калибровки и пр. Выходные регистры предназначены для связи с микропроцессорными системами.

27

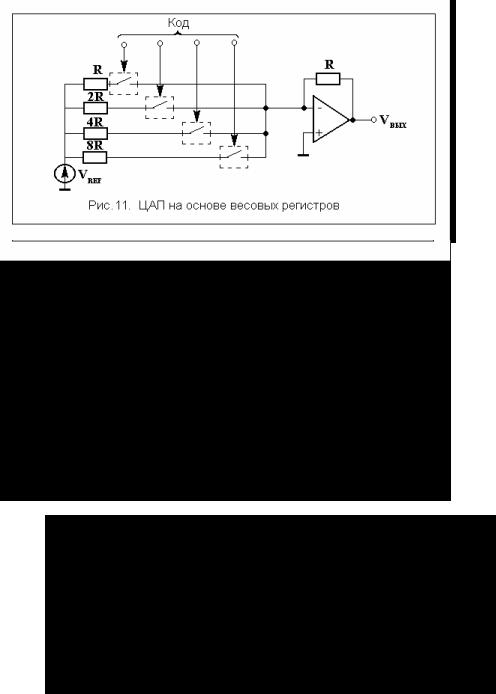

Практически все метрологические характеристики таких АЦП определяются параметрами внутреннего ЦАП. Наиболее широкое распространение при построении АЦП получили ЦАП, построенные на основе “весовых” резисторов (рис. 11) и на основе рези-

стивной матрицы типа R-2R (рис. 12). В обоих случаях для увеличения точности и стабильности применяется лазерная подгонка резисторов. Обойтись без этой сложной операции позволяют ЦАП, построенные на основе метода перераспределения заряда, со схемой самокалибровки (рис. 13). Такой ЦАП реализован на конденсаторной матрице с отношением емкостей, кратным 2n. Данный ЦАП выполняет также функцию вы- борки-хранения, т.е. необходимостьв УВХв УВХотсутствует. .

Возможно повышение быстродействия АЦП последовательного приближения за счет применения переменной тактовой частоты. Объясняется это тем, что для таких АЦП время определения одного разряда результата складывается из времени срабатывания логики АЦП (t LOG ) и времени установления (t DAC ).

Время t LOG является величиной постоянной, а t DAC уменьшается с уменьшением веса разряда. Следовательно, для определения младших разрядов может быть использована более высокая тактовая частота.

Результаты экспериментов показывают, что при использовании двух тактовых частот (f = 2f) возможно уменьшение t пр на 20%. При вариации f поразрядно, возможно уменьшение t пр на 40%. Для этого в схему АЦП добавляют ППЗУ со встроенным регистром, которые задают алгоритм работы АЦП.

12.3 АЦП РАЗВЕРТЫВАЮЩЕГО ПРЕОБРАЗОВАНИЯ.

12.3.1 ИНТЕГРИРУЮЩИЕ АЦП.

Интегрирующие АЦП относятся к классу развертывающих. Интегрироваться (развертываться) во времени может либо входной, либо опорный сигнал Промежуток времени между началом развертывания и моментом равенства является промежуточным результатом. Преобразование в код производится либо подсчетом этих интервалов, либо измерением длительности интервала. Различают АЦП с промежуточным времяимпульсным преобразованием (ВИП) и промежуточным частотно-импульсным преобразованием (ЧИП).

Преимущества:

•самая простая схемотехника;

•дешевизна;

•высокая линейность, монотонность характеристики;

•высокая точность (интегрирующие АЦП выпускаются на 24-26 двоичных разрядов с соответствующей точностью).

•высокая помехоустойчивость.

Недостаток: низкое быстродействие.

28

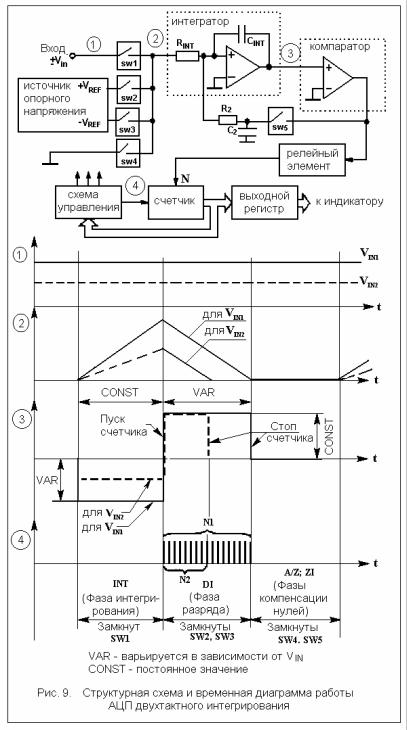

Своим названием преобразователи обязаны наличию в своей структуре интегратора. Большинство современных микросхем работает в два такта интегрирования, что позволяет называть их АЦП двухтактного интегрирования.

Микросхемы, построенные по такому принципу, совместно с источником опорного напряжения (ИОН), несколькими резисторами и конденсаторами предназначены для применения в измерительных приборах напряжения, тока, сопротивления, температуры, веса и других параметров с выводом информации на жидкокристаллические (ЖКИ) или светодиодные (СДИ) индикаторы. Некоторые преобразователи выдают информацию в двоично-десятичном коде.

Преобразователь состоит из аналоговой части (ключи SW1...4, источники опорных напряжений +VREF и -VREF, интегратор, компаратор схема компенсации нуля SW5, R2, C2) и цифровой части

(рис. 9).

Цикл аналого-цифрового преобразования состоит из четырех фаз:

1 - фаза A/Z автоматической коррекции погрешности;

2 - фаза INT интегрирования входного напряжения в течение фиксированного времени Т1;

3 - фаза DI интегрирования опорного напряжения, т.е. разряда интегрирующего конденсатора за время Т2;

4 - фаза ZI коррекции нуля интегратора.

Необходимо отметить, что в первых микросхемах преобразование осуществлялось в 3 фазы, то есть четвертая фаза (ZI) - коррекция нуля интегратора - отсутствовала, что приводило к возникновению по-

грешности гистерезиса из-за дрейфа интегратора и компаратора. Это можно наблюдать как появление одного и того же выходного кода при разных значениях входного напряжения в зависимости от того, с какой стороны напряжение подходит к этой точке. Рабочие фазы интегрирующего АЦП устанавливаются с помощью аналоговых переключателей, управляемых сигналами из цифровой части.

Цифровой эквивалент аналогового сигнала: N = VIN × T2 / VREF × T1 .

Для увеличения входного сопротивления на входе преобразователя ставится повторитель напряжения, который на приведенной схеме не указан.

В настоящее время выпускаются приборы, работающие как от однополярного, так и двуполярного напряжения. Низкое потребление делает такие приборы незаменимыми при построении переносных приборов с автономным питанием, которые могут работать от одной батарейки на протяжении нескольких лет.

У многих преобразователей цифровая информация на выходе представлена в специальном коде, предназначенном для непосредственного управления цифровым табло с 7-сегментными индикаторами. Диапазон входного сигнала определяется значением внешнего опорного напряжения.

Для увеличения коэффициента подавления помехи нормального вида рекомендуется время преобразования выбирать равным или кратным периоду помехи (см. описание 572ПВ2 (ICL 7106)), чаще всего это период питающей сети, т.е. 50 или 60Гц.

К недостаткам такого рода преобразователей можно отнести высокие требования к качеству СINT , невысокое быстродействие и такой факт, что если на преобразователь подается входное напряжение, изменяющееся скачкообразно от значения, соответствующего этому участку, то в течение нескольких первых циклов преобразования оста-

29

точное напряжение на конденсаторе СINT может вносить значительную погрешность в измерение. Влияние перегрузки полностью устранится только через несколько полных циклов преобразования. Помимо автоматической коррекции нуля и автоматического определения полярности входного сигнала современные преобразователи снабжаются схемами автоматического выбора предела измерения с выдачей информации о положении десятичной точки, имеют входы управления режимом запоминания результата на индикаторе (HOLD) и выбора диапазона измерения (RANG), а также возможность работать в приборах, предназначенных для измерения частоты, значений емкости и индуктивности.

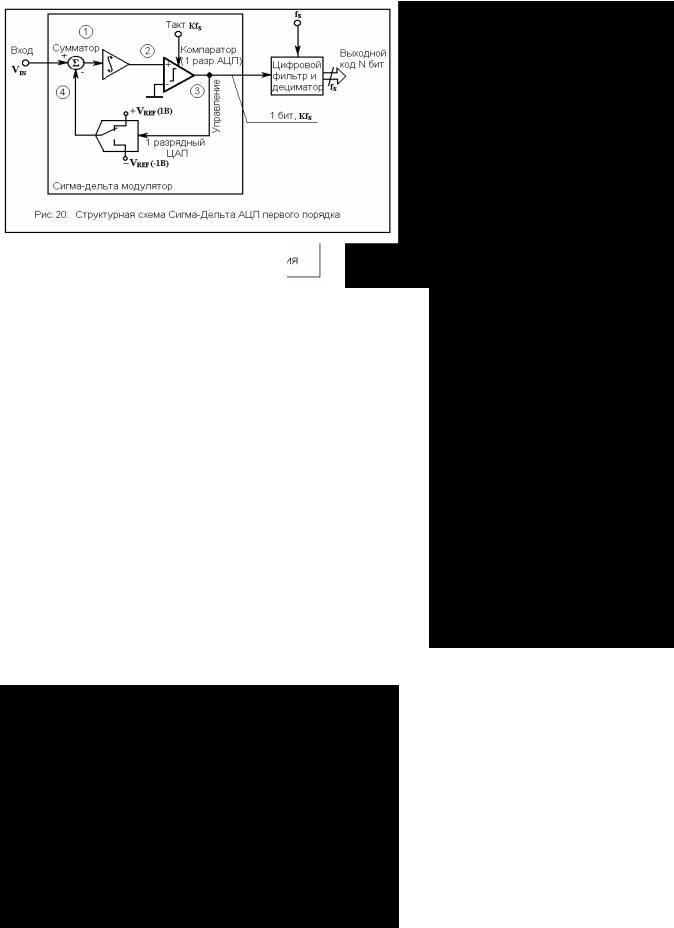

12.3.2 СИГМА-ДЕЛЬТА АЦП.

ΣΔАЦП относятся к классу интегрирующих. В них процедура интегрирования разбивается на множество мелких тактов или одноразрядных шагов.

Своим названием такие преобразователи обязаны наличию в них двух блоков: “сигма” - наличие интегратора, “дельта” - наличие дифференциального усилителя. Один из принципов, заложенных в такого рода преобразователях, позволяющий уменьшить погрешность, вносимую шумами, а следовательно, увеличить разрешающую способность - это усреднение результатов измерения. Проиллюстрировать это можно на методе Гетти, когда на входной сигнал АЦП накладывается при помощи дополнительного ЦАП равномерно распределенный шумовой сигнал размахом больше 1 МЗР (рис.18). При выполнении большого числа преобразований с последую-

щим усреднением получается дробное значение МЗР (q/4 на рисунке).

Второй важный момент - это автоматический перенос спектра шума квантования в более высокочастотную область при высококачественной дискретизации низкочастотного сигна-

ла (рис.19).

Принцип действия сигма-дельта АЦП первого порядка (рис.20) состоит в том, что в аналоговую схему с отрицательной обратной связью и высоким коэффициентом усиления при разомкнутой обратной связи включен одноразрядный ЦАП (фактически - ключ и два источника опорного напряжения +VREF и -VREF), который стремится свести к нулю значение напряжения на входе интегратора.

Принцип действия пояснен на примере преобразования входного сигнала, равного 0.6В (см. таблицу).

В нулевом тактовом периоде выходы интегратора и ЦАП “заземляются” и на них задается строго определенное исходное состояние. Затем система проходит через показанную (см. таблицу) последовательность состояний. В тактовые периоды 2 и 7 состояния системы идентичны, так как при неизменном входном сигнале цикл работы занимает 5 тактовых периодов. Усреднение выходного сигнала ЦАП за цикл, действительно, дает величину напряжения 0,6В: (+1-1+1+1+1) : 5 = 0.6 .

Для работы такого преобразователя необходимо, чтобы его входной сигнал за время усреднения можно было считать постоянным, т.е. частота выборки должна быть намного

больше частоты входного сигнала.

Если выполнить это условие, то для превращения потока битов в десятичный сигнал можно воспользоваться фильтром низких частот (ФНЧ). На приведенном рисунке это цифровой фильтр. К достоинствам схем, работающих по такому принципу, можно отнести: возможность увеличения разрешающей способности за счет увеличения времени интегрирования, большую по сравнению с АЦП двухтактного или многотактного интегрирования скорость преобразования (на 3 порядка), небольшую стоимость, малое количество аналоговых структур, устранение влияния помех от источников питания за счет наличия фильтров.

30

Таблица

Тактовый период |

Выходное напря- |

Выходное напря- |

Выходное напря- |

Выход |

|

жение сумматора |

жение интегратора |

жение компаратора |

ЦАП |

|

(1) , В |

(2) , В |

(3) , В |

(4) , В |

1 |

0,6 |

0,6 |

1 |

+1 |

2 |

-0,4 |

0,2 |

1 |

+1 |

3 |

-0,4 |

-0,2 |

0 |

-1 |

4 |

1,6 |

1,4 |

1 |

+1 |

5 |

-0,4 |

1,0 |

1 |

+1 |

6 |

-0,4 |

0,6 |

1 |

+1 |

7 |

-0,4 |

0,2 |

1 |

+1 |

8 |

-0,4 |

-0,2 |

0 |

-1 |

Самый быстродействующий 24-разрядный сигма-дельта АЦП выпускается на максимальную частоту дискре-

тизации 40 кГц (AD7731).

12.4 СТАТИЧЕСКИЕ ХАРАКТЕРИСТИКИ АЦП.

Трактовка многих терминов, определений и способов нормирования погрешностей АЦП существенно различается у разных производителей и у потребителей в разных областях применения АЦП. В данном руководстве приняты определения, данные в работе [ 3 ].

Характеристика преобразования АЦП - это зависимость между напряжением на его аналоговом входе и множеством возможных значений выходного кода, заданная в виде таблицы, графика или формулы.

Различают номинальную характеристику преобразования (рис.1), установленную в стандартах или технических условиях на АЦП конкретного типа, и действительную характеристику преобразования, найденную экспериментальным путем и настолько приближенную к истинной характеристике преобразования конкретного АЦП, что для данной цели может быть использована вместо нее [7].

Количество разрядов. Для наиболее распространенных двоичных АЦП число разрядов равно двоичному логарифму максимального числа возможных кодовых комбинаций на выходе АЦП. Применительно к АЦП, вырабатывающим другие числовые коды, вводят число, эквивалентное увеличенному до целого двоичному логарифму номинального числа возможных значений выходного кода.

Разрешающая способ-

ность - величина, обратная максимальному числу кодовых комбинаций на выходе АЦП. Разрешающая способность выражается в процентах, разрядах или децибеллах и характеризует потенциальные возможности АЦП с точки зрения достижимой точности. Например, 12-разрядный АЦП имеет разрешающую способ-

ность 1/4096, или 0.0245% от полной шкалы, или -72.2 дБ.

Погрешность квантова-

ния зависит от количества разрядов (рис. 2).

Одним из фундаментальных понятий, на котором базируются определения основных метрологических характеристик

АЦП, является значение напряжения межкодового перехода - определенное по характеристике преобразования значение напряжения на аналоговом входе, соответствующее переходу от предыдущего к заданному значению выходного кода. Разность значений напряжений межкодовых переходов (V i-1,i - V i,i+1) называют значением кванта преобразования (шагом квантования, ступенью квантования).

Номинальное значение кванта преобразования ( q H ) равно:

q H = (V N-1,N - V 0,1 ) / (N - 2) = V REF /2 n-1,

где N - номинальное число возможных значений выходного кода;

V 0,1 и V N-1,N - номинальные значения напряжений межкодовых переходов от нулевого к первому и от предпоследнего кода к последнему.

Если в данной формуле заменить номинальное значение напряжений действительными, то получим среднее действительное значение кванта преобразования. Номинальное значение кванта преобразования называют единицей младшего разряда или Младшим Значащим Разрядом (МЗР).

В связи с тем, что данное выше определение для произвольно заданной точки характеристики преобразования АЦП не может быть использовано для начальной и конечной точек характеристики преобразования, то их задают следующим образом.