Параллельные порты цифрового ввода/вывода (цвв)

1. Типовой порт цвв

Универсальные порты ввода/вывода позволяют PIC-микроконтроллерам контролировать работу и управлять другими устройствами передавая им или принимая от них данные в параллельном коде, т.е. в виде напряжений одновременно на нескольких контактах порта. Максимальная разрядность порта определяется разрядностью шины данных. В микроконтроллерах PIC16 порты ЦВВ имеют разрядность до одного байта, т.е. до восьми разрядов. С целью расширения функциональных возможностей микроконтроллера некоторые каналы портов ввода/вывода мультиплицированы с другими периферийными модулями, которые влияют на их свойства и структуру. Поэтому все порты несколько различаются по свойствам и разрядности. В некоторых портах даже отдельные разряды могут иметь индивидуальные особенности. Для изучения свойств конкретного порта надо рассматривать его индивидуальное описание. Тем не менее, все разряды портов построены на основании типовой структуры одного разряда, приведенной на рис. 1. Типовой порт считается восьмиразрядным.

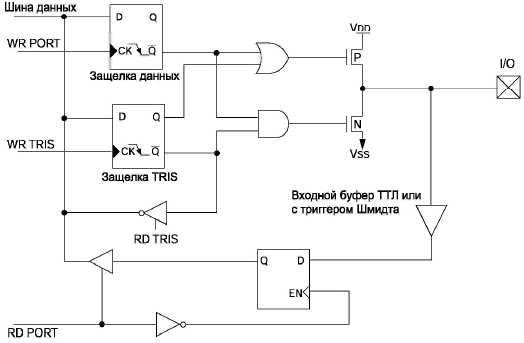

Рис. 1. Типовая структурная схема одного разряда порта ввода/вывода

Для управляющей программы каждый порт ЦВВ представлен двумя специальными регистрами памяти данных:

Регистр PORTx, в который выводимый байт записывается через шину данных по сигналу управления шиной WR PORT, который вырабатывается автоматически ядром микропроцессора при выполнении команды записи в регистр PORTx. На рис.1 из технического описания один разряд его изображен в виде синхронного D-триггера и называется “ Защелка данных”. Данные из регистра PORTx через логическую схему состоящую из логических элементов И и ИЛИ поступают в выходной усилитель на комплементарных полевых транзисторах, соединенных стоками между собой и с соответствующим выводом I/O на корпусе микропроцессора.

Регистр TRISx служит для управления направлением передачи данных, т.е. он устанавливает режим или вывода данных из микропроцессора, или ввода. На рис. 1 отдельный разряд этого регистра называется “Защелка TRIS”. Запись восьмиразрядного кода в регистр TRISx производится по синхроимпульсу WR TRIS из ядра микропроцессора. Каждый разряд может устанавливаться в '0' или '1' независимо от других разрядов. Это позволяет индивидуально устанавливать направление ввода/вывода для каждого разряда выбранного порта. Если бит TRIS установлен в '1' то соответствующий канал порта ввода/вывода работает как вход, а если бит TRIS сброшен в '0', то канал ввода/вывода работает как выход. В состоянии '1' напряжения с выхода разряда TRISx через логическую схему запирают оба транзистора выходного усилителя, запрещая таким образом передачу сигнала от регистра PORTx и отключая выходной усилитель от вывода. В состоянии равном '0' напряжения с разряда TRISx через логическую схему разрешают прохождение сигнала от PORTx на вывод соответствующего разряда ЦВВ.

Легко запомнить связь направления ввода/вывода и состояния битов регистров TRIS, если учесть что '1' - напоминает'In' (ввод), а '0' - напоминает 'Оut' (выход).

Чтение данных в режиме ввода производится по синхроимпульсу RD PORT через управляемый усилитель, который через схему формирования входного сигнала и триггер (защелку) считывает напряжение с контакта разряда ЦВВ. Сигнал с триггера поступает в шину данных через формирующий усилитель, управляемый тем же синхроимпульсом RD PORT.

В описанном режиме работает большинство разрядов портов ЦВВ, однако необходимость мультиплицирования контактов накладывает дополнительные особенности на работу отдельных разрядов ЦВВ. Если устройство микроконтроллера, использующее общий вывод с данным разрядом ЦВВ, отключено, то оно обычно не оказывает влияния на работу ЦВВ. Этот режим работы ЦВВ для всех разрядов устанавливается после импульса начального сброса микроконтроллера, если слово конфигурации (Config) задано по умолчанию. Так как включение и выключение периферийных устройств производится с помощью специальных регистров закрепленных за этими устройствами точно определить их влияние на порты ЦВВ можно только по описаниям периферийных устройств.

При включении периферийных устройств они обычно используют мультиплицированный вывод в монопольном режиме и использование этого контакта для вывода данных через соответствующий разряд ЦВВ недопустимо. Чтобы не нарушать работу микроконтроллера, этот разряд необходимо перевести в режим ввода, занеся 1 в соответствующий разряд регистра TRISx. При этом будут заперты оба транзистора выходного буфера. Напряжение на выводе будет определяться только сигналами периферийного устройства или внешними сигналами.