- •Архитектура 32-битных микропроцессоров семейства Intel ia-32. Часть 1

- •Структура микропроцессоров ia-32

- •Регистры

- •Формат команды микропроцессора ia-32

- •Вопросы для самоконтроля

- •Режимы работы

- •Реальный режим (Real Mode)

- •Режим системного управления (System Management Mode)

- •Защищенный режим (Protected Mode)

- •Вопросы для самоконтроля

- •Конвейеризация команд

- •Динамическое (спекулятивное) исполнение

- •Вопросы для самоконтроля

- •Организация и режимы работы процессоров семейства Pentium

- •Динамическое исполнение программ в процессоре Pentium Pro

- •Simd-расширения архитектуры ia-32

- •Микроархитектура NetBurst

- •Архитектурные особенности процессоров семейства Pentium

- •Инициализация пэвм на базе i86-х

- •Вопросы для самоконтоля

Лекц2Аппаратные платформы и архитектура IA32

Аппаратная платформа компьютера (архитектура компьютера) — уровень, образованный микроархитектурой, микропрограммой управления ядром микропроцессора и архитектурой набора команд на аппаратной базе конкретных микросхем процессора, чипсета, других физических компонентов, которые в совокупности составляют аппаратную модель вычислительной системы.Предназначен для запуска определенных семейств программных продуктов (операционная система, прикладное программное обеспечение), которые, в свою очередь, разработаны исходя из возможностей и для запуска на данной аппаратуре.

Конкретно, аппаратные платформы отличаются друг от друга совокупностью аппаратуры (процессором, чипсетом), а также разработанными (и запускаемыми) программными компонентами.

Содержание

1 Платформы-бренды

2 Платформы-анклавы

3 Несовместимые аппаратные платформы

3.1 Несовместимость кода, выполняемого процессором

3.2 Несовместимость устройств и материнских плат

4 Кроссплатформенное программное обеспечение

5 Литература

6 См. также

7 Ссылки

Платформы-бренды

Одной из наиболее распространённых офисных платформ и персональных компьютеров является IBM PC. На рынке персональных компьютеров также распространены компьютеры Apple. Эти платформы являются широко известными брендами.

|

Аппаратная платформа |

Актуальность |

Разработчик |

Разрядность, бит |

Типы систем |

Год начала производства |

Снятия с производства |

Примечания |

|

Amiga |

Нет |

Commodore International, Escom, MacroSystem |

32 |

ПК, игровая приставка, сервер |

1985 |

1996 |

Архитектура «классических» Amiga на процессорах m68k. В производстве имеется клон на современной элементой базе (MiniMig)) |

|

Amiga PowerPC |

Да |

Eyetech Group, Genesi, bPlan GmBH, ACube Systems Srl |

32/64 |

ПК |

2002 |

В производстве |

Современные Amiga работающие на процессорах PowerPC. |

|

IA-32 |

Да |

Intel |

32 |

ПК, сервер, ноутбук, кластер |

1985 |

? |

Доминирующая архитектура в мире Windows |

|

x86-64 |

Да |

AMD |

64 |

ПК, сервер, ноутбук, кластер |

2003 |

В производстве |

Обратная совместимость с i386. Широко производимая, но, из-за отсутствия 64 bit драйверов для некоторых устройств, реже используемая архитектура. |

|

SPARCv8 |

Нет |

Sun Microsystems |

32 |

рабочая станция,сервер |

1992 |

? |

|

|

SPARCv9 |

Да |

Sun Microsystems |

64 |

рабочая станция,сервер |

1994 |

В производстве |

|

|

IA-64 |

Да |

Intel и Hewlett Packard |

64 |

сервер |

2001 |

В производстве |

Разрабатывалась на смену 32 битных CPU Intel, но не совместима с i386. Потеряла важность с появлением x86-64 |

|

Alpha |

Нет |

DEC |

64 |

рабочая станция, сервер |

1992 |

27 октября 2007 года |

|

|

ESA/390 |

Да |

IBM |

32 |

мейнфрейм |

1990 |

? |

Обратно совместим с System/360 и ESA/370. Фирмами среднего размера применяется для хранения данных и виртуализации серверов (LPAR). |

|

z/Architecture |

Да |

IBM |

64 |

мейнфрейм |

2000 |

В производстве |

Обратно совместим с ESA/390. Применяют до 60 LPAR. Возможно несколько машин этого класса объединить в кластер. |

|

Xbox 360 |

Да |

Microsoft в сотрудничестве IBM, ATI и SiS |

64 |

игровая приставка |

2005 |

В производстве |

CPU Xenon с архитектурой PowerPC, 3 ядра с двумя аппаратными потоками на каждое, 3,2 ГГц. Заявленная суммарная производительность системы — 1 ТFLOPS (производительность CPU — 115 Гфлопс). Частично совместим с Xbox. |

|

PlayStation 3 |

Да |

Sony в сотрудничестве с Toshiba и IBM |

64 |

игровая приставка |

2006 |

В производстве |

Частично совместима с PlayStation и PlayStation2. 2 Тфлопс. CPU Cell. GPU RSX от NVidia. |

|

Famicom (Dendy в России) |

Нет |

Nintendo, Масэюки Уэмурой |

8 |

игровая приставка |

1983 |

В производстве |

Процессор 6502 1,79 МГц, ОЗУ 2 Кб, картридж ПЗУ 48 Кб, видеопамять 2 Кб, 256×240 пикселов, 48 цветов, пятиканальный звукогенератор. |

|

Motorola 68xxx |

Нет |

Apple |

16 |

ПК |

1984 |

1996 |

ПК Apple Macintosh под управлением Mac OS Classic версий до 7.5.1 |

|

PowerPC |

Нет |

Apple |

32 |

ПК, сервер |

1996 |

2006 |

ПК и сервера Apple Macintosh под управлением Mac OS Classic версии 8, версии 9 и Mac OS X для платформы PowerPC. |

Платформы-анклавы

Иногда ветвь CPU прекращает развитие, и может возникнуть компьютерный анклав, то есть пользователи по-прежнему любят свои компьютеры или не могут от них отказаться. Технический прогресс в анклаве замедлен или полностью остановлен. Железо компьютерного анклава на уровне машинных кодов не совместимо с мейнстрим платформами и постепенно морально стареет. Это значит, что у пользователей есть большой соблазн сменить платформу. Программисты если и пишут новый софт, то, как правило, на свободных, нежели коммерческих, началах.

Анклав Commodore 64 во многом обязан своему существованию возможности писать музыку на этом компьютере 1982 года выпуска. Немецкая группа Welle:Erdball, играющая в стиле Synthpop, пишет пять своих участников — пятым, всегда и везде указываемым в списке музыкантом, является компьютер Commodore 64.

8-битные процессоры Intel, такие как 8080 и 8085, несовместимы с 8086 и другими 16-битными процессорами Intel. Сегодня 8080 и 8085 являются анклавом. Примером из анклава может быть компьютер MFA с процессором 8085. Он по-прежнему применяется студентами для изучения функционирования ЭВМ. Несовместимые с архитектурой IA-32 процессоры/платформы линий iAPX 432, i960 и i860, тоже ушедшие в прошлое, по разным причинам анклавов не образуют.

ZX Spectrum, будучи созданным в 1982, применяется любителями до сих пор. Процессоров Z-80 произведено более миллиарда. В мире огромное число клонов ZX Spectrum, многие из которых сделаны в СССР и России. Современный спектрум имеет CD привод, модем и существует во многом благодаря участию в Демосцене, которая в РФ получила огромную популярность именно на ZX Spectrum. Таким образом, хотя ZX Spectrum не слишком активно совершенствуется технически, но остаётся полотном для компьютерного искусства.

Несовместимые аппаратные платформы

Аппаратные платформы несовместимы в случае различия программной модели процессора, а также различия системных шин и устройств на материнской плате.

Несовместимость кода, выполняемого процессором

Корпорация Intel, развивая свои семейства процессоров, наполняет процессоры дополнительными командами: команды математического сопроцессора (FPU); команды оптимизированные для обработки мультимедийного контента (MMX); серии команд SSE (SSE, SSE2, SSE3, SSE4 и SSE5); поддерживаемые только AMD команды 3DNow!, а также 64-битный набор команд AMD64. Новые команды серьёзно влияют на совместимость процессоров, поэтому разработчикам программного обеспечения приходится ориентироваться на две платформы, более старую и «многочисленную» IA-32 и новую, перспективную x86-64. Проблема совместимости кода — ситуация, когда процессоры различных семейств не могут выполнять один и тот же машинный код. Например, между двумя 32-битными процессорами одного и того же производителя, Intel — Pentium и Pentium 2, может возникнуть несовместимость по причине присущего ограничения (аппаратного отсутствия MMX команд), если на первом будет запущена программа, откомпилированная с учётом имеющихся на Pentium 2 аппаратных возможностей.

Несовместимость устройств и материнских плат

Конкретно взятая материнская плата, особенно персонального компьютера, также вносит свой вклад в несовместимость платформ. На современной материнской плате расположено множество встроенных (англ. integrated, интегрированных в плату) устройств, для которых, в отличие от определённых в дистрибутиве семейства операционных систем Windows NT восьми альтернативных (англ. Hardware abstraction layer, HAL) и мультиплатформенных драйверов для целых классов устройств, нужны специфические драйверы. Поэтому, при установке операционной системы Windows 9x или NT, она посредством установки драйверов специфического оборудования, «привязывается» к конкретной материнской плате. Последующий перенос операционной системы на другую материнскую плату сопряжен со сложностью обеспечения аппаратной совместимости новой аппаратной платформы.

Для решения этой проблемы в корпоративном сегменте, новая техника (материнская плата, периферийные устройства) проходит тщательную подгонку под существующий HAL, либо, если разрабатываемая линейка является революционной и перспективной, под неё создается новый HAL, согласованный со сторонними разработчиками программного и аппаратного обеспечения.

Кроссплатформенное программное обеспечение

Основная статья: Кроссплатформенное программное обеспечение

Запуск программного обеспечения на более чем одной аппаратной платформе и/или операционной системе является важной задачей, как для разработчиков новой аппаратуры, так и для программистов.

Debian компилирует свои пакеты для GNU/Linux для трёх архитектур процессоров Intel: IA-32 (x86-32), x86-64, IA64. Также официально создаются пакеты для ещё 8 аппаратных платформ. Пакеты, оптимизированные для конкретных процессоров своих платформ пользователи могут создать сами. Debian GNU/Hurd и GNU/kFreeBSD пока поддерживают меньшее количество платформ.

ОС NetBSD портирована на 60 аппаратных платформ (включающих в общей сложности 17 различных процессорных архитектур).

Microsoft разрабатывает специальные ветки своей операционной системы Microsoft Windows: Windows CE и Windows Embedded.

Запуск на различных архитектурах одного и того же прикладного программного обеспечения без необходимости обеспечивать совместимость на уровне ОС реализуется путём стандартизации языков, компиляторов, библиотек и среды исполнения (см., например, POSIX), а также путём перехода на исполнение ПО в виртуальной машине и стандартном окружении, которые реализуются для каждой платформы и гарантируют единообразное исполнение ПО независимо от платформы (см., например, Common Language Infrastructure и JVM).

Литература

Э.Таненбаум Архитектура компьютера = Structured Computer Organization. — 5-е изд.. — СПб.: Питер, 2007. — 848 с. — (Классика Computer Science). — ISBN 5-469-01274-3.

Барри Брэй Микропроцессоры Intel: 8086/8088, 80186/80188, 80286, 80386, 80486, Pentium, Pentium Pro Processor, Pentium 4. Архитектура, программирование и интерфейсы = The Intel Microprocessors 8086/8088, 80186/80188, 80286, 80386, 80486, Pentium, Pentium Pro Processor, Pentium 4. Architecture, Programming,and Interfacing. — Шестое издание. — СПб.: БХВ-Петербург, 2005. — 1328 с. — ISBN 5-94157-422-3.

Архитектура набора команд

Материал из Википедии — свободной энциклопедии

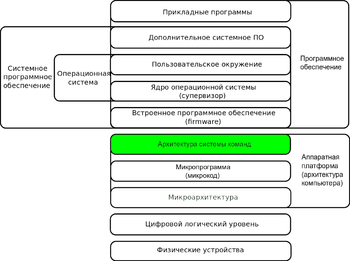

Схема, иллюстрирующая место уровней микроархитектуры, архитектуры набора команд и микрокода в многоуровневой структуре компьютера

Архитектура набора команд (англ. instruction set architecture, ISA) — часть архитектуры компьютера, определяющая программируемую часть ядра микропроцессора. На этом уровне определяются реализованные в микропроцессоре конкретного типа:

архитектура памяти,

взаимодействие с внешними устройствами ввода/ вывода,

режимы адресации,

регистры,

машинные команды,

различные типы внутренних данных (например, с плавающей запятой, целочисленные типы и т . д.),

обработчики прерываний и исключительных состояний.

Микроархитектура

Основная статья: Микроархитектура

Описывает модель, топологию и реализацию ISA на микросхеме микропроцессора. На этом уровне определяется:

конструкция и взаимосвязь основных блоков ЦП,

структура ядер, исполнительных устройств, АЛУ, а также их взаимодействия,

блоков предсказания переходов,

организация конвейеров,

организация кэш-памяти,

взаимодействие с внешними устройствами.

В рамках одного семейства микропроцессоров, микроархитектура со временем расширяется путем добавления новых усовершенствований и оптимизации существующих команд с целью повышения производительности, энергосбережения и функциональных возможностей микропроцессора. При этом сохраняется совместимость с предыдущей версией ISA.

Уровни, реализуемые в архитектуре, микроархитектуре и в семействе процессоров соответственно, а также их взаимосвязь описаны на рис. 1 в документе White Paper Inside Intel®Core™ Microarchitecture (англ.)

Содержание

1 Наборы команд на базе архитектуры Intel (IA)

2 Наборы команд на базе архитектуры AMD

3 См. также

4 Внешние ссылки

Наборы команд на базе архитектуры Intel (IA)

Корпорация Intel разработала три типа ISA, которые ориентируются на различные секторы рынка. Для их именования часто используется акроним из выражения Intel Architecture, IA (например, IA-32, IA-64).

Архитектура IA-32 предназначена для выполнения массовых 32-разрядных приложений на ПК начального уровня и реализована в следующих семействах процессоров:

Intel Celeron и Intel Pentium (в корпусе FC-PGA2);

процессорах Intel, использующих технологии ультранизкого напряжения питания;

Intel Core Duo.

Архитектура набора команд IA-64 реализована в семействе процессоров Intel Itanium.

Архитектура Intel 64 предназначена для современных ПК и серверов среднего уровня, оптимизированных для выполнения 64-разрядных приложений. Эта архитектура реализована в следующих семействах процессоров:

Intel Xeon;

Intel Core 2 Duo.

Наборы команд на базе архитектуры AMD

|

|

Этот раздел статьи ещё не написан. |

|

См. также

Микропроцессор

Цифровой сигнальный процессор

Архитектура компьютера

Микропрограмма

Система команд

Внешние ссылки Intel

Intel 64 and IA-32 Architectures Optimization Referance Manual (англ.)

Intel 64 and IA-32 Architectures Software Developer's Manual (в пяти томах):

Том 1. Basic Architecture (англ.)

Том 2A. Instruction Set Reference, A-M (англ.)

Том 2B: Instruction Set Reference, N-Z (англ.)

Том 3A. System Programming Guide (англ.)

Том 3B: System Programming Guide (англ.)

Главная страница поддержки процессоров (англ.)

Руководства по архитектурам Intel 64 и IA-32 (англ.)

AMD

|

[показать] |

Категории:

Технологии процессоров

Обработка команд

Архитектура компьютеров

Виртуальная машина (ВМ, от англ. virtual machine) —

программная и/или аппаратная система, эмулирующая аппаратное обеспечение некоторой платформы (target — целевая, или гостевая платформа) и исполняющая программы для target-платформы на host-платформе (host — хост-платформа, платформа-хозяин)

или виртуализирующая некоторую платформу и создающая на ней среды, изолирующие друг от друга программы и даже операционные системы (см.: песочница);

также спецификация некоторой вычислительной среды (например: «виртуальная машина языка программирования Си»).

Виртуальная машина исполняет некоторый машинно-независимый код (например, байт-код, шитый код, p-код) или машинный код реального процессора. Помимо процессора, ВМ может эмулировать работу как отдельных компонентов аппаратного обеспечения, так и целого реального компьютера (включая BIOS, оперативную память, жёсткий диск и другие периферийные устройства). В последнем случае в ВМ, как и на реальный компьютер, можно устанавливать операционные системы (например, Windows можно запускать в виртуальной машине под Linux или наоборот). На одном компьютере может функционировать несколько виртуальных машин (это может использоваться для имитации нескольких серверов на одном реальном сервере с целью оптимизации использования ресурсов сервера).

Содержание

1 Теория

2 Применение

3 Известные виртуальные машины

4 См. также

5 Примечания

6 Литература

7 Ссылки

Теория

Концепция виртуальной машины как совокупности ресурсов, которые эмулируют поведение реальной машины, появилась в Кембридже в конце 1960-х годов в виде расширения концепции виртуальной памяти манчестерской вычислительной машины Atlas[1]. В целом вычислительный процесс определяется в рамках этой концепции содержимым того рабочего пространства памяти, к которому он имеет доступ. При условии, что конкретная ситуация в этом рабочем пространстве соответствует ожидаемой, процесс не имеет никаких средств для определения того, является ли представленный ему ресурс действительно физическим ресурсом этого типа, или же он имитируется действиями других ресурсов, которые приводят к аналогичным изменениям содержимого рабочего пространства процесса.

Например, процесс не может определить, монопольно ли он использует процессор или же в режиме мультипрограммирования вместе с другими процессами. В виртуальной машине ни один процесс не может монопольно использовать никакой ресурс, и все системные ресурсы считаются ресурсами потенциально совместного использования. Кроме того, использование виртуальных машин обеспечивает развязку между несколькими пользователями, работающими в одной вычислительной системе, обеспечивая определённый уровень защиты данных.

Идея виртуальной машины лежит в основе целого ряда операционных систем, в частности, IBM VM/CMS (и её советского клона СВМ) и DEC VAX/VMS.

Применение

Виртуальные машины могут использоваться для:

защиты информации и ограничения возможностей программ (см.: песочница);

исследования производительности ПО или новой компьютерной архитектуры;

эмуляции различных архитектур (например, эмулятор игровой приставки);

оптимизации использования ресурсов мейнфреймов и прочих мощных компьютеров (см., например: IBM eServer);

вредоносного кода для управления инфицированной системой: вирус PMBS, обнаруженный в 1993 году, а также руткит SubVirt, созданный в 2006 году в Microsoft Research, создавали виртуальную систему, которой ограничивался пользователь и все защитные программы (антивирусы и прочие).[2]

моделирования информационных систем с клиент-серверной архитектурой на одной ЭВМ (эмуляция компьютерной сети с помощью нескольких виртуальных машин).

упрощения управления кластерами — виртуальные машины могут просто мигрировать с одной физической машины на другую во время работы.

тестирования и отладки системного программного обеспечения;

Известные виртуальные машины

Некоторые известные виртуальные машины:

|

Среды языков программирования

|

Операционные системы и гипервизоры

|

Автономные эмуляторы компьютеров

|

См. также

Сравнение виртуальных машин

Low Level Virtual Machine

ссылки

Программная модель IA-32 miu.by/rus/kaf_fis/kaf_download/21317_115157518.pdf

X86 — Lurkmore lurkmore.to/X86

http://www.intuit.ru/studies/courses/92/92/lecture/2777

Организация вычислительных систем

| Скачать электронную книгу

|

Поделиться

|

|

Лекция 2:

Архитектура 16-битных микропроцессоров семейства Intel IA-32

Аннотация: В этой лекции анализируется базовая архитектура процессора 8086: основные регистры, адресация памяти, режимы работы и ее развитие в процессоре 80286. Цель: познакомить учащихся с архитектурными особенностями и режимами работы 16-битных процессоров фирмы Intel, сформировать знания о формировании адреса в разных режимах работы процессора.

Ключевые слова: проектная норма, FPU, программная модель, регистр, центральный процессор, SI, SP, сегмент, указатель, IP, адрес, базово-индексная адресация, SCA, адресное пространство, выборка, процессор, прямой доступ, байт, константы, указатель команд, флаг состояния, дескрипторная таблица, таблица векторов прерываний, MSW, защищенный режим, селектор, режим реального адреса, сенмент, дескриптор

Анализ развития процессоров фирмы Intel IA-32

В табл. 2.1 приведены основные свойства процессоров фирмы Intel, от процессора 8086 до первых представителей семейства Pentium.

|

Таблица 2.1. Основные свойства процессоров фирмы Intel | |||||||

|

Тип ЦП Свойства |

8086 |

8088 |

80286 |

80386 |

80486 |

Pentium |

P6 |

|

1. Год выпуска |

1978 |

1979 |

1982 |

1985 |

1989 |

1993 |

1995 |

|

2. Проектные нормы (мкм) |

3 |

3 |

1,5 |

1 |

1-0,8 |

0,8-0,6 |

0,6-0,35 |

|

3. Количество транзисторов |

29000 |

29000 |

130000 |

275000 |

1млн 200т |

3млн 100т |

9млн 500т |

|

4. Разрядность ШД/ША |

16/20 |

8/20 |

16/24 |

32/32 |

32/32 |

64/32 |

64/32 (36) |

|

5. Максимальный объем физ. памяти |

1 Мб |

1 Мб |

16 Мб |

4 Гб |

4 Гб |

4 Гб |

4 Гб (64 Гб) |

|

6. Максимальный объем виртуальной памяти |

1 Мб |

1 Мб |

1 Гб |

64 Тб |

64 Тб |

64 Тб |

64 Тб |

|

7. Максимальный размер сегмента |

64 Кб |

64 Кб |

64 Кб/4 Гб |

64 Кб/4 Гб |

64 Кб/4 Гб |

64 Кб/4 Гб |

64 Кб/4 Гб |

|

8. Размер очереди предвыборки (байт) |

6 |

6 |

16 |

32 |

32 |

32 |

32 |

|

9. Размер операндов (бит) |

8, 16 |

8, 16 |

8, 16 |

8, 16, 32 |

8, 16, 32, 64 |

8, 16, 32, 64 |

8, 16, 32, 64 |

|

10. Размер регистров (бит) |

8, 16 |

8, 16 |

8, 16 |

8, 16, 32 |

8, 16, 32 |

8, 16, 32 |

8, 16, 32 |

|

11. Разбиение на страницы |

Нет |

Нет |

Нет |

Есть |

Есть |

Есть |

Есть |

|

12. Рабочая частота (МГЦ) |

5, 8, 10 |

5, 8, 10 |

8, 10, 12, 16 |

20, 25,33, 40 |

25-133 |

60-233 |

166, 180, 200 |

|

13. Защита памяти |

Нет |

Нет |

Есть |

Есть |

Есть |

Есть |

Есть |

|

14. Сопроцессор |

8087 |

8087 |

80287 |

80287, 80387 |

FPU |

FPU |

FPU |

Архитектура ЦП 8086: основные регистры, организация памяти

Программная модель МП представляется набором его регистров. Регистр является устройством временного хранения данных и используется с целью облегчения арифметических, логических и пересылочных операций.

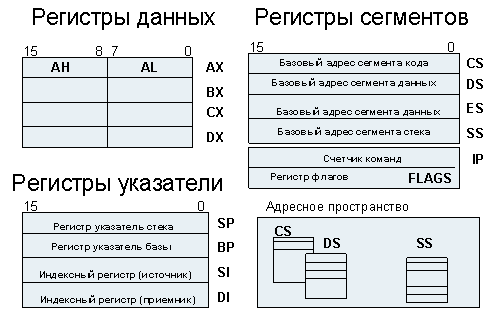

Центральный процессор 8086 имеет четыре 16-битных регистра общего назначения AX, BX, CX, DX, четыре регистра-указателя SI, DI, BP и SP, четыре регистра сегментов CS, DS, ES, SS, один 16-битовый регистр флагов FLAGS и указатель программ IP (см. рис.2.1)

Рис. 2.1. Программная модель ЦП 8086

Регистр-аккумулятор AX используется для хранения промежуточных данных и результатов.

При базовых типах адресации регистр BX содержит адрес области памяти либо адрес, который суммируется для получения нового значения со смещением.

Регистр-счетчик CX предназначен для управления числом итераций в цикле или числом повторений в командах REP в строковых операциях.

Регистр данных DX используется как вторичный аккумулятор для хранения промежуточных данных и результатов.

Индексный регистр-источник SI применяется в качестве указателя адреса байта или слова в таких строковых командах, как LODS ("загрузить строку"), CMPS ("сравнить строку"), MOVS ("переслать строку"). При базово-индексной адресации содержимое регистра SI может суммироваться с содержимым регистра BX.

Индексный регистр-приемник DI используется как указатель назначения для адреса байта или слова в строковых командах, таких как SCAS (сканировать строку), CMPS, MOVS, STOS (записать строку). При базово-индексной адресации для получения адреса операнда содержимое регистра DI может суммироваться с содержимым регистра BX.

Регистр-указатель стека SP применяется для работы с данными в стековых структурах. Его содержимое указывает адрес элемента на вершине стека, что удобно при организации обработки прерываний, процедур вызова подпрограммы и выхода из нее путем сохранения адреса возврата на вершине стека.

Регистр-указатель базы BP используется как дополнительный указатель для работы с данными в стековых структурах. В режиме базово-индексной адресации содержимое регистра BP может суммироваться с содержимым регистров SI или DI.

Адресное пространство памяти процессора, откуда происходит выборка команд и данных, разделено на сегменты (области памяти) емкостью до 64 Кбайт каждый. Процессор 8086 имеет прямой доступ одновременно к четырем сегментам.

Начальный адрес сегмента может быть установлен прикладной программой и всегда должен начинаться с 16-байтовых границ. Базовый адрес сегмента получается делением действительного физического адреса начальной ячейки сегмента на 16. Базовые адреса содержатся в одном из четырех 16-битных сегментных регистров CS, DS, ES и SS. На расположение сегмента не накладывается никаких специальных ограничений, кроме одного: он должен быть на границе 16 байт (т.е. физический адрес начальной ячейки должен делиться на 16). Сегменты могут быть смежными, разделенными, перекрываться частично или полностью.

Регистры сегментов используются для идентификации текущего сегмента адресного пространства.

Регистр сегмента команд CS указывает сегмент, содержащий адрес текущей выполняемой программы.

Регистр сегмента данных DS содержит начало зоны адресов, которая в общем случае включает программно изменяемые таблицы и константы.

Регистр дополнительного сегмента ES указывает начало области памяти, которая обычно используется для запоминания промежуточных данных.

Регистр сегмента стека SS содержит начальный адрес стековой структуры в памяти ЭВМ.

Указатель команд IP содержит адрес следующей команды в сегменте памяти, определяемом содержимым регистра сегмента команд CS.

Регистр флагов FLAGS содержит информацию о текущем состоянии микропроцессора. Имеет шесть однобитовых флагов состояния, которые индицируют результаты выполнения арифметических и логических операций.

Архитектура ЦП 80286: основные регистры, режимы работы, адресация памяти

Программная модель процессора 80286 включает 14 регистров ЦП 8086, пять новых регистров:

GDTR - 40-разрядный регистр определяет размер и положение глобальной дескрипторной таблицы ;

LDTR - 16-разрядный регистр определяет базовый адрес локальной дескрипторной таблицы ;

IDTR - 40-разрядный регистр определяет начало и размер таблицы векторов прерываний;

MSW - слово состояния программы (, если флаг PE = 1 в MSW, то процессор переключается в защищенный режим ).;

TR - 16-разрядный регистр содержит селектор сегмента состояния задачи, используется для многозадачности,

и шесть программно недоступных регистров, связанных с CS, DS, ES, SS, GDTR, IDTR.

Режимы работы

С появлением Intel-286 впервые стали говорить о различных режимах работы IA-32. Это первый представитель данного семейства микропроцессоров, в котором были реализованы многозадачность и защищенная архитектура. Чтобы обеспечить совместимость с предыдущими представителями этого семейства (8086/88, 80186/188), в Intel-286 было реализовано два режима функционирования: режим реального адреса (режим эмуляции 8086) и защищенный режим, в котором используются все возможности МП. В последующих поколениях МП этого семейства защищенный режим становится основным режимом работы.

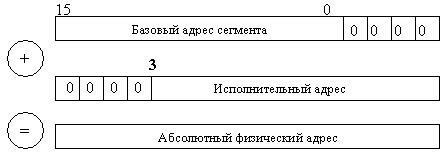

Формирование линейного адреса без участия селекторов

В режиме реального адреса используется упрощенная схема формирования линейного адреса.

В этом случае базовый адрес сегмента берется из сегментного регистра. Значение в сегментном регистре представляет собой биты 4-19 базового адреса сегмента. Из этого следует, что сегменты в этих режимах выровнены по 16-битной границе и все сегменты начинаются в пределах нижнего мегабайта линейного адресного пространства. Действительный физический адрес получается умножением на 16 базового адреса сегмента (рис. 2.2). Предел для всех сегментов одинаков. В режиме реального адреса предел сегмента - 64 Кбайт.

Рис. 2.2. Формирование физического адреса в реальном режиме

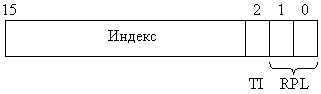

Формирование линейного адреса в защищенном режиме

Значения, помещаемые в сегментные регистры, называются селекторами. Селектор содержит индекс дескриптора, определяющий номер записи в дескрипторной таблице, бит TI, указывающий, к какой дескрипторной таблице производится обращение LDT (TI = 1) или GDT (TI = 0), а также запрашиваемые права доступа к сегменту - RPL (рис. 2.3.).

Рис. 2.3. Структура селектора

По указанному в селекторе номеру записи в соответствующей (бит TI селектора ) дескрипторной таблице определяется дескриптор сегмента.

Дескриптор - это 8-байтная единица описательной информации, распознаваемая устройством управления памятью в защищенном режиме, хранящаяся в дескрипторной таблице.

Дескриптор сегмента содержит базовый адрес описываемого сегмента, предел (размер) сегмента и права доступа к сегменту. В защищенном режиме сегменты могут начинаться с любого линейного адреса.

Для определения физического адреса базовый адрес сегмента суммируется со смещением.

Существуют две обязательных дескрипторных таблицы - глобальная (GDT) и дескрипторная таблица прерывания (IDT), - а также множество (до 8192) локальных дескрипторных таблиц (LDT), из которых в один момент времени процессору доступна только одна. Расположение дескрипторных таблиц определяется регистрами процессора GDTR, IDTR, LDTR.

Регистры GDTR и IDTR - содержат базовый адрес и предел дескрипторной таблицы.

Программно доступная часть регистра LDTR - 16 бит, которые являются селектором LDT. Дескрипторы LDT находятся в GDT. Однако, чтобы не обращаться каждый раз к GDT, в процессоре имеется теневая (программно недоступная) часть регистра LDTR, в которую процессор помещает дескриптор LDT при каждой перегрузке селектора в регистре LDTR.

Вопросы

Какие устройства составляют системное ядро ПК?

При инициализации ПК информация о проверке каких устройств выводится на экран дисплея?

С какого процессора семейства х86 количественные изменения в архитектуре кристалла перешли в качественные?

Какими регистрами дополнилась программная модель ЦП 80286?

Что такое селектор? С чем связано его появление? Какова структура селектора?

Как формируется линейный адрес в режиме реальных адресов и в режиме системного управления?

Что такое дескриптор? Какова структура дескриптора?

Как формируется линейный адрес в защищенном режиме?

Что находится в регистрах GDTR, IDTR и LDTR?

Каково содержимое регистра TR? Для чего он нужен?

Лекция 3:

Архитектура 32-битных микропроцессоров семейства Intel ia-32. Часть 1

Аннотация: В данной части лекции рассматривается базовая структура микропроцессоров IA-32: программная модель, основные регистры и формат команд. Цель: познакомить учащихся с программной моделью IA-32, сформировать знания о некоторых архитектурных особенностях микропроцессоров IA-32.

Ключевые слова: IA-32,драйвер,мультиплексор,интерфейс,цикла,режим пакетирования,адрес,конвейеризация,функция,FIFO,First,очередь,операции,производительность,суперскалярность,pentium pro,сложение,вычисление,регистр,интеграция,point,вещественная арифметика,MMX,FPU,SIMD,инструкция,XMM,SSE,устройство управления памятью,кэш,память,компонент,страничное преобразование,физический адрес,трансляция,информация,пространство,рестарт,кэш данных,программная модель,указатель команд,регистр управления,бит,битовые поля,ESI,EDI,ebps,ESP,доступ,SI,SP,AH,указатель,значение,предел,сегментный регистр,дескрипторная таблица,логический адрес,EIP,FAR,far call,int,IRET,стек,байт,программа,время выполнения команды,MOV,немаскируемое прерывание,сегменты,call,RET,слово,флаг состояния,регистр флагов,защищенный режим,LDT,IDT,LTR,SIB,префикс,mod,режим адресации,дополнительный код,способ адресации,операнд,исключение,порт ввода-вывода,архитектура,процессор,адресация,EA

Структура микропроцессоров ia-32

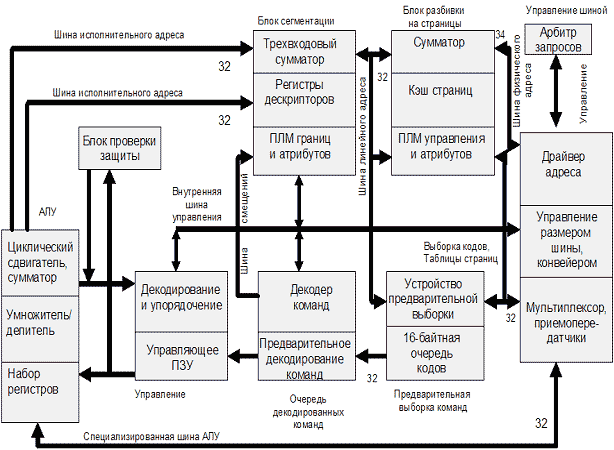

увеличить изображениеРис. 3.1. Структура микропроцессора Intel-386

Базовую структуру микропроцессоров (МП) IA-32 можно рассмотреть на примере Intel-386 (рис. 3.1). В структуре Intel-386 можно выделить шесть основных блоков, работающих параллельно: блок интерфейса с магистралью, блок предварительной выборки команд, блок декодирования команд, исполнительный блок, блок управления сегментами и блок страничной трансляции.

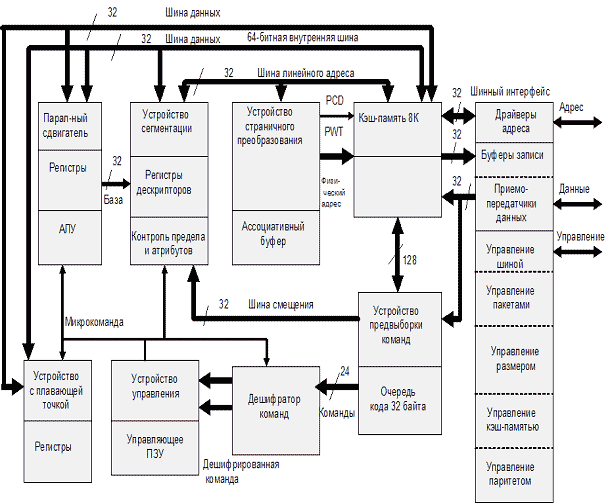

Блок интерфейса смагистралью содержит драйвер адреса, схемы управления размером адреса и конвейером, мультиплексор, приемопередатчики и др. Этот блок обеспечивает интерфейс между МП и его окружением. Он принимает внутренние запросы для выборки команд от блока предварительной выборки команд и для обмена данными с исполнительным блоком и устанавливает приоритет этих запросов. Одновременно он генерирует или обрабатывает сигналы для исполнения текущего цикла магистрали. К ним относятся сигналы адреса, данных и управления для обращения к внешней памяти и устройствам ввода-вывода. При помощи схемы арбитра запросов блок управляет интерфейсом с внешними задатчиками магистрали и сопроцессорами. В МП Intel-486 (рис. 3.2) этот блок был дополнен схемой управления паритетом (выравниванием) и схемой управления пакетами. На основе последней был реализован специальный режим работы магистрали - режим пакетирования. В этом режиме при передаче 4 слов на магистрали выставляется только адрес первого, что позволяет существенно сократить время обмена данными с оперативной памятью или внешним кэшем.

увеличить изображениеРис. 3.2. Структура микропроцессора Intel-486

|

Таблица 3.1. Порядок передачи 4 слов (64 бита) на системной магистрали | ||

|

Такт |

Конвейеризация Intel-286 |

Режим пакетирования Intel-486 |

|

1 |

Адрес 1 слова |

Адрес 1 слова |

|

2 |

Передача 1 слова |

--- |

|

3 |

Адрес 2 слова |

Передача 1 слова |

|

4 |

Передача 1 слова |

Передача 2 слова |

|

5 |

Адрес 3 слова |

Передача 3 слова |

|

6 |

Передача 1 слова |

Передача 4 слова |

|

7 |

Адрес 4 слова |

|

|

8 |

Передача 1 слова |

|

Для того чтобы заранее получать команды или данные перед их фактическим использованием, существует функция опережающего просмотра программы, которую в Intel-386 выполняет блок предвыборки команд. Когда блок интерфейса с магистралью не занимает цикла магистрали для исполнения команды, блок предвыборки команд использует его для последовательной выборки из памяти байтов команд. Эти команды хранятся в 16-байтовой очереди команд в ожидании обработки блоком декодирования команд.

Блок декодирования командпреобразует байты команды из этой очереди в микрокод. Декодированные команды в ожидании обработки исполнительным блоком хранятся в очереди команд, работающей по принципу FIFO (First In First Out). В Intel-386 эта очередь имеет размер 3 команды, а в Intel-486 - уже 5 команд, что позволяет этому МП при некоторых условиях выполнять по одной команде за цикл. Непосредственные данные и относительные адреса в коде операции также берутся из очереди команд.

Исполнительный блоквыполняет команды из очереди команд и взаимодействует со всеми другими блоками, нужными для завершения выполнения команды. Для ускорения выполнения команд с обращением к памяти исполнительный блок приступает к их исполнению до завершения выполнения предыдущей команды. Так как команды с обращением к памяти встречаются очень часто, то благодаря такому перекрытию по времени производительность повышается. В МП Pentium исполнительный блок реализован в виде двух параллельных конвейеров (u и v), что позволяет ему выполнять до двух команд за такт. Это архитектурное решение названо суперскалярностью. Оно получило дальнейшее развитие в МП подсемейства P6 (Pentium Pro, Pentium II, Pentium III), где исполнительный блок представлен уже тремя конвейерами. Особенностью конвейеров P6 является динамическое выполнение (предсказание ветвлений, спекулятивное выполнение, изменение последовательности команд).

В исполнительный блок встроены регистры общего назначения (РОН),которые используются для таких операций, как двоичное сложение или вычисление и модификация адресов. Исполнительный блок содержитвосемь 32-разрядныхРОНов, применяемых как для вычисления адресов, так и для операций с данными. Этот блок содержит также 64-разрядный регистр, необходимый для ускорения операций сдвига, циклического сдвига, умножения и деления.

Интеграция в МП i486DX блока вычислений с плавающей точкой (Floating Point Unit) резко повысила производительность вещественной арифметики. В МП Pentium MMX был добавлен набор команд, позволяющий использовать регистры блока FPU для параллельной обработки пакета целочисленных данных: SIMD - "одна инструкция - несколько операндов". В МП Pentium III эта технология была расширена, за счет добавленияем блока XMM, позволяющего параллельно обрабатывать пакет вещественных данных: SSE - потоковое расширение SIMD.

Блоки сегментации и страничнойтрансляции образуют устройство управления памятью.

Блок сегментации преобразует логические адреса в линейные по запросу исполнительного блока. Для ускорения этого преобразования текущие дескрипторы сегментов помещаются во встроенную кэш-память. Во время трансляции адресов блок управления сегментами проверяет, нет ли нарушения сегментации. Эти проверки выполняются отдельно от проверок нарушений статической сегментации, осуществляемых механизмом проверки защиты. Блок сегментации обеспечивает четыре уровня защиты (от 0 до 3) с целью изоляции и защиты друг от друга прикладных программ и операционной системы. Этот компонент также позволяет легко создавать перемещаемые программы и данные и обеспечивает их совместное использование. Полученный линейный адрес направляется в блок страничной трансляции.

Если механизм страничного преобразования включен, то для получения физических адресов по линейным используется блок страничной трансляции. Если же этот механизм выключен, то это означает, что, физический адрес совпадает с линейным, и трансляция не нужна. Для ускорения трансляции адресов в кэш-память дескрипторов страниц помещаются каталог недавно использованных страниц, а также информация о входах в таблицу страниц в буфере трансляции адресов. Затем блок страничной трансляции пересылает физические адреса в блок интерфейса с магистралью для выполнения цикла обращения к памяти или устройствам ввода-вывода. МП Intel-386 использует 32-разрядные регистры и шины данных для поддержки адресов и типов данных такой же разрядности.

Блок страничной трансляциипозволяет прозрачно управлять пространством физических адресов независимо от управления сегментами. Каждый сегмент отображается в пространство линейных адресов, которое, в свою очередь, отображается в одну или несколько страниц объемом 4 Кб. Для реализации эффективной системы виртуальной памяти Intel-386 полностью поддерживает способность рестарта (повторного запуска) в случае отказа во всех страницах и сегментах.

В МП 80486 был интегрирован кэш первого уровня размером 8 Кб. В МП Pentium размер кэша первого уровня удвоен: 8 Кб - кэш команд и 8 Кб - кэш данных. В МП Pentium Pro, кроме того, на кристалле интегрирован кэш второго уровня.

Лекция 3: Архитектура 32-битных микропроцессоров семейства Intel IA-32. Часть 1