- •Вступление

- •Основные задачи технической диагностики

- •Системы диагноза технического состояния

- •Диагностические системы управления

- •Объекты диагноза

- •Математические модели объектов диагноза

- •Функциональные схемы систем тестового и функционального диагноза

- •Методы и технические средства диагностирования элементов и устройств вычислительной техники и систем управления Общие сведения

- •Тестовое тестирование узлов, блоков и устройств.

- •Структуры автоматизированных систем.

- •Программное обеспечение процессов диагностирования.

- •Логические анализаторы.

- •Микропроцессорные анализаторы (ма).

- •Способы запуска.

- •Подключающие устройства.

- •Ввод начальных данных.

- •Проверка отдельных триггеров.

- •Проверка содержимого постоянных запоминающих устройств (пзу).

- •Проверка оперативных запоминающих устройств (озу).

- •Проверка работы линии коллективного пользования (лкп).

- •Проверка аналого-цифровых преобразователей (ацп).

- •Проверка печатных плат.

- •Проверка микропроцессорной системы.

- •Сигнатурные анализаторы

- •Процесс формирования сигнатур.

- •Аппаратурная реализация сигнатурного анализатора.

- •Тестовое диагностирование устройств в составе эвм.

- •Диагностирование оборудования процессоров.

- •Способы диагностирования периферийных устройств.

- •Диагностирование упу/пу с помощью процессора.

- •Проверки упу/пу с помощью диагностических приказов.

- •Диагностирование упу/пу с помощью тестеров.

- •Способы тестирования зу.

- •Принципы построения стандартных проверяющих тестов полупроводниковых зу.

- •Аппаратурные средства функционального диагностирования узлов и блоков. Основные принципы построения.

- •Кодовые методы контроля.

- •Контроль передач информации.

- •Контроль по запрещенным комбинациям.

- •Самопроверяемые схемы контроля.

- •Контроль по модулю

- •Организация аппаратурного контроля озу.

- •Организация аппаратурного контроля внешних зу.

- •Средства функционального диагностирования в составе эвм.

- •Контроль методом двойного или многократного счета

- •Экстраполяционная проверка

- •Контроль по методу усеченного алгоритма (алгоритмический контроль).

- •Способ подстановки.

- •Проверка предельных значений или метод "вилок".

- •Проверка с помощью дополнительных связей.

- •Метод избыточных переменных

- •Контроль методом обратного счета.

- •Метод избыточных цифр.

- •Метод контрольного суммирования.

- •Контроль методом счета записи.

- •Контроль по меткам

- •Метод обратной связи

- •Метод проверки наличия формальных признаков (синтаксический метод, метод шаблонов).

- •Метод проверки запрещенных комбинаций.

- •Метод an-кодов

- •Методы на основе циклических кодов и кодов Хэмминга и др.

- •Структурные методы обеспечения контролепригодности дискретных устройств.

- •Введение контрольных точек.

- •Размножение контактов.

- •Использование блокирующей логики.

- •Применение параллельных зависимых проверок

- •Замена одним элементом состояний группы элементов памяти.

- •Методы улучшения тестируемой бис. Сокращение числа тестовых входов.

- •Двухуровневое сканирование.

- •Микропроцессорные встроенные средства самотестирования.

- •Контроль и диагностирование эвм Характеристики систем диагностирования

- •Системы контроля в современных эвм

- •Применение аналоговых сигнатурных анализаторов

- •Работа локализатора неисправностей pfl780 в режиме "Pin by Pin"

- •Работа в режиме Pin by Pin

- •Работа с торцевыми разъемами

- •Среда тестирования

- •Индивидуальное тестирование или режим Pin by Pin?

- •Тестирование специальных устройств

- •Устранение ложных отказов путем использования эталонных сигнатур компонентов от разных производителей

- •Тестирование цифровых компонентов методом asa

- •Вариации сигнатур.

- •Входные цепи защиты

- •Набор альтернативных сигнатур

- •Тестирование подключенных к общей шине компонентов путем их изоляции специальными блокирующими напряжениями.

- •Системы с шинной архитектурой

- •Устройства с тремя логическими состояниями

- •Разрешение работы и блокирование компонентов

- •Применение "блокирующих" напряжений

- •Отключение тактовых импульсов.

- •Отключение шинных буферов.

- •Опция Loop until Pass

- •Локализация дефектных компонентов в системах с шинной архитектурой без их удаления из испытываемой цепи

- •Поиск неисправностей методами asa и ict в системах с шинной архитектурой

- •Сравнение шинных сигнатур

- •Шинные сигнатуры

- •Изоляция устройств.

- •Локализация коротких замыканий шины и неисправностей нагрузки прибором toneohm 950 в режиме расширенного обнаружения неисправностей шины

- •Типы шинных неисправностей

- •Короткие замыкания с низким сопротивлением

- •Измерение протекающего через дорожку тока.

- •Измерение напряжения на дорожке печатной платы

- •Обнаружение кз и чрезмерных токов нагрузки в труднодоступных для тестирования местах

- •Короткие замыкания на платах

- •Обнаружение сложных неисправностей тестируемой платы путем сравнения импедансных характеристик в режиме asa

- •Импедансные сигнатуры

- •Локализация неисправностей методом Аналогового сигнатурного анализа

- •Методы сравнения

- •Основы jtag Boundary Scan архитектуры

- •АрхитектураBoundaryScan

- •Обязательные инструкции

- •Как происходитBoundaryScanтест

- •Простой тест на уровне платы

- •Граф состояний тар – контроллера

- •Мониторинг сети Управление сетью

- •Предупреждение проблем с помощью планирования

- •Утилиты мониторинга сети

- •Специальные средства диагностики сети

- •Источники информации по поддержке сети

- •Искусство диагностики локальных сетей

- •Организация процесса диагностики сети

- •Методика упреждающей диагностики сети

- •Диагностика локальных сетей и Интернет Диагностика локальных сетей

- •Ifconfig le0

- •Сетевая диагностика с применением протокола snmp

- •Диагностика на базеIcmp

- •Применение 6-го режима сетевого адаптера для целей диагностики

- •Причины циклов пакетов и осцилляции маршрутов

- •Конфигурирование сетевых систем

- •Методы тестирования оптических кабелей для локальных сетей.

- •Многомодовый в сравнении с одномодовым

- •Нахождение разрывов

- •Измерение потери мощности

- •Использование тестовOtdRдля одномодовых приложений

- •Источники

- •Словарь терминов а

Основы jtag Boundary Scan архитектуры

Исторически большинство печатных плат тестировались с использованием аппаратуры, непосредственно подключаемой к проверяемым цепям с помощью различных приспособлений (в частности, «щупов»). Однако современные достижения в области микроэлектроники ставят перед производителями несколько проблем: высокотехнологичные микропроцессорные и специализированные устройства имеют огромное число контрольных точек, причем большая их часть находится непосредственно в корпусе микросхемы, а устройства для их проверки необходимо изготавливать узко специализированными, что непомерно дорого.

В 1985 году группа европейских компаний сформировала специальную организацию, занимающуюся вопросами тестирования - JETAG (Joint European Test Action Group), призванную решить эту проблему. Ее целю было создание единой аппаратной базы тестинга, контролируемой программным образом, исключающей применение сложной и дорогой специализированной аппаратуры тестирования. В 1988 году произошло дальнейшее развитие организации, превратившейся в JTAG (Joint Test Action Group). Результатом ее работы стало принятие в 1991 году Institute of Electrical and Electronic Engineers (IEEE) стандарта IEEE 1149.1, известного как стандарт Test Access Port and Boundary Scan Architecture.

АрхитектураBoundaryScan

Архитектура Boundary Scan позволяет проводить полное тестирование и обзор компонентов, совместимых со спецификацией JTAG, без использования специальных устройств, подключаемых к плате. Контроль и диагностика осуществляются программным путем, так как каждое устройство (микросхема) снабжены собственными схемами тестирования, выдающими результат внутренней проверки через стандартные шины.

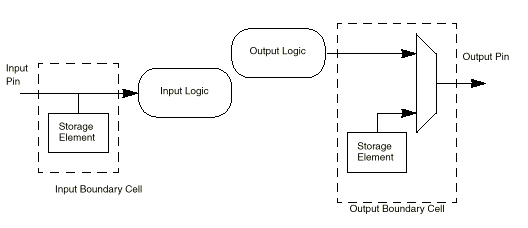

Рис. 1 Входные и выходные структуры для Boundary Scan устройств.

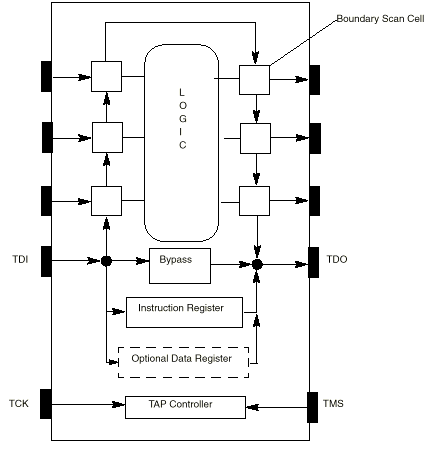

На рис.1 изображена возможная структура для входных и выходных ножек JTAG – совместимых устройств. Во время стандартных операций boundary – соты не активны и данные проходят обычным образом через элемент. Во время режима тестирования все входные сигналы сохраняются для анализа, а все выходные сигналы устанавливаются таким образом, чтобы организовать процесс тестирования для последующих устройств. Функционирование таких сканирующих сот контролируется через Test Acsess Port (TAP) контроллер с использованием регистра инструкций, как показано на рис.2.

Рис.

2. Устройство (микросхема), поддерживающая

Boundary

Scan.

Рис.

2. Устройство (микросхема), поддерживающая

Boundary

Scan.

ТАР – контроллер – это устройство (может находиться в одном из 16 состояний), контролирующее операции связанных архитектурой Boundary Scan сот. Основные операции контролируются через четыре вывода: Test Clock (TCK) – частота синхронизации теста, Test Mode Select (TMS) – выбор режима тестирования, Test Data In (TDI) – вход тестовых данных, и Test Data Out (TDO) – выход тестовых данных.

Входы TCK и TMS определяют переходы ТАР – контроллера в различные состояния. Выводы TDI и TDO определяют тестовые данные для сканируемой цепочки. Еще может использоваться пятый вывод, TRST, для асинхронного сброса ТАР – контроллера.