3.2 Зу мпс

Основной частью ОЗУ является элемент памяти, который хранит 1 байт информации, элемент памяти, в котором замещается n-разрядное слово, называется ячейкой памяти. При этом величинаnопределяет разрядность ячейки, каждая ячейка памяти имеет свой адрес.

Кол-во ячеек памяти равняется 2 в сепени m- кол-во адресных входов, а информационная емкость. Большиннство ляля имеют словарную организацию, т.е. предполагают переальльное сичтывагние ляляля

Для считывании информации из ячейки необходимо на адресные входы мискросхемы ПЗУ подать разряды кода адреса (А0---А13) которые выбираеют соответствующую ячейку в ПЗУ. Считывание информации происходит при активном (нулевом) уровне сигнала CS. ПриCS, равном 1, выходыd7-d0 нахордятся в 3-ем (высокоимпендансном)zсостоянии. Если ЗУ имеет выходы с 3-мя состояниями, или с открытым коллекторм, то выход БИС ПЗУ может быть соединен непосредственнос шиной.

По способу программирования, т.е. способу заненсения иснформвации в ЗУ различают след типы ПХУ:

массочные, однократно программируемые

многократно программируемые с ультрапро

многократно программируемые с электрическим стиранием

Флеш-память

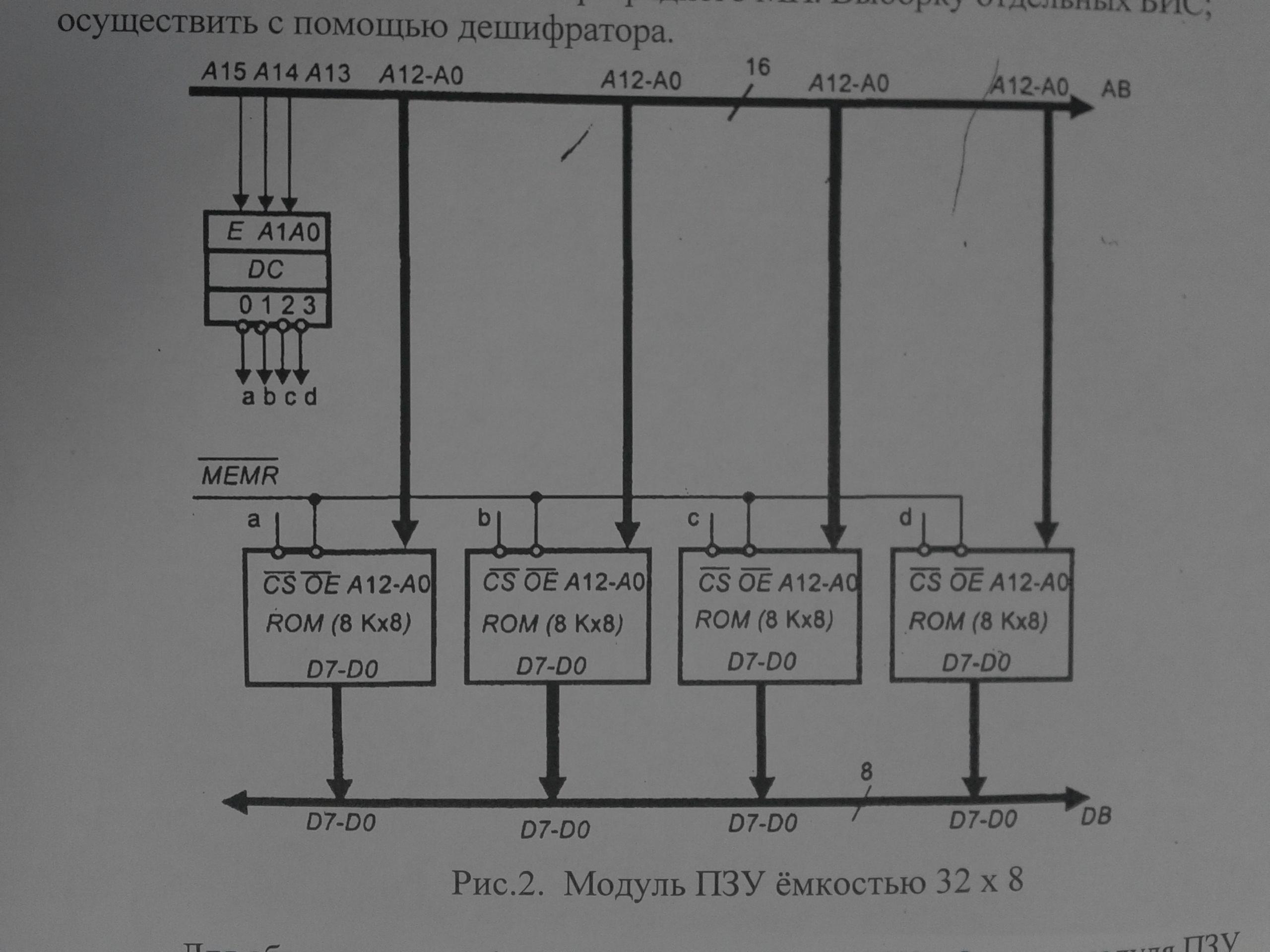

Рассмотрим принципиальную схему модуля ПЗУ с организацией 32 k*8 и начальным адресом 8000hна базе БИСK573RF6. модуль ПЗУ СОЕДИНЕН с системной шиной с 8-разрядной МПС. Выборка отдельных БИС осуществляется с помощью дешифратора.

Поскольку модуль памяти содержит 4 БИС ПЗУ, для выбрки кажой из низ используется дешифратор DCс 4-мя выходамиABCD. При нулевом значенииa15 выбобка не осуществляется, поэтому значение сигналов дешифратора являются единичнымиA=B=C=D=1. При подаче на вход Е нулевого значения А15 ни одна БИС ПЗУ не выбирается. Для адресации 4-х БИС ПЗУ, при фиксированным значении старшего разряда А15 необходимо использовать еще 2 адресных разряда. Для этого используеют разряды А14 и А15, которые поступают на адресные входы дешифратора А1 и А0. Для обеспечению информационной емкости 32k*8, схема модуля ПЗУ должна содержать 4 БИС ПЗУ емкостью 8k*8.

|

А15 |

А14 |

А13 |

a |

b |

c |

D |

|

0 |

X |

X |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

0 |

1 |

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

1 |

0 |

Младшие адреса подаются на адресные входы А12-А0 всех БИС ПЗУ и параллельно адресуют ячейку внутри одной БИС. 2 старших разряда А14 и А13 через дешифратор DCвыбирают одну из 4 БИС ПЗУ. Выходы БИСD7-D0соединены с ШД МПС.

17.03.12

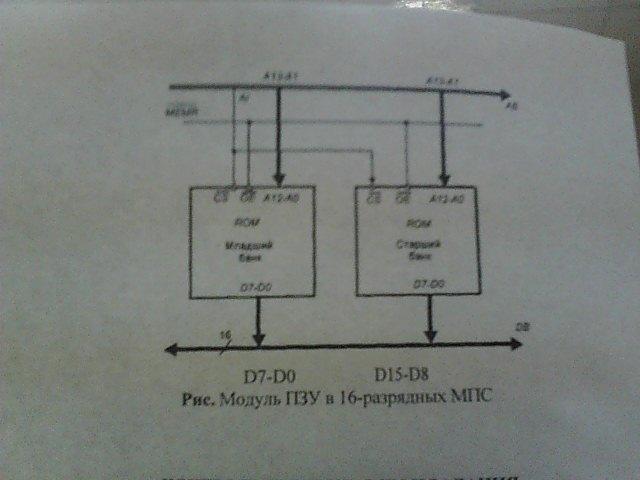

Построение модуля ПЗУ 16-разрядной МПС.

16-разрядная МПС должна оперирровать как с 8, так и с 16-разрядными ячейками памяти. Для использования 8 разпядных БИС модулей памяти 16-разрядных процессорова, например с информауионной емкостью 1мб, постоянная память выполняется в виде 2-х банков, по 512 кб каждый.

Один из банков соединяется с младшой половины шины данных (D7-D0) и называется младшим, второй - со старшей половины ШД, разрядыD15-D8 и называется старшим. Младший байт содержит адреса с четными адресами, а старший с нечетными. Для адресации внутри банка используются адресные разряды А19-А1. Считывание из ПЗУ организовано таким образом, что при обращении к ПЗУ на шину данных всегда поступают два байта, т.е. считывается в содержимое обоих банков одновременно. В случае необходимости процессор может выбрать 1 нужный байт из 2-х.

Каждый их банков выполнен по структурной схеме модуля ПЗУ, рассмотренной выше. В МПС с 32-разрядной ШД модуль ПЗУ выполняется в виде 4-х банков, информация, считывается одновременно со всех 4-хбанков, после чего МП выбирает одно, 2-х или 4-х байтное слово, в зависимости от выполняемой комангды.

3.3. ОЗУ статического типа. Элементом памяти -триггер. Для того, чтобы считать информацию из ячейки памяти илии записать в нее новое значение, ее необходимо выбрать подачей на БИС ОЗУ соответствующего адреса. Часть адресоных разрядов поступают на дешифратор строк, а часть на DCстолбцов, определяет таким образом положение ячейки памяти в матрице накопителя. ЗУ предполагает обращение к любой ячейке памяти в произвольном порядке. Такое ОЗУ называют ОСУ с произвольной выборкой. Существует ОЗУ с информационной емкостью 2 в стемениm* 1бит. (К541, К132). И емкостью 2 в степениm*8 (К541). Для ввода информации в ОЗУ 1-ого типа используют входDI, а для вывода выходDO. БИС ОЗУ 2-ого типа имеютnинфомационных входов-выходов и предполгают чтение-запись 8-разрядного кода. Управление режимами (запись, чтение, хранение) осуществляется с помощью сигналаCSиW\R. Высокий уровень сигнала поределяет режим записи информации в память, низкий уровень - режим считывания информации из записи.

3.4 ОЗУ динамического типа.

В микросхемах Дин типа элементом является емкость PnпереходаMDPтранзистора (микроконденсатор). Заряженное состояние конденсатора считается состоянием логической 1-цы, разряженное состоянием логического 0-ля. Такие элементы памяти не могут продолжительное время сохранять свое состояние, и поэтому требуют дополнительных средств для периодического восстановления (регенерации) информации. Время выборки для динамического ОЗУ составляет 70-200 нс. По сравнению с ОЗУ статического типа ОЗУ динамического типа характеризуются:

большей информационной емкостью, обусловленной меньшим числом транзистров в одном элементе памяти;

меньшим быстродействием (из-за необходимости разряда и заряда конденсатора при записи бита информации.

меньшей мощностью поребления

меньшей стоимостью, что приятно

Для обеспечения адресации сравнительно большой емкости динамической памяти используют мультипрексирования адресных сигналов во времени. Сначала на БИС ОЗУ подают m-младших разрядов ША, сопровождаемые строгомRAS, затемm- старших, сопровождаемые сигналомCAS, строк адреса столбца. Мультиплексирование адресных симий во времени позволяет уменьшить число выводов БИС ОЗУ для адреса в 2 раза. Для БИС К565РУ7 с помощью 8 адресных диний (А7-А0) передаются данные, адесация которых требуют 16-адресных линий. Эта БИС имеет информационную емкость 64к*1 и 2 вывода,yfrjnjhstgjcnegf.ncbuyfkscnhj,jdRasbCAS.

Оперативные зу динамического типа работают в режимах записи, считывания, регенерации.