Отчетик

.docxМинистерство образования и науки Российской Федерации

ФГБОУ ВПО

«Магнитогорский Государственный Технический Университет им. Г.И. Носова»

Кафедра электротехники и электротехнических систем

Расчетно-графическая работа №1

Задача №2

Вариант №5

Выполнил: студент группы АВ-09-1

Сичная Мария

Проверил: профессор

Мугалимов Р.Г.

Магнитогорск 2011

«Исследование одноразрядного сумматора и 2-разрядного параллельного сумматора-вычитателя»

Ход работы:

-

Изучить алгоритм сложения и вычитания двоичных чисел. На основе алгоритма составить таблицу истинности полного одноразрядного сумматора. Из таблицы истинности сумматора записать булевы уравнения для сигнала суммы и сигнала переноса полного одноразрядного сумматора.

-

Применяя карту Карно, выполнить минимизацию логического уравнения сумматора. По минимизированным уравнениям составить логическую схему полного одноразрядного сумматора. Исследовать полный одноразрядный сумматор на правильность функционирования. Для этого логическую схему дополнить генератором двоичных слов и анализаторов двоичных сигналов. Снять осциллограмму выходных сигналов сумматора. Проанализировать полученные осциллограммы и составить по ним таблицы истинности. Сравнить первую и полученную таблицы. Сделать выводы.

-

На основе разработанного полного одноразрядного сумматора составить логическую схему 2-разрядного параллельного сумматора. Проверить правильность функционирования 2-разрядного параллельного сумматора.

-

Разработанный 2-разрядный паралелльный сумматор доработать до 2-разрядного параллельного сумматора-вычитателя. Проверить правильность функционирования.

-

Сделать выводы по расчетно-графической работе.

Выполнение работы:

-

Таблица истинности полного одноразрядного сумматора выглядит так:

|

№ п/п |

Вход |

Выход |

||||

|

pi-1 |

b |

a |

&i |

pi |

||

|

0 |

0 |

0 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

1 |

1 |

0 |

|

|

2 |

0 |

1 |

0 |

1 |

0 |

|

|

3 |

0 |

1 |

1 |

0 |

1 |

|

Булево уравнение для сигнала суммы:

.

.

Булево уравнение для сигнала переноса:

.

.

-

Применим карту Карно для того, чтобы минимизировать уравнение для сигнала суммы:

|

|

|

|

|

|

|

|

0 |

1 |

0 |

1 |

|

|

1 |

0 |

1 |

0 |

Как видно на карте, минимизировать функцию не удалось.

Применяем карту Карно, чтобы минимизировать уравнение для сигнала перноса:

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

|

|

0 |

1 |

1 |

1 |

Получили минимизированную функцию:

.

.

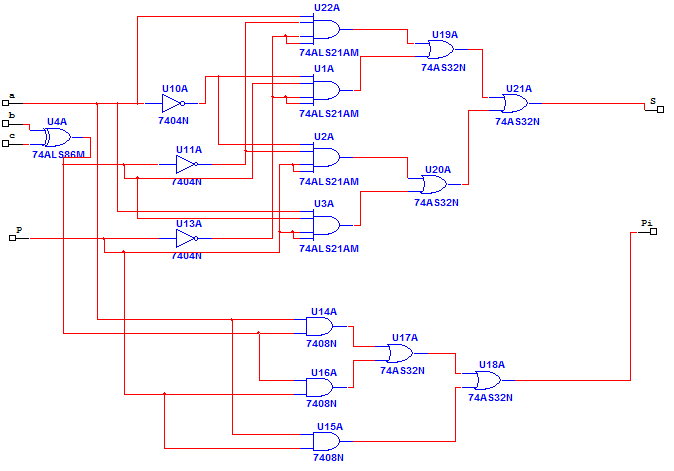

По получившимся уравнениям составляем логическую схему полного одноразрядного сумматора в программе Multisim.

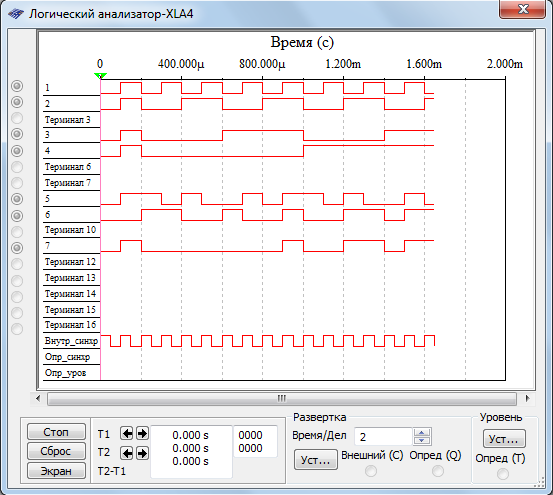

Проверяем правильность функционирования полного одноразрядного сумматора с помощью осциллограммы.

По полученной осциллограмме не трудно составить таблицу истинности:

|

№ п/п |

Вход |

Выход |

||||

|

pi-1 |

b |

a |

&i |

pi |

||

|

0 |

0 |

0 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

1 |

1 |

0 |

|

|

2 |

0 |

1 |

0 |

1 |

0 |

|

|

3 |

0 |

1 |

1 |

0 |

1 |

|

Так как таблицы истинности получились одинаковые, можно утверждать, что сумматор был составлен верно.

-

Для того, чтобы построить 2-разрядный параллельный сумматор, необходимо построить отдельные компоненты этого сумматора.

Построим компонент «сумматор». Его логическая схема в программе Multisim выглядит так:

Построим компонент «формирователь сигнала переноса». Его логическая схема в программе Multisim выглядит так:

После того, как компоненты 2-разрядного параллельного сумматора определены, можно построить его логическую схему в программе Multisim:

Осциллограмма выглядит так:

По данной осциллограмме можно построить таблицу истинности:

|

№ п/п |

Входы |

Выходы |

||||||

|

a1 |

a2 |

b1 |

b2 |

&1 |

&2 |

p |

||

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

|

2 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

|

3 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

|

|

4 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

|

|

5 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

|

|

6 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

|

|

7 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

|

|

8 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

|

|

9 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

|

10 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

|

|

11 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

|

|

12 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

|

|

13 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

|

|

14 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

|

|

15 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

|

-

Для выполнения действия сложения или вычитания используется сумматор–вычитатель.

Вычитаемое двоичное число преобразуется из прямого кода в дополнительный код, при этом уменьшаемое число остается в прямом коде.

Коды уменьшаемого вычитаемого в дополнительном коде подаются на информационные входы сумматора. Код разности снимается с выхода сумматора. В логической схеме прямой код с помощью логического элемента исключающее ИЛИ.

Логическая схема компонента «сумматор» в программе Multisim:

Логическая схема двуразрядного параллельного сумматора-вычитателя в программе Multisim:

Осциллограмма сумматора-вычитателя в режиме сумматора:

Осциллограмма сумматора-вычитателя в режиме вычитателя:

-

В ходе лабораторной работы были составлены таблица истинности и булевы уравнения полного одноразрядного сумматора. Также изучены логические схемы полного одноразрядного сумматора и сумматора–вычитателя, двуразрядного параллельного сумматора и двуразрядного параллельного сумматора-вычитателя.